Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,241 - 2,260 / 2,405

抵抗変化層をストレージノードとして備えるメモリ素子の製造方法

【課題】抵抗変化層をストレージノードとして備えるメモリ素子の単位セル面積を4F2未満に減らせるメモリ素子の製造方法を提供する。

【解決手段】下部膜上に半導体層44a、46,48、抵抗変化層50及び第1物質層を順次積層し、第1物質層に抵抗変化層50が露出されるストライプ状の第1ホールを形成し、第2物質層で第1ホールの側壁に第1スペーサ58aを形成し、第1ホールを、第1スペーサ58aを覆う第3物質層で満たし、第1物質層を除去し、第1スペーサ58aの側面に第4物質層で第2スペーサ66aを形成し、第3物質層を除去し、第1スペーサ58a及び第2スペーサ66aをマスクとして使用して、抵抗変化層50を含む第2積層物に下部膜が露出されるストライプ状の第2ホール90を形成するメモリ素子の製造方法である。

(もっと読む)

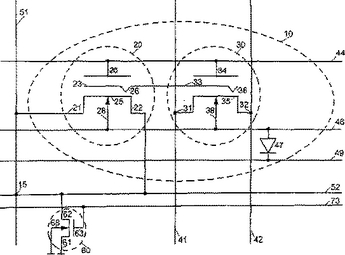

半導体メモリ素子及び半導体記憶装置

【課題】 情報を抵抗値の違いとして記憶することができ、且つトランジスタのコンダクタンス変化によって抵抗の変化を確実に読み出すことができ、低電圧動作と高集積化を可能にする。

【解決手段】 情報を抵抗値の違いとして記憶する半導体メモリ素子において、MISトランジスタ10と、MISトランジスタ10のゲートと第1の電源端との間に接続され、通電量又は通電方向によって抵抗値が変化し、且つ通電を停止しても変化した抵抗値が保持される2端子の抵抗変化素子20と、MISトランジスタ10のゲートと第2の電源端との間に接続された固定抵抗素子30とを備えた。

(もっと読む)

ジルコニウム酸化膜を有する半導体素子のキャパシタ及びその製造方法

【課題】70nm以下の金属配線を有する次世代DRAMで要求される容量、良好な漏れ電流特性を確保できるキャパシタ及びその製造方法を提供すること。

【解決手段】ストレージ電極15及びプレート電極17間のキャパシタの誘電膜16として、Al2O3/ZrO2、ZrO2/Al2O3、(ZrO2/Al2O3)n(2≦n≦10)、(Al2O3/ZrO2)n(2≦n≦10)、ZrO2/Al2O3/ZrO2の3重膜構造、窒化されたZrO2薄膜の単一膜、窒化Al2O3薄膜と窒化されたZrO2薄膜との2重膜、Al2O3薄膜と窒化されたZrO2薄膜との2重膜、又は、ZrO2薄膜、Al2O3薄膜及び窒化されたZrO2薄膜の3重膜を採用し、また、バンドギャップエネルギーの大きいZrO2(Eg=7.8eV、ε=20〜25)薄膜及び熱安定性に優れたAl2O3(Eg=8.7eV、ε=9)薄膜からなる多重誘電膜構造を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 フォトリソグラフィー工程を削減するとともに、短チャネル効果によるサブスレッショルド電流を抑制する。

【解決手段】 フィールド形成用のシリコン窒化膜102を用いて素子分離領域105を形成した後、このシリコン窒化膜102及び半導体基板100をパターニングすることにより、半導体基板100に達するゲートトレンチを活性領域106に形成する。次に、ゲートトレンチ内にゲート電極114を形成した後、シリコン窒化膜102を除去し、これにより形成されたコンタクトホール内にコンタクトプラグを埋め込む。これにより、拡散層コンタクトパターンが不必要となるとともに、活性領域を縮小することが可能となる。しかも、ゲート電極114がゲートトレンチ内に埋め込まれていることから、ゲート長が拡大され、サブスレッショルド電流を抑制することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】 縮小化されたセル面積でも大きな静電容量を有するキャパシタを得る。

【解決手段】 メモリセルの製造工程において、下部電極となる多結晶シリコンをフッ酸と酸化剤とを含むエッチング液で洗浄して、その表面を粗面化されて表面積を増大する。

(もっと読む)

フィールドプログラマブルゲートアレイを構成するためのプログラム可能な相互接続セル

本発明は、制御ゲート電位のノードと、ドレイン、ソース、フローティングゲート、前記制御ゲート電位のノードに接続された制御ゲートを有する第1のフローティングゲートフラッシュメモリトランジスタと、第1のプログラム可能なノードに接続されると共に、第2のプログラム可能なノードに接続されたドレイン、第1のフローティングゲートフラッシュメモリトランジスタのフローティングゲートに接続されたフローティングゲート、制御ゲート電位のノードに接続された制御ゲートを有する第2のフローティングゲートフラッシュメモリトランジスタとを有するプログラム可能な相互接続セル切り替え回路構造を備え、それによって、第1のフローティングゲートフラッシュメモリトランジスタのソースまたはドレインが、プログラム動作の間、セルの外でアースに接続されることを必要とする。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAMの容量素子の下部電極上に形成した誘電体膜を酸素雰囲気中で熱処理する際、下部電極を透過した酸素がバリア層を酸化して、高抵抗、低誘電率の酸化物層を形成する不具合を防止する。

【解決手段】溝27を形成した後、溝27から露出するプラグ22の表面にRuシリサイド層25を形成し、そのRuシリサイド層25の表面にRuシリコンナイトライド層26を形成する。続いて、溝27の内部に下部電極28を形成した後、その上部に誘電体膜29を形成し、酸素を含む雰囲気中で誘電体膜29を熱処理する。その後、誘電体膜29の上に上部電極30を形成する。これにより、誘電体膜29を形成する工程で行われる酸素雰囲気中での高温熱処理の際に、Ruシリコンナイトライド層26が犠牲的に酸化されてRuシリコンオキシナイトライドとなり、Ruシリサイド層25の酸化の進行を防止できる。

(もっと読む)

不揮発性半導体メモリの製造方法

【課題】安定でかつ信頼性の高い不揮発性半導体メモリを形成する。

【解決手段】p型シリコン半導体基板15に溝13a,13bを形成し、この溝13a,13b底面部に、不純物拡散層12a,12bを形成する。このようなp型シリコン半導体基板15上に、シリコン酸化膜からなる第1絶縁膜16a、シリコン窒化膜からなる電荷捕獲膜16b、およびシリコン酸化膜からなる第2絶縁膜16cが順に積層された3層構造のゲート絶縁膜16が形成される。このゲート絶縁膜16上に、ゲート電極11が形成される。ここで、溝13a,13bによって形成された凸部14は、不揮発性半導体メモリ10のチャネル領域となる。この不揮発性半導体メモリ10では、素子が微細化されても、その実効的なチャネル長が確保されるので、安定で、高い信頼性を実現できる。

(もっと読む)

磁気抵抗効果素子

【課題】面積抵抗RAの大幅な増大を招くことなく、高いMR変化率を有する磁気抵抗効果素子を製造できる方法を提供する。

【解決手段】磁化方向が実質的に一方向に固着された磁化固着層と、磁化方向が外部磁界に対応して変化する磁化自由層と、前記磁化固着層と前記磁化自由層との間に設けられた絶縁層及び前記絶縁層を貫通する電流パスを含むスペーサ層と、を有する磁気抵抗効果素子において、前記スペーサ層の下側に位置する前記磁化固着層または前記磁化自由層は膜厚方向に延びる粒界によって分離された結晶粒を含み、前記結晶粒の一端の面内方向位置を0とし、前記結晶粒の他端に隣接する粒界の面内方向位置を100としたとき、前記電流パスは面内方向位置が20以上80以下の範囲内にある領域上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 素子分離領域に埋込み形成される導電材に電位を与えるための専用のコンタクトを必要とすることなくチップ面積の縮小化を図りながらゲート電極の容量を形成することでソフトエラー対策を施すことができるようにする。

【解決手段】 トレンチ2の側溝部2bにゲート絶縁膜として第1のシリコン酸化膜3を介して多結晶シリコン膜6を埋込みながらゲート電極配線6としても機能させ、素子分離領域Sに埋込み形成される多結晶シリコン膜6およびNウェルNwを両電極としてキャパシタC1を構成する。

(もっと読む)

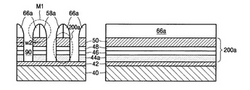

不揮発性半導体メモリの製造方法

【課題】安定でかつ信頼性の高い不揮発性半導体メモリを形成する。

【解決手段】p型シリコン半導体基板65への不純物導入後に溝63を形成し、この溝63を形成する凸部64a,64bに、不純物拡散層62a,62bを形成する。このようなp型シリコン半導体基板65上に、シリコン酸化膜からなる第1絶縁膜66a、シリコン窒化膜からなる電荷捕獲膜66b、およびシリコン酸化膜からなる第2絶縁膜66cが順に積層された3層構造のゲート絶縁膜66が形成される。このゲート絶縁膜66上に、ゲート電極61が形成される。ここで、p型シリコン半導体基板65の溝63の部分は、不揮発性半導体メモリ60のチャネル領域となる。この不揮発性半導体メモリ60では、素子が微細化されても、その実効的なチャネル長が確保されるので、安定で、高い信頼性を実現できる。

(もっと読む)

半導体メモリ

【課題】セルアレイの増大なく、ビット線ツイスト構造を実現する。

【解決手段】本発明の例に関わる半導体メモリは、第1及び第2ビット線BL0,bBL0と、第1カラム01内に配置される第1セルブロックBKと、第1ビット線BLと第1セルブロックBKとの間に接続される第1ブロックセレクトトランジスタBSTと、第2カラム02内に配置される第2セルブロックBKと、第2ビット線bBLと第2セルブロックBKとの間に接続される第2ブロックセレクトトランジスタBSTとを備える。第1及び第2ビット線BL,bBLは、ビット線ツイスト構造を有し、かつ、第1及び第2ビット線BL,bBLの入れ替えは、ブロックセレクタ領域BSで行われる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化を実現しつつリーク電流を抑制することができ、かつ、多くの容量を保持することができるDRAM混載半導体装置を提供する。

【解決手段】本発明の半導体記憶装置のキャパシタは、ストレージノードホール9の底面を覆い、側面を第2の層間絶縁膜8の上面の高さよりも低い高さまで覆う下部電極10と、下部電極の上を覆う容量絶縁膜11と、容量絶縁膜11の上を覆う上部電極12とを備える。この構造では、ビット線コンタクト14を形成するための開口17がずれてキャパシタにまで達しても、容量が蓄積される部分の容量絶縁膜が露出することがない。そのため、リーク電流の発生を抑制することができる。また、ストレージノードホール9と開口17との間にマージンを設ける必要がないので、微細化を実現することができると共に、メモリセルサイズが一定のままで保持できる容量を多くすることができる。

(もっと読む)

不揮発性半導体記憶装置及び相変化メモリ

【課題】 相変化メモリ素子を高集積化して十分な書込み電流を確保し、平面レイアウトや動作制御の面において有利な相変化メモリを提供する。

【解決手段】 本発明の不揮発性半導体記憶装置は、複数のワード線3と複数のビット線4がマトリクス状に配列され、ワード線3とビット線4の各交点に設けられた選択トランジスタ1と、一端が選択トランジスタ1に共通に接続されるとともに他端がそれぞれ異なる素子選択線5に接続され、情報の書込みと読出しが可能な所定数のメモリ素子2からなるメモリ素子群とを備える。制御対象の選択トランジスタ1を介して、メモリ素子群の中から選択されたメモリ素子2に接続された素子選択線5を経由して所定の電流を供給することにより、選択されたメモリ素子2に対する書込み動作と読出し動作を制御する。そして、半導体基板上では素子選択線5がビット線4と平行に配置されている。

(もっと読む)

記憶素子及びメモリ

【課題】 記憶素子に流す電流の極性を変えなくても情報の記録を可能にすることにより、構造を簡素化することができるメモリを提供する。

【解決手段】 記憶層5に対して中間層4を介して磁化固定層3が設けられ、記憶層5に対して、非磁性層6を介して、磁化の向きが積層方向にほぼ固定されている駆動層7が設けられ、積層方向に電流を流すことにより、記憶層5の磁化M2の向きが変化して記憶層5に対して情報の記録が行われる記憶素子10と、この記憶素子10に対して積層方向の電流を流す電流供給手段とを備え、電流供給手段から記憶素子10に電流が供給される時間の長さにより、記録される情報の内容が変わるメモリを構成する。

(もっと読む)

磁気抵抗効果素子

【課題】半選択セルの誤書き込み防止とスイッチング磁場の低減を図る。

【解決手段】本発明の例に関わる磁気抵抗効果素子は、第1及び第2強磁性層とこれらの間に配置される非磁性層とからなる積層構造を有し、第1及び第2強磁性層のうちの少なくとも1つは、第1方向に磁気異方性を有する第1部分と、第1部分に結合され、第1方向及びこれと逆向きの第2方向とは異なる第3方向に磁気異方性を有する第2部分とから構成される。

(もっと読む)

半導体メモリ装置とそのプログラミング方法

【課題】一つの選択トランジスタ及び8の倍数から構成された相変化可変抵抗素子から形成されたメモリセルを備える半導体メモリ装置の構造と、そのプログラミング方法とを提供する。

【解決手段】相変化メモリセルは、それぞれ、一端が対応するビットラインに連結され、他端が共通で選択トランジスタのドレインに連結され、8の倍数から構成された複数の相変化可変抵抗素子と、ゲートが対応するワードラインに連結され、ソースが基準電圧に連結された選択トランジスタと、を備える複数の相変化メモリセルを備える半導体メモリ装置である。これにより、半導体メモリ装置は、一つのメモリセルが8の倍数個の相変化可変抵抗素子を備えることにより、半導体装置の集積度を高めうる。

(もっと読む)

マルチビット不揮発性メモリセルを含む半導体素子及びその製造方法

【課題】マルチビット不揮発性メモリセルを含む半導体素子及びその製造方法を提供する。

【解決手段】不揮発性半導体素子は、ソース及びドレーン領域がそれぞれ共有される複数のトランジスタを備える単位セルを含み、複数のトランジスタは、それぞれ少なくとも一つのコントロールゲートと少なくとも一つの電荷蓄積領域とを含み、各コントロールゲートは各トランジスタのスレッショルド電圧をシフトするための少なくとも一つのコントロール電圧に連結される。これにより、フラッシュEEPROMの高集積化及びメガバイト当たり低コスト化を効果的に達成できる。

(もっと読む)

高密度及び高プログラミング効率のMRAM設計

磁気メモリを提供するための方法及びシステムが開示される。その磁気メモリは磁性素子を含む。その磁性素子は第1の書込み線及び第2の書込み線を用いて書き込まれ、第1の書込み線と第2の書込み線とが交差する場所に存在する。第2の書込み線は第1の書込み線に対して或る角度に向けられる。第2の書込み線は上側と少なくとも1つの側面とを有する。第2の書込み線の少なくとも一部が絶縁層によって覆われる。磁性層が絶縁層の一部を覆う。絶縁層のその一部は、磁性層と第2の書込み線との間に存在する。磁性層は軟磁性材料を含む。 (もっと読む)

半導体装置及びその製造方法

【課題】 深孔の壁面におけるボーイングが抑制されたスタック型キャパシタを備える半導体装置を提供する。

【解決手段】 半導体装置100は、シリコン基板101の主面上部に形成された第三の層間絶縁膜123と、第三の層間絶縁膜123内に形成され上部に開口を有する筒状の下部電極125と、下部電極125の表面を覆って形成された筒状の誘電体膜126と、誘電体膜126上に形成され誘電体膜126を介して下部電極125と対向する上部電極127とを備えるキャパシタと、下部電極125の底部に金属シリサイド124を介して接続されるコンタクトプラグ122とを備える。下部電極125は、開口に隣接する上部電極部分が2層の多結晶シリコン膜153,154で構成され、金属シリサイド124に隣接する底部電極部分が2層の多結晶シリコン膜153,154の内で最上層の多結晶シリコン膜154で構成される。

(もっと読む)

2,241 - 2,260 / 2,405

[ Back to top ]