Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,281 - 2,300 / 2,405

サブパターン転写ナノスケールインターフェースの確率的組立体

ナノスケール配線の電気伝導を制御する方法を示した。ナノスケール配線には、軸方向および/または半径方向に分布する制御可能領域が設けられる。ミクロスケール配線または追加のナノスケール配線によって、これらの領域を制御することにより、ナノスケール配線の電気伝導を可能にしたり、遮断したりすることができる。制御可能領域には2の異なる種類がある。例えば第1の制御可能領域は、第2の制御可能領域とは異なるドーピング特性を示す。この方法では、サブパターン転写ピッチで束ねられた1または2以上のナノスケール配線組を別々に選択することができる。 (もっと読む)

半導体装置の製造方法

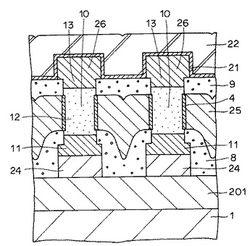

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜13が設けられる。キャパシタ絶縁膜13を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化に有利で信頼性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、ゲート電極上に金属層31を備えたトランジスタSTと、順次設けられた第1バリア膜23、第1絶縁層24、第2バリア膜25、第2絶縁層26と、前記第2バリア膜に第1幅W1で開口し第1方向に伸びる溝と、前記第2絶縁層を貫通して前記第2バリア膜中に底部40を有し前記底部が前記第1方向に交差する第2方向に前記第1幅よりも大きい第2幅W2を有するコンタクトホール上部39−1と、前記コンタクトホール上部から前記溝を介して前記第1絶縁層および第1バリア膜を貫通して前記拡散層上に設けられ前記第2方向に上面が前記1幅W1を有するコンタクトホール下部39−2と、前記コンタクトホール上部内および前記コンタクトホール下部内に連続して導電体が埋め込まれたコンタクト39を具備する。

(もっと読む)

記憶装置及び半導体装置

【課題】 メモリ素子に均一に電圧を印加することができる記憶装置及びこうした記憶装置を有する半導体装置を提供する。

【解決手段】 行方向に配列されたソースラインと、列方向に配列されたビットラインと、第1の閾値電圧以上の電圧が印加されることによって書き込みを行い、第2の閾値電圧以上の電圧が印加されることによって消去を行なう特性を有し、ソースラインとビットラインの交点に配設されたメモリ素子と、ビットラインの一端と接続され、ビットラインに所定電圧を印加するドライバと、ビットラインの最も他端側に位置するメモリ素子に印加される電圧を設定電圧と比較して、ドライバがビットラインに印加する電圧を調整するオペアンプとを備える。

(もっと読む)

集積回路メモリ装置

【課題】一対の第1ビットラインとビットラインプリチャージ/選択回路に電気的に接続される第1カラムメモリセルを有する集積回路メモリ装置を開示する。

【解決手段】ビットラインプリチャージ/選択回路は、薄膜トランジスタからなる少なくとも一つの積層構造を有する。このような薄膜トランジスタは第1PMOSプルアップ薄膜トランジスタ及び第1NMOSパス薄膜トランジスタを有する。また、薄膜トランジスタは、一対の第1ビットラインの一つのラインに電気的に接続される。1カラムメモリセルは薄膜トランジスタSRAMセルを含む。

(もっと読む)

半導体装置

【課題】 キャパシタの側面の傾斜を最適化することにより、特性や信頼性に優れた半導体装置を提供する。

【解決手段】 半導体基板10と、半導体基板の上方に設けられ、下部電極21と、下部電極上に設けられた誘電体膜22と、誘電体膜上に設けられた上部電極23とを含むキャパシタと、上部電極上に設けられ、キャパシタのパターンを形成する際のマスクとして用いるマスク膜31とを備えた半導体装置であって、マスク膜の側面の傾斜は、上部電極の側面の傾斜及び誘電体膜の側面の傾斜よりも緩い。

(もっと読む)

抵抗スイッチング半導体メモリー

本発明の目的は、CBRAMメモリーセルを有し、上記CBRAMメモリーセルが、AgドープされたGeSe層とAGトップ電極との間に、化学的に不活性な境界層を有し、上記境界層が、CBRAMメモリーセルの切り替え特性を改善する不揮発性半導体メモリーを提供することである。この目的は、本発明に基づいて、メモリーセルを活性マトリックス材料層が、ガラス状のGeSe層とアモルフGe:H層とを有するGeSe/Ge:H二重層を備え、アモルフGe:H層が、GeSe層と第2電極との間に配置されていることによって達成される。その結果、Agドーピング層および/または電極層におけるAgSe塊の形成が抑制される。その結果、堆積が防止され、銀ドーピング層を均一に堆積できる。GeSe/Ge:H二重層組織により、一方ではCBRAMメモリーセルの抵抗不揮発性メモリー作用が得られ、他方では、薄いGe:H層を用いて、薄いGe:H層上に設けられる上部電極の化学的安定性が保証される。  (もっと読む)

(もっと読む)

不揮発性メモリ素子及びその形成方法

【課題】不揮発性メモリ素子およびその形成方法を提供する。

【解決手段】本発明の不揮発性メモリ素子は、半導体基板に形成された第1及び第2不純物拡散領域、前記第1及び第2不純物拡散領域の間の半導体基板のチャンネル領域上に形成されたメモリセルを含む。前記メモリセルは前記チャンネル領域上に形成された積層ゲート構造及び前記チャンネル領域上に、そして前記積層ゲート構造の両側壁上に形成された第1及び第2選択ゲートを含む。前記第1及び第2選択ゲートがスペーサ形態で前記積層ゲート構造の両側壁に自己整列されるので、メモリセルの大きさを減らすことができるので、素子の集積度を向上させることができる。

(もっと読む)

オボニック閾値スイッチを有する相変化メモリ

【課題】 相変化メモリはメモリ要素と選択要素とを有する。

【解決手段】 メモリ要素は誘電体中に埋め込まれ、少なくとも1つのサブリソグラフィック寸法を有する抵抗性要素と抵抗性要素と接触している記憶領域とを有する。選択要素は誘電体中に埋め込まれたカルコゲン材料を有する。カルコゲン材料及び記憶領域は共通のエッチング端部を有するスタックの一部である。

(もっと読む)

反転型FinFET薄膜トランジスタを用いたFinFETSRAMセル

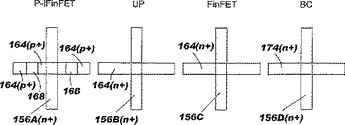

【課題】反転型FinFETトランジスタ(P2)とFinFETトランジスタ(N3)とを含む、SRAMセル(130)などの集積回路を提供すること。

【解決手段】反転型FinFETトランジスタは、基板上に半導体構造(100)によって形成された第1のゲート領域(108)、ならびに、第1のゲート領域上に配置された第1のチャネル領域(112)と、第1のチャネル領域のいずれか一方の側に形成されたソース(110)およびドレイン(114)とを有する、半導体層(104)からなる第1のボディ領域を含む。FinFETトランジスタ(N3)は、反転型FinFETトランジスタに結合しており、第2のチャネル領域(118)と、第2のチャネル領域のいずれか一方の側に形成されたソース(116)およびドレイン(120)とを有する、半導体構造(102)によって形成された第2のボディ領域、ならびに、第2のチャネル領域上に配置された、半導体層からなる第2のゲート領域(122)を含む。  (もっと読む)

(もっと読む)

電荷捕獲半導体メモリデバイス

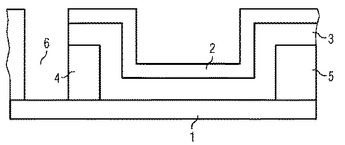

【課題】 大きさがさらに低減された電荷捕獲半導体メモリデバイスを提供する。

【解決手段】 メモリセルは、半導体基板(1)の主表面における好適には円柱状の凹部(2)により形成され、側壁におけるメモリ層シーケンス(3)とゲート電極(4)とを備えており、列を成して第1のビット線(8)および第2のビット線(9)に接続された上部ソース/ドレイン領域(5)および下部ソース/ドレイン領域(6)が提供されている。ワード線(10)が、第1のビット線(8)および第2のビット線(9)の上部に配置されており、ゲート電極(4)の行に接続されている。その鉛直方向のトランジスタ構造により、セルのさらなる縮小化が容易になり、所望される最小有効チャネル長が可能になる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】製造が容易で高集積化が可能な強誘電体メモリの構成と製造法を提供する。

【解決手段】半導体記憶装置は、半導体基板と、この半導体基板上に形成され、ソース・ドレインとなる1対の不純物領域とゲート電極を有するMOSトランジスタと、1対の不純物領域の一方の上に形成されたコンタクトプラグと、このコンタクトプラグ上に形成され、下部電極層、強誘電体層、上部電極層が積層された平面型の強誘電体キャパシタとを有し、コンタクトプラグの側面上端は強誘電体キャパシタ側面の下端の対応する部分と整合して形成されている。

(もっと読む)

半導体装置

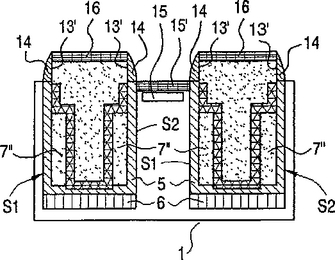

【課題】 半導体基板の主表面に対して平行な方向における面積を小さくすることができる薄膜トランジスタを有するラッチ回路を備えた半導体装置を提供する。

【解決手段】 1つのメモリセル領域100を横切る同一層に形成されたビット線15および他のビット線とは別の層にグラウンド配線層16が形成されている。このグラウンド配線層16は、メモリセル領域100内のほぼ全ての領域にわたって形成されている。また、メモリセル領域100内においてプラグ18および19がグラウンド配線層16を上下に貫通しているが、絶縁膜18aおよび絶縁膜19aによってグラウンド配線層16とプラグ18および19のそれぞれとが絶縁されている。

(もっと読む)

半導体メモリ装置のライン配置構造

【課題】半導体メモリ装置のライン配置構造を提供する。

【解決手段】複数個のメモリセルを有する半導体メモリ装置のライン配置構造において、前記メモリセルに連結されるビットラインを形成する第1金属配線ラインと、前記第1金属配線ラインの上部で前記第1金属配線ラインと交差するように配置されて前記メモリセルに連結されるセクションワードラインを形成する第2金属配線ラインと、前記第2金属配線ラインの上部で前記第2金属配線ラインと平行に配置されて第1電源ラインまたは信号ラインを形成する第3金属配線ラインと、を備える。

(もっと読む)

縦型スプリット・ゲート不揮発性メモリ・セルおよび製造方法

半導体基板上に、少なくとも1つのビットを記憶する縦型スプリット・ゲート不揮発性メモリ・セルを備え、基板上に、トレンチと、第1の活性領域と、第2の活性領域と、トレンチの側壁に沿って延びるチャネル領域とを含み、このトレンチは、第1の方向に延びる長さと、それに垂直な第2の方向に延びる幅を有し、トンネル酸化物によって側壁が覆われており、少なくとも1つの浮遊ゲートおよび制御ゲートのゲート・スタックを含み、制御ゲートがトレンチの底部まで延び、第1の浮遊ゲートが、制御ゲートと共に第1のスタックを形成するようにトレンチの左壁に位置するとともに、第2の浮遊ゲートが、制御ゲートと共に第2のスタックを形成するようにトレンチの右壁に位置する半導体デバイス。  (もっと読む)

(もっと読む)

抵抗スイッチング素子及び界面抵抗型不揮発性メモリ素子

【課題】 強相関電子系物質の電界誘起相転移現象を用いた、低コストなスイッチング素子と、低コスト、大容量の不揮発性メモリを提供する。

【解決手段】 チタンマグネリ相化合物やバナジウムマグネリ相化合物は強相関電子系物質であり、印加電界によって絶縁体相から金属相に、金属相から絶縁体相に可逆的に相転移する。絶縁体相と金属相の抵抗の違いを利用すれば、抵抗スイッチング素子が実現できる。金属相は、電界を除去することによって絶縁体相に戻るので、このままでは不揮発性メモリとならないが、マグネリ相化合物相と酸化物半導体を接合することにより、スイッチして形成された金属相が電界を除去しても保持されるようになり、不揮発性メモリを実現することができる。

(もっと読む)

半導体装置およびICカード

【課題】不揮発性メモリにおいて、メモリアレイの面積の増大を抑えて、記憶情報の書き換えの信頼性を向上させることのできる技術を提供する。

【解決手段】ソースSを共有し、対称の位置にある2つのメモリセルM00およびM10に対して別個のビット線BL0およびビット線BL1をそれぞれ接続して、1つのメモリセルM00(またはメモリセルM10)が占有する領域のチャネル幅方向の幅に対して2本のメタル配線(ビット線BL0およびビット線BL1)を配置する。これに対し、2ワード分のメモリセルM00およびM10のメモリゲートMGと、コントロールゲートCGとをそれぞれ同電位として、2つのメモリセルM00およびM10が占有する領域のチャネル長方向の長さに対して3本のメタル配線(コントロールゲート制御線CG0、メモリゲート制御線MG0および共通ソース線SL0)を配置する。

(もっと読む)

半導体記憶装置

【課題】ビット線交差方式を採用して隣接ビット線間の容量を低減する効果を維持しつつも、ダミーメモリセルを無くしてメモリセルアレイの面積の増大を回避し得る半導体記憶装置を得る。

【解決手段】第2配線層内には、交差配線18a,18bとシャント配線SL0〜SL2,SL7〜SL9とが形成されている。交差領域TR3,TR4は、第X3〜X6行に属している。シャント配線SL0〜SL2,SL7〜SL9は、交差領域TR3,TR4が属さない第X0〜X2,X7〜X9行にそれぞれ属している。第4配線層内には、シャント配線SL3〜SL6が形成されている。シャント配線SL3〜SL6は、交差領域TR3,TR4が属する第X3〜X6行にそれぞれ属している。

(もっと読む)

不揮発性半導体記憶装置

【課題】 高集積化を実現することができる不揮発性半導体記憶装置を提供すること。

【解決手段】 本発明の不揮発性半導体記憶装置は,半導体基板にトレンチ領域を設け,

1つのトレンチ領域の側壁の両側に,それぞれ,NAND型メモリセルユニットを三次元

的に有している。そしてこれらのNANDメモリセルユニットは,1本のビット線に接続

されている。それぞれのNAND型メモリセルユニットは,複数のメモリセルトランジス

タと選択ゲートトランジスタが直列に接続されている。これらの複数のメモリセルトラン

ジスタ及び選択ゲートトランジスタは,同一のトレンチ領域に設けられている。さらに,

本発明の不揮発性半導体記憶装置においては,メモリセルトランジスタの電荷蓄積層には

,従来のような浮遊ゲートの替わりに,酸化珪素膜,窒化珪素膜,酸化珪素膜の積層構造

,又はシリコン,金属その他の導電性物質のナノ結晶を含有する絶縁層を用いている。

(もっと読む)

半導体メモリ装置及びリード動作方法

【課題】リード動作の時に漏洩電流を補償することができる相変化メモリ装置を提供する。

【解決手段】ワードラインとビットラインとの交差点に位置する複数個のメモリセルと、ダミービットラインに連結された複数個のダミーセルと、前記ダミービットラインに連結され漏洩補償電流を前記ビットラインに出力する漏洩補償回路と、第1制御信号に応じてリード動作時に必要なリード電流を前記ビットラインに出力する理度電流供給回路と、を備える。

(もっと読む)

2,281 - 2,300 / 2,405

[ Back to top ]