Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,341 - 2,360 / 2,405

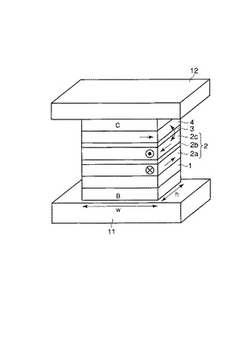

磁気抵抗効果素子、磁気ヘッド、磁気記録再生装置、および磁気メモリ

【課題】高MR変化率が得られ、高密度化への対応が期待できる磁気抵抗効果素子を提供する。

【解決手段】実質的に磁化方向が固着された第1の磁性層と、外部磁界に応じて磁化方向が変化する第2の磁性層と、前記第1の磁性層と前記第2の磁性層との間に設けられた磁性スペーサ層と、前記第1の磁性層、磁性スペーサ層および第2の磁性層を含む積層膜の膜面垂直に電流を通電する電極とを有し、外部磁界がゼロのときに、前記第1の磁性層の磁化方向と前記第2の磁性層の磁化方向がほぼ直交している磁気抵抗効果素子。

(もっと読む)

半導体装置およびその製造方法

【課題】 素子形成領域の占有面積を増大させることなく電気的分離が確実に行なわれる半導体装置と、その製造方法を提供する。

【解決手段】 半導体基板上にBOX層を介在させてN−層3が形成されている。そのN−層3には素子形成領域となるN−層3aを取囲むようにトレンチ分離領域4が形成されている。トレンチ分離領域4はN−層3の表面からBOX層に達するように形成されている。トレンチ分離領域4の外側には、他の素子形成領域となるN−層3bが位置している。トレンチ分離領域4とN−層3aとの間には、P型拡散領域10aが形成されている。P型拡散領域10aは、素子形成領域を取囲むトレンチ分離領域4の内側側壁の全面に接するように切れ目なく連続して形成されている。N−層3a等の素子形成領域には、所定の半導体素子が形成される。

(もっと読む)

強誘電体キャパシタの製造方法

【課題】寸法変換差の小さい微細強誘電体キャパシタの製造方法を提供する。

【解決手段】先ず、半導体基板を用意し、この半導体基板上に第1層間絶縁膜20を形成する。層間絶縁膜20上にメタル層31、第1導電体層33、強誘電体層35及び第2導電体層37を備えるキャパシタ形成用積層膜30を形成し、キャパシタ形成用積層膜上にタンタル酸ストロンチウム又はニオブ酸ストロンチウムからなるエッチングマスク形成用膜39を形成する。エッチングマスク形成用膜39上に強誘電体キャパシタ形成領域を覆うシリコン酸化膜マスク52を形成して、シリコン酸化膜マスクを用いてエッチングマスク形成用膜に対するウェットエッチングを行うことにより、エッチングマスク49を形成する。エッチングマスクを用いてキャパシタ形成用積層膜に対してドライエッチングを行うことにより、バリアメタル41、下部電極43、強誘電体膜45、及び上部電極47を備える積層体40を形成する。

(もっと読む)

磁気トンネル接合、磁気ランダムアクセスメモリ、渦磁化状態の形成方法および渦磁化状態の切り換え方法

【課題】 フリー層およびリファレンス層が渦磁化状態を有し、高密度用途および高速用途に適用することが可能なMRAMを提供する。

【解決手段】 自由な回転方向を伴う渦磁化状態を有する強磁性フリー層27に交換結合定数を低下させるためのドーパントが含まれていると共に、固定された回転方向を伴う渦磁化状態を有する強磁性ピンド層25(リファレンス層)に交換結合定数を低下させるためのドーパントが含まれている。磁化状態を切り換えるために形状異方性を利用していた従来の場合とは異なり、交換結合定数やMst(飽和磁束密度×厚さ)などに代表される磁性膜に固有な膜特性を利用して磁化状態が切り換えられるため、大きな保磁力が得られる。

(もっと読む)

半導体装置

【課題】 ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】 ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体記憶装置とその製造方法

【課題】 キャパシタとビアコンタクトとのショートを防止することが困難であった。

【解決手段】 トランジスタTrは半導体基板11の表面領域に形成されている。キャパシタCpはトランジスタの上方に形成され、第1の電極17、第2の電極19、及び前記第1、第2の電極の相互間に形成された誘電体膜18とを有している。第1のコンタクト24はキャパシタの側面部でキャパシタの少なくとも一部に近接して形成され、ソース/ドレイン領域の一方に接続されている。側壁絶縁膜23は第1のコンタクト24の側壁で、少なくともキャパシタCpに接して形成されている。

(もっと読む)

高密度SOIクロスポイントメモリアレイおよびそれを製造するための方法

【課題】 SOI RRAMアレイにおいて形成されたメモリセルの密度を増大し、利用可能な最小形状をうまく利用したアレイを提供すること。

【解決手段】 高密度SOIクロスポイントメモリアレイを製造するための方法は、SOI基板上にハードマスクを形成し、メモリ領域、活性デバイス領域、および上部電極領域を定義するステップと、露出したSi表面を除去するようにエッチングするステップと、ハードマスクに隣接した金属側壁を形成するステップと、メモリ領域をメモリレジスタ材料で満たすステップと、ハードマスクを除去して上に重なるSi活性デバイス領域を露出するステップと、上に重なる酸化物の層を形成するステップと、酸化物をエッチングし、活性デバイス領域にコンタクトホールを形成するステップと、コンタクトホールにおいてダイオードを形成するステップと、ダイオードの上に重なる底部電極線を形成するステップとを包含する。

(もっと読む)

密集したメモリゲートを有するNANDフラッシュメモリ及び製作方法

【課題】 半導体メモリ素子、NANDフラッシュメモリとその製作方法を提供する。

【解決手段】 メモリゲート及び電荷蓄積層を有するセルが密集し、隣接セル内のメモリゲートが互いに部分的に重なるか又は互いに自己整列するNANDフラッシュメモリセルアレイ及び製造方法。メモリセルは、ビット線拡散部と共通ソース拡散部の間で列状に配置され、電荷蓄積層は、セル内のメモリゲートの下に位置決めされる。プログラミングは、負電荷を電荷蓄積ゲートに蓄積させるためにシリコン基板から電荷蓄積ゲートまでのホットエレクトロン注入、又は正電荷を電荷蓄積ゲートに蓄積させるためにシリコン基板から電荷蓄積ゲートまでのホットホール注入により行われる。消去は、プログラミング方法により電荷蓄積ゲートからシリコン基板まで又はその逆のチャンネルトンネリングにより行われる。

(もっと読む)

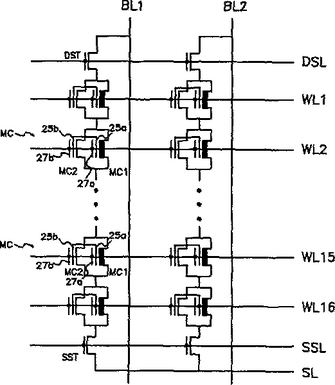

不揮発性半導体記憶装置

【課題】

サイドウォール型メモリセルで構成されたメモリセルアレイを備え、且つ、フラッシュメモリと同等にブロック消去が可能な不揮発性半導体記憶装置を提供する。

【解決手段】

MOSFET構造を有し、ゲート電極の両側に電荷保持機能を有するメモリ機能体を備えたサイドウォール型メモリセルをマトリクス状に配列したメモリセルアレイ100を複数備えてなる不揮発性半導体記憶装置であって、メモリセルアレイ100が、複数のセクタ101に分割して構成され、メモリセルアレイ100の1つが一括消去される場合に、一括消去の対象となるメモリセルアレイを構成する複数のセクタの中から、複数回に分けて同時に所定数または前記所定数以下のセクタを順次選択するセクタ選択回路105と、一括消去の実行時に、セクタ選択手段105が同時に選択したセクタに対し、消去用の所定電圧を印加する消去電圧印加回路106,107を備える。

(もっと読む)

不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法

本発明は、不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法に関するものである。不揮発性メモリーセルは、チャネル領域として設計されたナノ素子を有する垂直電界効果トランジスタと、ナノ素子を少なくとも部分的に取り囲む、電荷蓄積層として、および、ゲート絶縁層としての電気絶縁層とを備えている。この電気絶縁層は、電気的な電荷担体をその内部に選択的に注入でき、または、その内部から除去できるように設計されており、電気絶縁層に注入された電気的な電荷担体によって、ナノ素子の導電性に特徴的に影響を及ぼすように設計されている。  (もっと読む)

(もっと読む)

磁気記憶装置およびその製造方法

【課題】 微細な磁気記憶装置を提供する。また、簡便に磁気記憶装置を製造する方法を提供する。

【解決手段】 絶縁膜105中には、複数の磁気エレメント104が離間して配設されている。また、絶縁膜105の上には、磁気エレメント104に電気的に接続するビットライン配線112が形成されている。さらに、絶縁膜105の上には、絶縁膜1が、ビットライン配線112の側面および上面を被覆するようにして形成されている。高透磁率膜113は絶縁膜1を介して設けられているので、高透磁率膜113をパターニングしなくとも、隣接するビットライン配線112の間が電気的に接続されることはない。

(もっと読む)

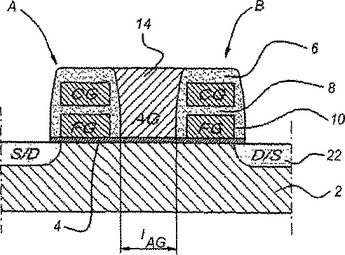

自己整合型の2ビット「ダブル・ポリCMP」フラッシュ・メモリ・セル

第1の浮遊ゲート・スタック(A)と、第2の浮遊ゲート・スタック(B)と、中間アクセス・ゲート(AG)とを含むメモリ・セルの製作。浮遊ゲート・スタック(A、B)は、第1のゲート酸化物(4)と、浮遊ゲート(FG)と、制御ゲート(CG;CGl、CGu)と、ポリ間誘電体層(8)と、キャッピング層(6)と、側壁スペーサ(10)とを含む。メモリ・セルはさらに、ソースおよびドレイン接触部(22)を含む。このメモリ・セルの製作は、浮遊ゲート・スタックを等しい高さにするために同じ処理工程で画定すること、ポリSi層(12)を浮遊ゲート・スタックの高さよりも大きな厚みで浮遊ゲートを覆って堆積させること、ポリSi層(12)を平坦化すること、浮遊ゲート・スタック間のポリSi層上にアクセス・ゲート・マスクを使用するマスキング工程およびポリSiエッチング工程によって、平坦化されたポリSi層(14)内に中間アクセス・ゲート(AG)を画定することを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 DRAMセルのセルリークを抑制し、微細化にも好適な半導体装置の製造方法を提供することを目的とする。

【解決手段】 半導体基板11に形成されたトレンチ内壁の所定の領域に、前記半導体基板11と反対の導電型の不純物を含むシリコン酸化膜17を形成した後、前記半導体基板11と同一の導電型の不純物を含む絶縁膜19により前記シリコン酸化膜17を被覆する。次に、前記半導体基板11を熱処理して前記半導体基板11と反対の導電型の不純物および同一の導電型の不純物を前記半導体基板11内に拡散させた後、前記絶縁膜19および前記シリコン酸化膜17を順次剥離して、プレート電極となるプレート20を形成する。次に、前記トレンチに絶縁分離膜を形成して導電膜を埋め込んだ後、所定の領域にゲート、ドレイン、ソースからなるトランジスタを形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルのサイズを縮小することができる不揮発性半導体記憶装置及びその製造方法を提供すること

【解決手段】不揮発性半導体記憶装置1は、第1方向Xに沿って形成されたトレンチ20を有する基板10と、そのトレンチ20外の基板10表面上に第1ゲート絶縁膜11を介して形成された浮遊ゲート40と、そのトレンチ20内の基板10表面上に第2ゲート絶縁膜21を介して形成された埋設ゲート30と、第3ゲート絶縁膜31を介して浮遊ゲート40を覆うように形成された制御ゲート50と、浮遊ゲート40下方の基板10中に形成されたソース領域61及びドレイン領域62とを備える。

(もっと読む)

メモリデバイス、トランジスタ、メモリセル並びにそれらの製造方法

メモリデバイスはメモリセルのアレイと周辺デバイスを含んでいる。少なくとも一部の個別メモリセルはSiCを含む炭酸化部分を含んでいる。少なくとも一部の周辺デバイスは炭酸化部分を含まない。トランジスタは第1ソース/ドレーン、第2ソース/ドレーン、第1ソース/ドレーンと第2ソース/ドレーンとの間にSiCを含む半導体基板の炭酸化部分を含んだチャンネル、及びチャンネルの両側と作動式に関係するゲートを含んでいる。 (もっと読む)

フラッシュEEPROM単位セル及びこれを含むメモリーアレイ構造体

【課題】 高集積フラッシュEEPROM単位セル及びそれを含むメモリーアレイ構造体 を提供する。

【解決手段】 本発明によるフラッシュEEPROM単位セルは、単位セルの分離のためのフィールド酸化膜が形成されている基板と、隣接する前記フィールド酸化膜の間に形成され、前記基板に形成されたソースとドレーンの間で並列連結されている第1の誘電体膜及び第2の誘電体膜を含み、前記第1の誘電体膜の厚さは前記第2の誘電体膜より厚く形成されているフローティングゲート誘電体膜と、前記フローティングゲート誘電体膜の上部に積層されているフローティングゲートと、前記フローティングゲートの上部に積層された制御ゲート誘電体膜と、前記制御ゲート誘電体膜の上部に積層された制御ゲートと、を含むことをことを特徴とする。  (もっと読む)

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】 冗長救済機能を備えた半導体記憶装置を有するロジック半導体装置において、半導体装置の高集積化に伴って生じる半導体装置の面積を増大させることなく、冗長救済を行なった後も、内部回路素子の金属配線における腐食の発生を防止する。

【解決手段】 半導体基板10上に形成された冗長救済されるべき回路素子を含む内部回路素子26と、半導体基板10上に内部回路素子26を覆うように形成された第1、第2及び第3の層間絶縁膜15、18及び21と、第3の層間絶縁膜21の上に形成された冗長救済されるべき回路素子26の冗長救済に用いられるヒューズ25とを備えている。第3の層間絶縁膜21とヒューズ25との間には、耐透水性を有する絶縁膜22が介在している。

(もっと読む)

半導体装置

【課題】本発明は、階層化されたビット線を有する半導体メモリにおいて、これらのビット線の配線レイアウトの効率化を図るとともに、全体のレイアウト面積を削減できるようにするものである。

【解決手段】たとえば、1つのカラムにおいて、グローバルビット線対GBL,GBLBには、複数のローカルビット線対LBL,LBLBが、それぞれ、選択トランスファーゲート15a,15bを介して共通に接続されている。そして、それぞれの選択トランスファーゲート15a,15bを構成する、PMOSスイッチトランジスタSPa,SPbおよびNMOSスイッチトランジスタSNa,SNbが、それぞれ、メモリセルアレイ11を挟んで反対側に配置されてなる構成となっている。

(もっと読む)

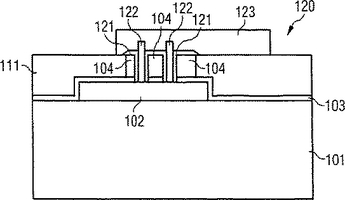

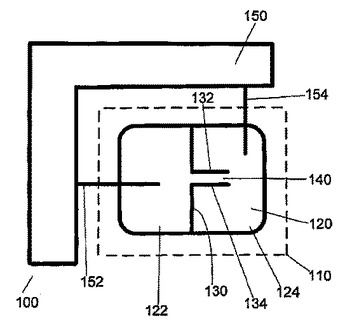

自己スイッチングメモリデバイス

メモリデバイス、及び関連する製造及び動作の方法を説明している。該メモリデバイスは、移動電荷キャリアを支持する基板(120)を具えている少なくとも1つのメモリユニットを含む。該基板表面上には絶縁部(130、132、134)が形成され、該絶縁部の両側に第1及び第2基板領域(122、124)を形成している。該第1及び第2基板領域は、絶縁部によって形成された細長チャネル(140)によって接続されている。メモリユニットは、前記第1及び第2領域間の所定の電位差でチャネルが第1及び第2領域間に第1のコンダクタンスを与える第1の状態と、前記所定の電位差でチャネルが第1及び第2領域間に第2の異なるコンダクタンスを与える第2の状態との間で切り換え可能である。メモリユニットを第1の状態に変更するため、前記メモリユニットの第1及び第2領域に第1の電位差を、そしてメモリユニットを第2の状態に変更するため第2の異なる電位差を印加するよう、書き込み回路(150)が構成されている。メモリユニットの状態を読み出すため、メモリユニットの第1及び第2領域に前記所定の電位差を印加するよう、読み出し回路(150)が構成されている。  (もっと読む)

(もっと読む)

ゲート当たりトラップ位置を2つ有する電荷をトラップする不揮発性メモリおよびその動作方法

【課題】容易に製造され高密度の用途に対応する不揮発性メモリ用のメモリ技術を提供する。

【解決手段】マルチゲート型メモリセルは、半導体本体と、半導体本体上に直列に配列された複数のゲート50,51とを備える。半導体本体上の電荷蓄積構造体は、複数のゲート50,51におけるすべてまたはいくつかのゲートのそれぞれの下の2つの電荷トラップ位置を含む。ソース55およびドレイン56のバイアス電圧を、半導体本体の、直列における第1のゲート50および最後のゲート51の近くに伝える回路、ならびにゲートのバイアス電圧を複数のゲートに伝える回路が備えられる。マルチゲート型メモリセルは、直列における複数のゲート50,51の下の、連続したマルチゲートのチャネル領域58を含み、電荷蓄積位置がゲートのうちのいくつかまたはすべての間にある。

(もっと読む)

2,341 - 2,360 / 2,405

[ Back to top ]