Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,381 - 2,400 / 2,405

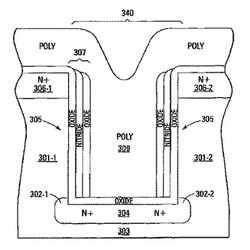

NROMデバイス

【課題】1セルに対して複数のビットが記憶可能な高性能のフラッシュメモリトランジスタを提供する。

【解決手段】NROMフラッシュメモリセルのアレイは、4F2あたり少なくとも2ビットを記憶するように構成される。スプリット縦型チャネルは、隣接する柱状部の各側面に沿って形成される。単一の制御ゲートが柱状部及び柱状部間のトレンチ内にわたって形成される。スプリットチャネルは、トレンチ底部のn+領域、又はトレンチ底部を覆うように形成されるチャネルによって接続され得る。各ゲート絶縁層は、チャネル長の増大により、他の電荷記憶領域から十分に分離した状態で電荷を記憶することができる。

(もっと読む)

縦型EEPROMNROMメモリデバイス

【課題】電荷捕獲領域の重なりがなく、過消去特性が改善された、より狭い素子間隔の高密度なNROMメモリアレイを製造する方法及び構造体を提供する。

【解決手段】NOR又はNAND型高密度メモリ構成において縦型NROMメモリセル及び縦型選択ゲートを有効に利用するNROM EEPROMメモリデバイス及びアレイが開示される。本発明に係るメモリの実施形態では、縦型選択ゲート及び縦型NROMメモリセルを用いて、NOR及びNAND型NROM構成のメモリセル列、メモリセグメント及びメモリアレイを形成する。これらNROMメモリセル構成によって、構成要素として選択ゲートを有するメモリデバイス又はメモリアレイをより高密度にすることが可能となる。これらメモリデバイス又はメモリアレイにおいては、半導体製造プロセスによって作製可能な加工寸法を利用することができ、かつ、典型的なマルチビットNROMセルにおいて存在する電荷分離に関する問題を被ることがない。さらに、上述のメモリセル構造体は、NROMメモリセルからそれらに関連したビット/データ線及び/又はソース線とを絶縁する選択ゲートの後ろに、NROMメモリセルを配置することによって、擾乱及び過消去問題を軽減することが可能となる。

(もっと読む)

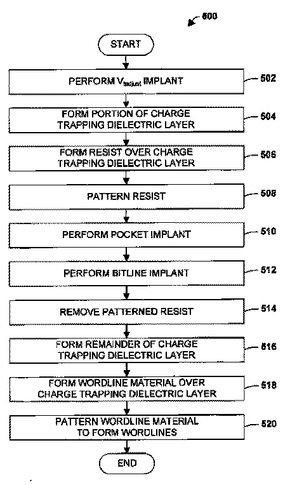

SONOSメモリセルの相補ビット妨害および蓄電の改善のためのポケット注入

デュアルビットメモリコアのアレイの少なくとも一部を形成する方法が開示される。最初に、電荷トラップ誘電層(608)の一部が基板(602)上に形成され、電荷トラップ誘電層(608)の一部の上にレジスト(614)が形成される。レジスト(614)がパターニングされ、ポケット注入(630)が所定の角度で実行され、基板(602)内にポケット注入部(620)が形成される。次に、基板(602)内に埋込みビット線(640)を形成するためにビット線注入(634)が実行される。次に、パターニングされたレジストが除去され、電荷トラップ誘電層(608)の残部が形成される。電荷トラップ誘電層の残部の上にワード線の材料(660)が形成されて、それはビット線(640)上にワード線(662)を形成するためにパターニングされる。ポケット注入部(620)は、特に、微細化によって生じるおそれのある相補ビット妨害(CBD)を軽減するのに役立つ。このように、ここに記載する発明思想により、半導体デバイスを小型化でき、高い実装密度を実現することができる。  (もっと読む)

(もっと読む)

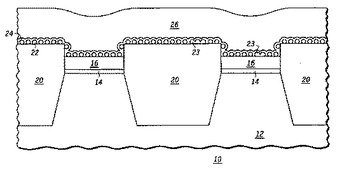

改良された表面形状を用いるメモリ構造の形成方法及びその構造。

半導体装置10のゲートカップリング比を増大させるため、超微細結晶等の個別素子22が浮遊ゲート16上に析出される。一実施形態において、個別素子22は、蒸気相中で予め形成され、静電気力によって半導体装置10に吸着される。一実施形態において、個別素子22は、それらが吸着されるチャンバとは異なるチャンバ内で予め形成される。更に別の実施例において、同じチャンバが全ての析出工程に使用される。界面層17は、必要に応じて、浮遊ゲート16と個別素子22との間に形成される。  (もっと読む)

(もっと読む)

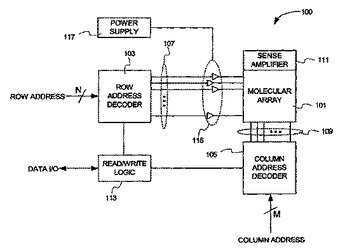

分子メモリデバイスおよび方法

スイッチングデバイスと、前記スイッチングデバイスに結合された少なくとも第1のビット線および第1のワード線と、それぞれがビット線およびワード線に結合された記憶位置のアレイとを具備する分子メモリ素子であって、前記素子は、レドックス活性分子を含む記憶分子を有する第1の電極を具備し、前記アレイは、第2の電極を具備する。

(もっと読む)

(もっと読む)

半導体メモリセルおよびその製造方法

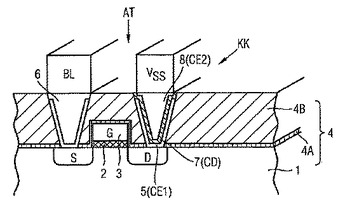

本発明は、ストレージキャパシタが選択トランジスタ(AT)に接続されている半導体メモリセル、および、その製造方法に関するものである。本発明では、ストレージキャパシタは、ソース領域Sまたはドレイン領域Dのための少なくとも1つのコンタクトホールにおいて、コンタクトホールキャパシタ(KK)として形成されている。このような半導体メモリセルは、特にコスト効率よく製造することができ、かつ高集積度を達成できる。  (もっと読む)

(もっと読む)

記憶素子、メモリ回路、半導体集積回路

【解決手段】第1の可変抵抗(5)は、第1の端子(7)と第3の端子(9)との間に接続され、第1の端子(7)と第3の端子(9)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第2の可変抵抗(6)は、第3の端子(9)と第2の端子(8)との間に接続され、第3の端子(9)と第2の端子(8)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第1の端子(7)と第3の端子(9)との間および第3の端子(9)と第2の端子(8)との間に所定のパルス電圧を印加して第1および第2の可変抵抗(5,6)の抵抗値を可逆的に変化させることにより1ビットあるいは多ビットの情報を記録する。 (もっと読む)

集積回路メモリーセル及びその製法

【課題】セルデザインや工程を不必要に複雑化せずにセルサイズを減少させる。

【解決手段】

チャンネル30は、組み合わされた第1電極と第1ソース/ドレーンの半導電性上方延長部を含むことができる。メモリーセルは複数のメモリーセルのアレイを含んでおり、第2電極は複数の電極の中の共通電極である。メモリーセルは、第1電極とデジット線との間に直線導電通路を提供することができ、その通路は垂直トランジスターを通過して延びている。

(もっと読む)

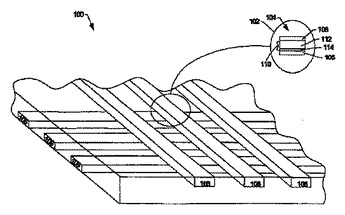

ピラー構造セルのフラッシュメモリ技術

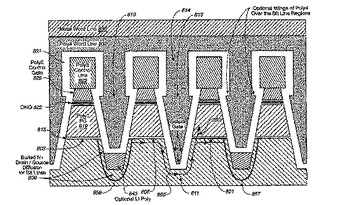

ピラー形不揮発性メモリセル803は各々がトレンチ810によって隣接するメモリセルから絶縁されるメモリセルを各々有している。各メモリセルは基板上に処理層を積層することによって形成される。すなわち、トンネル酸化物層815、ポリシリコンフローティングゲート層819、ONOまたは酸化物層822、ポリシリコンコントロールゲート層825である。ステップの多くの態様が自己整合される。これらのメモリセルのアレイにはより少ない分割しか必要ない。さらに、このメモリセルは、電子がフローティングゲート819に対して直角またはほぼ垂直843に向けられるので、プログラミング特性が増強される。  (もっと読む)

(もっと読む)

フラッシュメモリデバイス

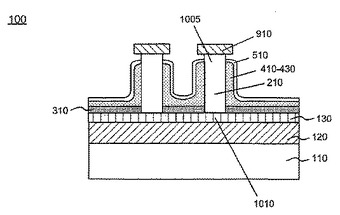

メモリデバイス(100)は、導電構造(210)、複数の誘電層(410−430)、及び、制御ゲート(510)を含む。誘電層(410−430)は導電構造(210)の周りに形成され、制御ゲート(510)は誘電層(410−430)上に形成される。導電構造(210)の一部はメモリデバイス(100)のドレイン領域(1005)として機能し、また、誘電層(410−430)の少なくとも1つは、メモリデバイス(100)の電荷蓄積構造として機能する。誘電層(410−430)は、酸化物−窒化物−酸化物層を含む。  (もっと読む)

(もっと読む)

ブリッジ電界効果トランジスタメモリセル、上記セルを備えるデバイス、および、ブリッジ電界効果トランジスタメモリセルの製造方法

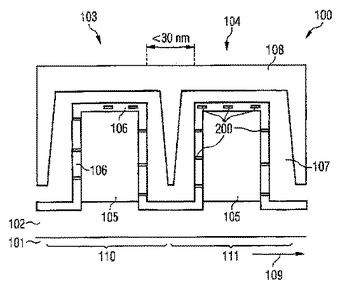

本発明は、第1および第2の各ソース/ドレイン領域、第1および第2の各ソース/ドレイン領域の間に配置されたチャネル領域とを備え、これらの各ソース/ドレイン領域とチャネル領域とが半導体ブリッジに形成されている、ブリッジ電界効果トランジスタメモリセルに関するものである。

本発明のメモリセルは、さらに、半導体ブリッジの少なくとも部分上に堆積されている電荷記憶層と、電荷記憶層の少なくとも一部上の金属性で導電性のゲート領域とを備え、電荷記憶層は、ブリッジ電界効果トランジスタメモリセルに所定の電気的電圧を印加することにより、選択的に、電気的な電荷キャリアが、電荷記憶層に対し導入されるように、または、電荷記憶層から除去されるように配置されている。  (もっと読む)

(もっと読む)

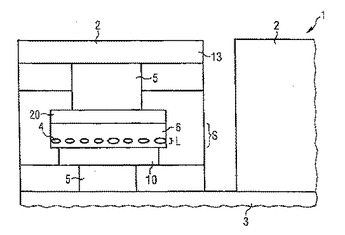

半導体集積メモリーおよび半導体集積メモリーの製造方法

本発明は、2つの電極(10,20)間に配置された記憶媒体(6)を備えた半導体集積メモリー(1)に関する。上記記憶媒体(6)は、例えば相変化媒体であってもよい。記憶媒体(6)は、電流によって第1状態または第2状態に設定される。その結果、情報項目を記憶させることができる。本発明によれば、材料(4)からなる不純物粒子が注入された面(L)が設けられている。その結果、記憶媒体における電流密度が局部的に上昇し、プログラミングのために必要とされるプログラミング電流を低減できる。その結果、相変化媒体を含むメモリー素子の電流消費を低減できる。したがって、相変化媒体を含むメモリー素子を、トランジスタなどの他の部品と共に、最小構造寸法で実施することができ、単一の半導体回路に集積することができ、別個のサブ回路に配置する必要がなくなる。  (もっと読む)

(もっと読む)

自己整合型電荷分離構造NROMフラッシュメモリ

【課題】電荷捕獲領域が重ならずにセルを小さくすることが可能なトランジスタを提供する。

【解決手段】窒化物リードオンリーメモリ(NROM)セルは、窒化物層を有し、前記窒化物層は、トランジスタの中心部の下方に配置されない。前記窒化物層を有するゲート絶縁層は、2つの部分を有する。各部分は、構造分離された(structurally defined and separated)電荷捕獲領域を有する。電荷は、トランジスタの動作方向に応じて、ある特定の捕獲領域に蓄積される。前記ゲート絶縁層の前記2つの部分は、ポリシリコンゲート構造体の中間部分から外側部分を分離する。

(もっと読む)

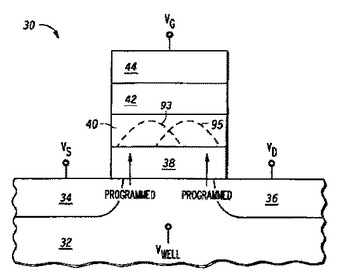

非対称のポケットドープ領域を有するメモリトランジスタおよびメモリユニット

本発明は、特に、ソース領域(S)近傍において、ポケットドープ領域(114)を1つ有しているフラッシュメモリトランジスタ(T11)に関する。上記メモリトランジスタ(T11)は、読み出し処理中において、ロードメモリ状態を妨害することなく機能する。 (もっと読む)

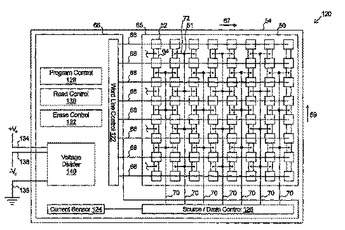

スタガー式ローカル接続構造を持つメモリセルアレイ

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

個別電荷蓄積素子を有するメモリのプログラミング

不揮発性メモリ(100)は、個別電荷蓄積素子(40)を有するトランジスタ群(30)から成るアレイを含む。トランジスタに対しては、2ステップ書き込み方法(60)を使用して書き込みを行ない、この方法では、第1ステップ(68)が低ゲート電圧によるホットキャリア注入(hot carrier injection:HCI)書き込みである。第2ステップ(78)を幾つかのメモリセルに対して選択的に利用して注入電荷分布を変え、トランジスタメモリセル内部の各メモリビットの間の電荷分布間隔を大きくする。書き込みを行なう第2ステップは、書き込み操作に長い余分な時間が加わることなく行われる。一の例では、第1ステップにおいて電子を注入し、そして第2ステップにおいてホールを注入する。2つのステップを実行して分布が形成される結果、蓄積媒体の中心部分の電子電荷が取り除かれる。  (もっと読む)

(もっと読む)

メモリデバイス及びこのデバイスの使用方法ないし製造方法

2つの電極(106、206、108、204)間に制御可能な導電媒体(110)を備える2つの電極で作られるメモリセル(104)を開示する。制御可能な導電媒体(110)は、活性低導電層(112)及び受動層(114)を備える。制御可能な導電媒体(110)は、電界の印加のような外部刺激が供給されると、インピーダンスか変わる。メモリデバイス/セルの作製方法、メモリデバイス/セルの使用方法、及び、メモリテバイス/セルを含むコンピュータのようなテバイスの使用方法も開示する。  (もっと読む)

(もっと読む)

FETベースの磁気ランダム・アクセス・メモリ・デバイス用の自己整列型導電線およびこれを形成する方法

【課題】下部メタライズ線(302)に導電的に結合された横方向の金属ストラップ(326)を含む、電界効果トランジスタ(FET)ベースの磁気ランダム・アクセス・メモリ(MRAM)デバイス用の導電線構造を提供すること。

【解決手段】金属ストラップ(326)上に磁気トンネル接合(MTJ)スタック(316)が形成され、MTJスタック(316)を覆って金属シールド(324)が形成され、金属シールド(324)は金属ストラップ(326)に対して自己整列される。上部メタライズ線(332)は金属シールド(324)に導電的に結合され、金属シールド(324)は上部メタライズ線(332)の形成時にエッチ・ストップとして働く。

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

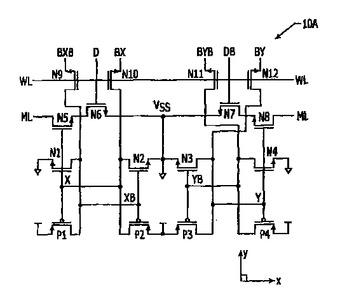

小さいフットプリントおよび効率的なレイアウトアスペクト比を有するターナリ検索機能付きメモリ(TCAM)セル

スケーラビリティを高める効率的なレイアウトアスペクト比および極めて小さいレイアウトフットプリントサイズを有するターナリCAMセルが提供される。また、セルは、ビット線、データ線、マッチ線に対する高い歩留りの相互接続を容易にする高度の対称性も有している。16TターナリCAMセルは、セルの第1の側に隣接して延びる第1および第2の対のアクセストランジスタと、セルの第2の側に隣接して延びる第1および第2の対の交差結合インバータとを有している。また、4T比較回路の第1及び第2の半分部位も設けられている。4T比較回路の第1の半分部位は、第1の対のアクセストランジスタと第1の対の交差結合インバータとの間で延びるように位置されている。同様に、4T比較回路の第2の半分部位は、第2の対のアクセストランジスタと第2の対の交差結合インバータとの間で延びるように位置されている。

(もっと読む)

(もっと読む)

2,381 - 2,400 / 2,405

[ Back to top ]