Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

261 - 280 / 2,405

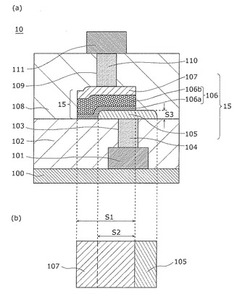

不揮発性記憶素子及びその製造方法並びに不揮発性記憶装置

【課題】不揮発性記憶素子の初期化電圧のばらつきの発生を抑えつつ、従来に比べて初期化電圧の低減を図ることができる抵抗変化型の不揮発性記憶素子を提供する。

【解決手段】第1の層間絶縁層102、下部電極105、上部電極107及び抵抗変化領域106を備え、抵抗変化領域106は積層された第1の抵抗変化領域106bと第2の抵抗変化領域106aを有し、第1の抵抗変化領域106bは第1の遷移金属酸化物で構成され、第2の抵抗変化領域106aは第2の遷移金属酸化物で構成され、第2の遷移金属酸化物の酸素不足度は第1の遷移金属酸化物の酸素不足度より小さく、抵抗変化領域106の上面は上部電極107と接し、抵抗変化領域106の底面は下部電極105及び第1の層間絶縁層102と接し、抵抗変化領域106の底面と下部電極105の接する面の面積は抵抗変化領域106の上面と上部電極107の接する面の面積より小さい。

(もっと読む)

不揮発性記憶装置

【課題】高密度・高信頼の不揮発性記憶装置を実現する

【解決手段】基板の主面に沿って延在するワード線2上に交互に積層された層間絶縁膜11〜15およびゲートポリシリコン層21p〜24pを含む積層体と、積層体上に形成され、ワード線2と直交して延在するビット線3と、ワード線2およびビット線3の交点に設けられたポリシリコンダイオードPDとを有する不揮発性半導体装置を形成する。積層体を貫通してポリシリコンダイオードPDの上面を露出する接続孔の内壁には、前記内壁側から順にゲート絶縁膜9、チャネルシリコン膜8a、8bおよび抵抗変化材料層7を設ける。ワード線2とビット線3とはポリシリコンダイオードPD、チャネルシリコン膜8aおよび8bを介して電気的に接続し、前記内壁に垂直な方向におけるチャネルシリコン膜8a、8bの合計の膜厚は、チャネルシリコン膜8a、8bを空乏化することができる膜厚とする。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

スイッチトランジスタを有しない差動センス増幅器

【課題】回路全体の面積を増やし、製造コストを押し上げるため、センス増幅器に使用される面積を最小限に抑える技術を提供する。

【解決手段】第1のビットライン(BL)に接続された出力と第2のビットライン(/BL)に接続された入力を有する第1のCMOSインバータと、第2のビットライン(/BL)に接続された出力と、第1のビットライン(BL)に接続された入力を有する第2のCMOSインバータと、第1のビットラインおよび第2のビットラインをそれぞれ第1のグローバルビットラインおよび第2のグローバルビットラインに接続するように配列された一対のパスゲートトランジスタを有し、それぞれのCMOSインバータはプルアップトランジスタM21、M22およびプルダウントランジスタM31、M32を備え、パスゲートトランジスタは、プルアップトランジスタ又はプルダウントランジスタによって構成される。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは、ビット線をキャパシタとセルトランジスタの間に形成するため、構造が複雑であったり、回路の特性を犠牲にしたりする必要があり、集積化の面で大きな障害となっている。

【解決手段】キャパシタの一方の電極をビット線に接続し、他方の電極をセルトランジスタのドレインに接続する。また、セルトランジスタのソースは、ソース線に接続される。この結果、例えば、スタック型キャパシタを採用する場合には、キャパシタの電極の一方をビット線の一部とすることができる。ソース線は、半導体基板上に形成された不純物領域や、ワード線に平行な配線を用いることができるので、構造が単純となる。

(もっと読む)

非揮発性メモリ装置及びセンシング方法

【課題】抵抗変化を利用したマルチレベルのデータをセンシングする非揮発性メモリ装置において、読出し動作の回数を減らし、読出し動作の制御に係わる回路の面積を縮小する。

【解決手段】非揮発性メモリ装置は、1つ以上の単位セルを含んでデータの読出し又は書込みが行なわれるセルアレイと、単位セルに格納されたデータに対応するセンシング電圧SAIと基準電圧REFを比較及び増幅して出力し、ビットラインがプリチャージされた以後にセンシングイネーブル信号SENの活性化区間で、単位セルの抵抗値に応じてセンシング電圧がディスチャージされる時間の差を測定し、データをセンシングするセンシング部100とを含む。

(もっと読む)

半導体不揮発性記憶装置およびその製造方法

【課題】高い信頼性で書き込み・消去・読み出しが可能な低コストの半導体不揮発性記憶装置およびその製造方法を提供する。

【解決手段】実施形態の半導体不揮発性記憶装置は、基体Sと、第1の電極2と、機能膜10と、第2の電極50と、を持つ。前記第1の電極2は、前記基体S上に設けられる。前記機能膜10は、前記第1の電極2上に成膜されて記憶媒体をなす。前記第2の電極50は、上面に凸の曲面を有するように、前記機能膜10上または前記機能膜10内に設けられる。

(もっと読む)

半導体装置

【課題】配線基板上にメモリチップとマイコンチップとを搭載してシステムを構成するシステム・イン・パッケージ(SIP)型半導体装置の小型化、高速化を推進する。

【解決手段】配線基板10の上面にマイコンチップ20とメモリチップ30を搭載する際、メモリチップ30の第1チップ辺31a(データ系電極パッド33Dが配置された辺)に沿って配置された配線基板10の第2導電パッド15が、平面視において、マイコンチップ20の第3チップ辺21cの延長線と第4チップ辺21dの延長線との間の領域に位置するようにメモリチップ30を配置することで、マイコンチップ20のデータ系電極パッド23Dとメモリチップ30のデータ系電極パッド33Dとを接続するデータ系配線16Dの長さを最短化する。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置を工程数の増大を抑制しながら製造可能な不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板101上にスペーサ膜104とチャネル半導体膜103とを交互に複数層積層させた積層構造を形成し、積層構造に第1の方向に延在するトレンチを形成する。ついで、トレンチからチャネル半導体膜103を第2の方向にリセスして空隙を形成し、空隙内のチャネル半導体膜103上にトンネル誘電体膜108を形成し、フローティングゲート電極膜109を埋め込む。その後、第1の方向に隣接するメモリセル間でフローティングゲート電極膜109が分離され、チャネル半導体膜103が分離されないように、積層構造を第1の方向に所定の間隔で分割する。また、第2の方向に隣接するメモリセル間でチャネル半導体膜103が分離されるように、積層構造を第2の方向に所定の間隔で分割する。

(もっと読む)

半導体装置

【課題】不揮発性であって、作製が簡単であり、追記が可能な記憶回路を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、複数のトランジスタと、前記トランジスタのソース配線又はドレイン配線として機能する導電層と、前記複数のトランジスタのうちの1つの上に設けられた記憶素子及びアンテナとして機能する導電層とを有し、前記記憶素子は、第1の導電層と、有機化合物層又は相変化層と、第2の導電層とが順に積層された素子であり、アンテナとして機能する前記導電層と前記複数のトランジスタのソース配線又はドレイン配線として機能する導電層とは、同じ層上に設けられていることを特徴とする。

(もっと読む)

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

半導体デバイスの電気的にプログラミング可能なヒューズモジュール

【課題】より小型なeヒューズモジュールを提供する。

【解決手段】半導体デバイスが、eヒューズモジュールおよびプログラミング電流生成器を有する。eヒューズモジュールが電気的にプログラミングするeヒューズ素子(226)のアレイを含む。プログラミング電流発生器が、複数の基準トランジスタ素子(M0〜M6)のセットと、基準トランジスタ素子(M0〜M6)を活性化させて、選択された基準電流を生成するセレクタ(254)と、アレイの選択されたeヒューズ素子(226)に、選択された基準電流に応じたプログラミング電流を印加して、eヒューズ素子(226)の抵抗をプログラミングするカレントミラー(M7、M8、M9)とを有する。

(もっと読む)

半導体メモリ装置及びそのリペア方法

【課題】リペア過程が簡素化された半導体メモリ装置及びそのリペア方法を提供する

【解決手段】半導体メモリ装置200は、複数のメモリセルを含む第1のメモリチップないし第3のメモリチップ210〜230と、第1のリペアチップ240とを備え、第1のリペアチップ240は、第1のメモリチップないし第3のメモリチップ210〜230のそれぞれに含まれた複数のメモリセル212A,212B,・・・のうち、欠陥が発生した任意のメモリセルをリペアするための第1のヒューズ回路ないし第3のヒューズ回路241A,241B,243A,243B,245A,245Bと、メモリチップ210〜230毎に欠陥が発生した任意のメモリセルを代替するための、複数の第1のリダンダンシメモリセルないし第3のリダンダンシメモリセル242A,242B,244A,244B,246A,246Bとを含む。

(もっと読む)

261 - 280 / 2,405

[ Back to top ]