Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

41 - 60 / 2,405

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気的特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】チャネル形成領域、及びチャネル形成領域を挟む低抵抗領域を含む酸化物半導体膜、ゲート絶縁膜、及び上面及び側面を覆う酸化アルミニウム膜を含む絶縁膜が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び酸化アルミニウム膜を含む絶縁膜の上面及び側面の一部に接して設けられる。

(もっと読む)

不揮発性メモリーセル

【課題】種々の回路ブロックを単一の集積回路(IC)に集約するために、不揮発性メモリーブロックをロジック機能ブロックにまとめる。

【解決手段】結合素子と第一のセレクトトランジスターを有している。結合素子は第一の伝導領域において形成されている。第一のセレクトトランジスターは、第一の浮遊ゲートトランジスターおよび第二のセレクトトランジスターに直列的に接続されており、それらは全て第二の伝導領域に形成されている。結合素子の電極および第一の浮遊ゲートトランジスターのゲートは、モノリシックに形成された浮遊ゲートである。第二の伝導領域は第一の伝導領域と第三の伝導領域の間に形成され、第一の伝導領域、第二の伝導領域、および第三の伝導領域は、ウェルである。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグに接続される配線間隔の縮小を可能にする半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板に第1の領域と第2の領域とを定義し、第1の領域に第1のサイズを持つ第1の素子を形成し、第2の領域に、第1のサイズとは異なる第2のサイズを持つ第2の素子を形成し、第1の素子及び第2の素子を覆うように半導体基板上に第1の層間絶縁膜を形成し、第1の領域上の第1の層間絶縁膜を貫通し第1の素子の一部を露出させる第1のコンタクトホールを形成し、第2の領域上の第1の層間絶縁膜を貫通し第2の素子の一部を露出させる第2のコンタクトホールを形成し、第1のコンタクトホール及び第2のコンタクトホールをそれぞれ埋める第1のコンタクトプラグ及び第2のコンタクトプラグを同時に形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

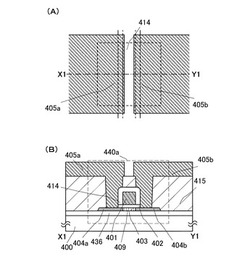

半導体装置及びその製造方法、並びにデータ処理システム

【課題】本発明は、第1の不純物拡散領域と第2の不純物拡散領域との間に位置するピラーを流れるドレイン電流が、隣接するピラーにリーク電流として流れることを防止可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13に立設されたピラー28と、Y方向に延在するように半導体基板13に設けられ、Y方向と交差するX方向において対向するピラー28の第2の側壁を露出する第1の溝16と、ピラー28の第2の側壁の下部に設けられた第1の不純物拡散領域と、ピラー28の上端に設けられた第2の不純物拡散領域と、半導体基板13に内設され、第1の溝16の底16Aに配置された絶縁層14と、を有する。

(もっと読む)

半導体装置、メモリカード、データ処理システムおよび半導体装置の製造方法

【課題】歩留まりや信頼性の低下を招くことなく、隣接セルのフローティング・ゲート間の結合容量を小さくすることができ、隣接セルの書き込み情報の影響を小さくした状態でフローティング・ゲートの電位を制御することが可能なNAND型フラッシュメモリを提供する。

【解決手段】一導電型の半導体材料層表面のチャネル領域上方に第2の絶縁膜12を介して形成されたゲート電極部と、ゲート電極部の上方に前記ゲート電極部と一体形成されたキャパシタ電極部と含むフローティング・ゲート13と、キャパシタ電極部の側面を囲むように第1の絶縁膜12を介して形成されたコントロールゲート10となる第1の電極と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】デバイス特性の向上を図る。

【解決手段】本実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法においては、半導体層10上に、トンネル絶縁膜11を形成する。トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜12を形成する。第1導電膜、トンネル絶縁膜、および半導体層を加工することにより、溝15を形成する。溝内の下部側に、第1犠牲膜17を埋め込む。溝内の第1犠牲膜上に、その上面がトンネル絶縁膜の上面よりも高く、第1導電膜の上面よりも低くなるように、第1犠牲膜よりも高密度な第2犠牲膜18を形成する。第1導電膜上および第2犠牲膜上に、絶縁膜19を形成する。絶縁膜上に制御ゲート電極となる第2導電膜WLを形成する。第2導電膜を加工することにより、第2犠牲膜を露出する。第1犠牲膜および第2犠牲膜を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置

【課題】半導体装置のI/O系および非I/O系の電源およびGNDをバランス良く強化して、低電圧動作性能および高速動作性能を向上させること。

【解決手段】配線基板2の一面は、接続パッド6Aの列を取り囲むように形成され、かつVSS用接続パッド6A−1と配線16を介して接続されたVSS用面状導体パターン18を備える。配線基板2の他面は、複数のVSSQ用外部端子7−3を連結するように配置されたVSSQ用面状導体パターン21と、複数のVDDQ用外部端子7−4を連結するように配置されたVDDQ用面状導体パターン22とを備える。

(もっと読む)

半導体素子及びその形成方法

【課題】ビットラインを容易に形成することができ、ビットライン工程マージンを増加させ、さらに隣接したビットライン間のキャパシタンスを減少させる半導体素子及びその形成方法を提供する。

【解決手段】本発明に係る半導体素子は、半導体基板10で一方向に延長され、垂直チャンネル領域12b,14bを含む第1及び第2ピラー12,14と、第1及び第2ピラー12,14の内部で垂直チャンネル領域12b,14bの下部に位置する第1ビットライン22と、第1ビットライン22を含む第1ピラー12及び第2ピラー14の間に位置する絶縁膜32とを含む。

(もっと読む)

3次元不揮発性メモリ素子及びその製造方法

【課題】消去動作の際、充分な量の正孔を生成させて消去特性を確保することができる3次元不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】基板から突出されたチャンネル膜と、チャンネル膜に沿って積層された複数のメモリセルと、チャンネル膜の一側端と繋がれたソースラインと、チャンネル膜の他側端と繋がれたビットラインと、チャンネル膜の一側端とソースラインとの間に介在されて、Pタイプの不純物がドープされた第1ジャンクションと、チャンネル膜の他側端と前記ビットラインとの間に介在されて、Nタイプの不純物がドープされた第2ジャンクションと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホールの側壁に制御性良く傾斜を形成することで、コンタクトプラグにボイドが形成されることを抑制する。

【解決手段】絶縁膜10に第1のコンタクトホール(破線部)を形成する工程と、第1のコンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施して内壁が傾斜した第2のコンタクトホール13を形成する工程と、第2のコンタクトホール内にコンタクトプラグを形成する工程とを有する。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】放射線耐性能力をさらに向上することができる半導体装置を提供する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

(もっと読む)

可変抵抗素子を備える不揮発性メモリセル及び不揮発性半導体記憶装置

【課題】 検知マージンを大きくして可変抵抗素子の抵抗状態をより正しく検知することができ、且つ、面積低減によりコスト抑制を図ることができる不揮発性メモリセル及び不揮発性半導体記憶装置を提供する。

【解決手段】 第1電極と第2電極の間に第1可変抵抗体R1を挟持してなる第1可変抵抗素子RD1と、第3電極と第4電極の間に第2可変抵抗体R2を挟持してなる第2可変抵抗素子RD2と、ドレイン端子が、第2電極と第4電極に、ゲート端子がワードラインに、ソース端子がコモンラインCLに夫々接続されたトランジスタTと、を備え、第1電極材料の仕事関数が第2電極材料の仕事関数より大きい値に、第3電極材料の仕事関数が第4電極材料の仕事関数より小さい値に設定されるか、または、第1電極材料の仕事関数が第2電極材料の仕事関数より小さい値に、第3電極材料の仕事関数が第4電極材料の仕事関数より大きい値に設定される。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】ジルコニウムを含ませた酸化物半導体材料は結晶化しやすい材料とすることができ、成膜直後において、結晶構造を有する酸化物半導体膜を形成することができる。従って、酸化物半導体膜の成膜後の加熱処理を省略することができるため、量産に適したプロセスである。具体的には、少なくともインジウムと亜鉛を含む酸化物半導体材料に、4族元素の一つであるジルコニウムを含ませる。少なくともインジウムと亜鉛を含む酸化物半導体材料にジルコニウムを含ませた酸化物半導体材料膜(InZrZnOX膜)を提供する。

(もっと読む)

半導体装置

【課題】低電圧動作が可能なSRAMをそのセル面積の増加を抑えて実現する。

【解決手段】第1方向Sに並ぶP型ウェル領域20、N型ウェル領域30、P型ウェル領域40に、第2方向Tに隣接するメモリセル1aが形成される。各メモリセル1aは、P型ウェル領域20,40に形成されたトランスファトランジスタTf1,Tf2及びドライバトランジスタDr1,Dr2、N型ウェル領域30形成されたロードトランジスタLo1,Lo2を備える。SRAM1では、第2方向Tに隣接するメモリセル1aの、互いのトランスファトランジスタTf1のゲート電極がワード線WL1に、互いのトランスファトランジスタTf2のゲート電極がワード線WL2に、それぞれ電気的に接続される。ワード線WL1はP型ウェル領域20に、ワード線WL2はP型ウェル領域40に、それぞれ電気的に接続される。

(もっと読む)

41 - 60 / 2,405

[ Back to top ]