Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

121 - 140 / 2,405

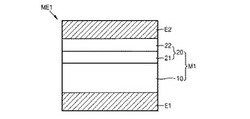

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

情報記憶素子

【課題】多値記録が可能で、アモルファスと結晶との相混合比を制御する方式に比較して、パルス電流条件のマージンが広い情報記憶素子を提供する。

【解決手段】相変化材料にそれぞれ形状の異なるパルス電流を流すことによって、アモルファス状態、微細な結晶粒からなる固相結晶、粒径の大きな結晶状態からなる溶融結晶の3状態を形成し、従来に比較してパルス電流条件のマージンが広く、信頼性の高い多値記録が可能な情報記憶素子を実現する。3状態を形成するには、相変化材料の組成を変更したり、他の元素を添加したりすることによって、溶融後の再結晶化速度および抵抗を制御する。

(もっと読む)

相変化メモリ

【課題】三次元構造を有する相変化メモリの熱ディスターブを抑制する。

【解決手段】三次元構造を有する相変化メモリにおいて、選択用MOSトランジスタのゲート絶縁膜として、高い熱伝導率を有する材料を使用し、相変化記録膜からSiチャネル層に伝達する熱を良好にゲート電極に拡散させる。これにより、記録ビットから発生する熱が非選択の隣接ビットに拡散し、隣接ビットのデータを消去する熱ディスターブを抑制する。高い熱伝導率を有するゲート絶縁膜材料としては、BN、Al2O3、AlN、TiO2、Si3N4、ZnOなどを挙げることができる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

情報格納装置

【課題】より容易な方法で集積度を向上させた情報格納装置を提供する。

【解決手段】本発明の情報格納装置は、基板と、基板上のゲートライン構造体を含むトランジスターと、少なくとも一部が基板内に埋め込まれてトランジスターの活性領域を定義する導電性分離パターン(conductive isolation patterns)と、を有し、導電性分離パターンは、互いに電気的に連結される。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】書き込み特性を向上することが可能な不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】複数のゲート電極構造13は、半導体基板11上に形成されたゲート絶縁膜12、電荷蓄積層14、ゲート間絶縁膜15、第1制御ゲート16、及び前記第1制御ゲートより幅が広い第2制御ゲート電極17を有する。絶縁膜19は、制御ゲート電極17間及び制御ゲート電極より上方に形成された空隙19を有する。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】短チャネル効果が抑制され、微細化を実現しつつ、安定した電気的特性を付与する半導体装置を提供する。また、上記半導体装置を作製する。

【解決手段】酸化物絶縁層に設けたトレンチに、トレンチに沿って成膜される酸化物半導体膜と、酸化物半導体膜と接するソース電極及びドレイン電極と、酸化物半導体膜上のゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有する半導体装置(トランジスタ)を設ける。該トレンチは下端コーナ部に曲面を有し、側部が酸化物絶縁層上面に対して略垂直な側面を有する。また、トレンチの上端の幅がトレンチの側面の幅の1倍以上1.5倍以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】抵抗変化型不揮発メモリ装置100は、基板、金属層、下部電極、抵抗変化層、上部電極、及びスペーサー部を備える。金属層(金属密着層142)は、半導体基板102上に設けられる。下部電極144は、金属密着層142上に設けられていて、金属密着層142と接続する。上部電極148は、下部電極144上にあって、下部電極144と対向する位置に設けられている。抵抗変化層146は、下部電極144と上部電極148との間に設けられていて、下部電極144と上部電極148とが重なる領域よりも外側に延在している。スペーサー部150は、抵抗変化層146のうち外側に延在している部分と金属密着層142との間に設けられる。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】生産性の高い不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態は、基板の主面に対して垂直な第1軸に沿って積層された複数の電極膜と、複数の電極膜を第1軸に沿って貫通する複数の半導体層と、複数の電極膜と半導体層との間に設けられたメモリ膜と、を含む不揮発性半導体記憶装置の製造方法であって、複数の電極膜となる複数の第1膜と複数の第2膜とを交互に積層して、第1積層体を形成する工程と、第1軸に沿い複数の第1膜を支持する支持部を形成する工程と、第1積層体を第1軸に沿って貫通する第1の孔を形成し、第1の孔を介して第2膜を除去し、複数の第1膜どうしの間に間隙が形成された第2積層体を形成する工程と、第2積層体の複数の第1膜を第1軸に沿って貫通する貫通孔を形成する工程と、複数の貫通孔の中に、メモリ膜及び半導体層を埋め込む工程と、を備える。

(もっと読む)

半導体装置

【課題】抵抗変化型記憶素子を用いた半導体装置の耐タンパ性を向上させること。

【解決手段】半導体装置は、1ビットのセルデータを記憶するユニットセル(10)と、制御回路(100)とを備える。ユニットセル(10)は、n個(nは2以上の整数)の抵抗変化型記憶素子(31)を備える。それらn個の抵抗変化型記憶素子(31)のうち少なくとも1つが、セルデータが記録される有効素子(40)である。セルデータの読み出し時、制御回路(100)は、少なくとも有効素子(40)を選択し、有効素子(40)に記録されているデータをセルデータとして読み出す。

(もっと読む)

121 - 140 / 2,405

[ Back to top ]