Fターム[5F083GA10]の内容

Fターム[5F083GA10]に分類される特許

61 - 80 / 1,175

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の動作電力を低減する。

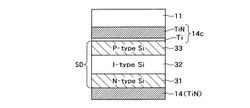

【解決手段】不揮発性半導体記憶装置は、TiN層からなる上部電極TE及びバリアメタルBM1,BM2と、金属酸化物HfOx層を有する可変抵抗素子VRと、ポリシリコン層及びポリシリコン層と金属酸化物HfOx層との界面に形成されたSiGe層を有する下部電極BEと、バリアメタルBM1と、NIP層からなるバイポーラ型の電流整流素子Diとを直列接続したメモリセルMCを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】エッチング加工がし易く、データ保持の劣化を抑制する。

【解決手段】実施形態の不揮発性半導体記憶装置は、下地層と、前記下地層の上に設けられた積層体であって、それぞれ交互に積層された複数の電極層と複数の絶縁層と、前記複数の電極層と前記複数の絶縁層との間に設けられた拡散抑制層と、を有する前記積層体と、前記積層体を積層方向に貫通するホールの側壁に設けられたメモリ膜と、前記メモリ膜の内側に設けられたチャネルボディ層と、を備える。前記複数の電極層のそれぞれは、第1の不純物元素を含む第1の半導体層である。前記拡散抑制層は、前記第1の不純物元素とは異なる第2の不純物元素を含む第2の半導体層である。前記拡散抑制層は、前記第1の不純物元素の拡散を抑制する効果を有する膜である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性および読み出し速度の向上を図ることができる半導体記憶装置及びその製造方法を提供する。

【解決手段】電極膜WLと層間絶縁膜14を交互に複数積層して積層体を形成する工程と、前記積層体の積層方向に延びる複数の貫通孔18を形成する工程と、前記貫通孔の内部に電荷蓄積膜23と、絶縁膜24aと、ゲルマニウムを用いた第1の膜25と、アルミニウムを用いた第2の膜27を形成する工程と、置換熱処理で、前記第1の膜と前記第2の膜を置換し前記第2の膜の前記絶縁膜とは反対の側にゲルマニウムを成長させて半導体ピラーSPを形成する工程と、前記積層体の上方に配線を形成する工程と、前記置換された第2の膜を選択的に除去することで、前記絶縁膜と前記半導体ピラーとの間に空隙24bを形成する工程と、を備えている。前記半導体ピラーの上端部は、前記積層体の上方に形成された前記配線により支えられる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

メモリ装置

【課題】大容量化が容易であり、高収率且つ高信頼性を有する半導体メモリ装置が提供される。

【解決手段】本発明に従うメモリ装置は、記憶素子と前記記憶素子にデータを書き込むか、又は読み出す周辺回路を含む第1半導体チップ、及び外部と前記第1半導体チップとの間で交換されるデータ又は信号の入出力機能を遂行する第2半導体チップを含み、本発明のその他の特徴に従うメモリ装置は、外部とデータ又は信号を交換するための入出力回路チップ、及び各々前記入出力回路チップから提供される信号に応答して前記データを格納するか、或いは内部に格納されたデータを読み出して前記入出力回路チップへ出力する、垂直方向に積層される複数のコアチップを含む。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、工程数削減によるコスト低減を図れる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、第2の被加工膜の上に第2の方向に延びる複数の第2の芯材膜であって、第1のスペースを隔てて第1の方向に並んだ第1の配列部と、第1のスペースよりも大きな第2のスペースを第1の方向に隔てて配置された第2の配列部とを有し、第2のスペースがループ部の上に位置する第2の芯材膜を形成する工程と、第2の芯材膜を除去し第2の被加工膜上に第2のスペーサー膜を残す工程と、第2のスペーサー膜をマスクにしたエッチングにより、第1の配列部の下の第2の被加工膜を、第2の方向に延びる第2のラインパターンを含む第2のラインアンドスペースパターンに加工するとともに、第2のスペースの下の第2の被加工膜と、第1の被加工膜のループ部とを除去する工程とを備える。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】上下2層のメモリセル構成部材を一括して加工してメモリセルを形成する際に、引き出し部でのパターンの撚れを抑制する不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、メモリセル部100は、ワード線WLとビット線BLの交差位置に、ワード線WLとビット線BLに挟持されるようにメモリセルMCが配置されるメモリ層とを有する。コンタクト部110は、メモリセル部100のワード線WLとビット線BLの延在方向に配置される。また、ワード線引き出し部120Wは、メモリセル部100とワード線コンタクトWCとをワード線WLによって接続し、ビット線引き出し部120Bは、メモリセル部100とビット線コンタクトBCとをビット線BLによって接続する。ワード線およびビット線引き出し部120W,120Bを構成するワード線WLとビット線BLの直下のメモリ層に対応する層にダミーパターンDPを備える。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】メモリストリングは、複数の第1導電層、メモリゲート絶縁層、及び半導体層を有する。複数の第1導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、メモリトランジスタのゲートとして機能する。半導体層は、複数の第1導電層と共にメモリゲート絶縁層を一方の側面で挟み、半導体基板に対して実質的に垂直方向に延び、メモリトランジスタのボディとして機能する。第1キャパシタは、複数の第2導電層を有する。複数の第2導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、第1キャパシタの電極として機能する。制御回路は、複数の第1導電層に印加される電圧に応じて、複数の第2導電層の各々に印加する電圧を制御し、これにより第1キャパシタの容量を変化させる。

(もっと読む)

不揮発性記憶装置

【課題】実施形態は、抵抗変化素子と、それを安定して双方向動作させることが可能な電流制御素子と、を有するメモリセルを備えた不揮発性記憶装置を提供する。

【解決手段】実施形態に係る不揮発性記憶装置は、第1の信号線と、前記第1の信号線と非平行な第2の信号線と、前記第1の信号線と前記第2の信号線とに接続されたメモリセルを備える。さらにメモリセルは、前記第1の信号線と前記第2の信号線との間を流れる電流により抵抗値が変化する抵抗変化部と、前記電流を制御する電流制御部と、を含む。そして、前記抵抗変化部と前記電流制御部とが、前記第1の信号線と前記第2の信号線との間に直列に配置され、前記電流制御部は、第1の導電体と、前記第1の導電体から離間して設けられた第2の導電体と、前記第1の導電体と前記第2の導電体と間の対向する2つの面の間に設けられた絶縁層と、を有する。前記2つの面のそれぞれは、前記第1の信号線から前記第2の信号線に向かう方向に直交する平面に対して、平行な部分と、交差する部分と、を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の加工精度をより向上させる。

【解決手段】実施形態によれば、不純物含有領域と、被エッチング領域と、を有する半導体層を形成し、それぞれの表面から内部にかけて第1絶縁層を形成し、第1絶縁膜を介して、半導体層上に複数の電極層を含む積層体を形成し、積層体に、被エッチング領域に達し第2絶縁層を挟む一対のホールを形成し、被エッチング領域を一対のホールを通じて除去し、半導体層に一対のホールのそれぞれの下端とつながった空間部を形成し、一対のホールのそれぞれの側壁に、メモリ膜を形成し、空間部の内壁に第4絶縁層を形成し、一対のホールのそれぞれの側壁と空間部の内壁とに形成されたメモリ膜の表面に、チャネルボディ層を形成する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】寄生抵抗がより低いチャネルボディ層を有する不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置は、半導体層と、第1絶縁層が表面に設けられた第2絶縁層と、第3絶縁層と、第2絶縁層および第3絶縁層の上に、電極層と絶縁膜とを有する第1積層体と、第1積層体の積層方向に貫通し第2絶縁層に達する一対の第1ホールのそれぞれの側壁に設けられたメモリ膜と、メモリ膜の内側に設けられた第1チャネルボディ層と、層間絶縁膜と選択ゲートとを有する第2積層体と、一対の第1ホールのそれぞれ上端と連通し、第2積層体の積層方向に貫通する第2ホールの側壁に設けられたゲート絶縁膜と、ゲート絶縁膜の内側に設けられた第2チャネルボディ層と、第1積層体の下側に設けられた連結部と、一対の第1ホールの間に挟まれ、第1積層体の表面から第1絶縁層に達する第4絶縁層と、を備える。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】読み出し速度の向上を図ることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、交互に積層して設けられた複数の電極膜及び層間絶縁膜を有した積層体と、前記積層体を積層方向に貫く半導体ピラーと、前記半導体ピラーと前記電極膜との間に設けられた電荷蓄積膜と、前記半導体ピラーの側面に設けられた添加部と、を備えている。そして、前記半導体ピラーは、ゲルマニウムを含む半導体材料を用いて形成され、前記添加部は、酸化アルミニウムを用いて形成されている。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造工程を簡略化出来る半導体記憶装置の製造方法を提供すること。

【解決手段】実施形態の半導体記憶装置の製造方法は、第1配線層42及び前記第1メモリセル層43〜47をパターニングすることにより、第1方向D1に沿ったストライプ形状の第1構造を第1領域20に形成し、第2構造DM1を第2領域21に形成することと、第1構造及び前記第2構造DM1上に順次形成した第2配線層54及び第2メモリセル層55〜59をパターニングすることにより、第1方向D1と異なる第2方向D2に沿ったストライプ形状を有し、且つ第2領域21における第2構造DM1直上の領域で折り返すパターンを有する第3構造を第1領域20に形成することと、第3構造の折り返す部分における第2配線層54及び第2メモリセル層55〜59、並びにその直下に位置する第1メモリセル層43〜47を除去することとを具備する。

(もっと読む)

半導体記憶装置の製造方法

【課題】スループットの向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板上に、不純物濃度が第1濃度である第1シリコン層35、不純物濃度が第1濃度より低い第2濃度である第1犠牲層、不純物濃度が第1濃度である第2シリコン層35、および不純物濃度が第2濃度である第2犠牲層が順に積層された積層体を形成する工程と、積層体上に、第1絶縁膜を形成する工程と、積層体および第1絶縁膜内に、溝22を形成する工程と、溝内に、不純物濃度が第1濃度より低く、第2濃度より高い第3濃度である第3犠牲層90を埋め込む工程と、ウェットエッチングにより、溝内の第3犠牲層を上面から後退させて除去することで、第1犠牲層および第2犠牲層の端面を後退させる工程と、第1シリコン層および第2シリコン層の端面を第1犠牲層および第2犠牲層の端面に沿ってエッチングする工程とを具備する。

(もっと読む)

61 - 80 / 1,175

[ Back to top ]