Fターム[5F083GA11]の内容

Fターム[5F083GA11]の下位に属するFターム

低雑音化 (360)

保護素子 (38)

誤書込防止 (328)

誤消去防止 (100)

過消去(オーバーイレース)防止 (41)

ソフトエラー防止 (115)

局所的電界緩和 (168)

疲労特性劣化の防止 (791)

カップリング比増大 (255)

ラッチアップ防止 (24)

高耐圧化 (134)

不純物混入、拡散防止 (686)

Fターム[5F083GA11]に分類される特許

1 - 20 / 1,881

半導体装置及びその製造方法

メタルブリッジ型記憶装置

半導体装置の製造方法

半導体装置及びその製造方法

半導体装置及びその製造方法

液体噴射ヘッド、液体噴射装置及び圧電素子

スイッチ素子を有するメモリシステム

半導体集積回路

不揮発性半導体記憶装置及びその製造方法

【課題】 書き込み動作及び消去動作の両方の特性向上を図る。

【解決手段】 実施形態による不揮発性半導体記憶装置は、半導体基板11と、半導体基板上に形成されたゲート絶縁膜12と、ゲート絶縁膜上に形成され、13族元素であるP型不純物を含有するポリシリコンからなり、下部膜13aと下部膜上に積層された上部膜13bとを有するフローティングゲート電極13と、フローティングゲート電極上に形成された電極間絶縁膜16と、電極間絶縁膜上に形成されたコントロールゲート電極17と、を具備し、上部膜におけるP型不純物の濃度又は活性化濃度は、下部膜におけるP型不純物の濃度又は活性化濃度より高い。

(もっと読む)

液体噴射ヘッド及び液体噴射装置並びに圧電素子

【課題】環境負荷が小さく、歪量が大きい液体噴射ヘッド、液体噴射装置及び圧電素子を提供する。

【解決手段】圧電体層70と圧電体層70に設けられた電極60,80とを具備する圧電素子300を備え、圧電体層70は、ビスマス、鉄、バリウム及びチタンを含みペロブスカイト構造を有する複合酸化物からなり、圧電体層70に駆動電圧Vaを印加したときの変位量をZmax、その後印加電圧を0Vにしたときの変位量をZ0としたとき、(Zmax−Z0)/Vaが70pm/V以上且つ比誘電率が700以下である。

(もっと読む)

半導体記憶装置

【課題】不揮発性メモリ部内蔵のSRAMの特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1とビット線BLとの間に抵抗変化層Rを有するReRAM部RM1を設け、アクセストランジスタAcc2とビット線/BLとの間に抵抗変化層Rを有するReRAM部RM2を設ける。SRAM通常動作期間の終了時において、例えば、蓄積ノードAに低電位(L=0V)、蓄積ノードBに高電位(H=1.5V)が保持されている場合、ReRAM部RM1をオン状態(ON)とし、ReRAM部RM2をオフ状態(OFF)とすることで、SRAMの保持データをReRAM部へ書き込み、再び、SRAM通常動作となった場合には、蓄積ノードAおよびBに対応するデータ書き戻すとともに、ReRAM部RM1、RM2の双方をオン状態に(リセット)する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性の均一化を図る。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に設けられた積層体と、絶縁膜と、チャネルボディと、半導体層とを備えている。前記積層体は、選択ゲートと、前記選択ゲート上に設けられた絶縁層とを有する。前記絶縁膜は、前記積層体を積層方向に貫通して形成されたホールの側壁に設けられている。前記チャネルボディは、前記ホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲む。前記半導体層は、前記チャネルボディが前記ホールを閉塞する部分より上の前記ホール内に、前記チャネルボディと同材料で連続して埋め込まれている。

(もっと読む)

半導体装置の製造方法

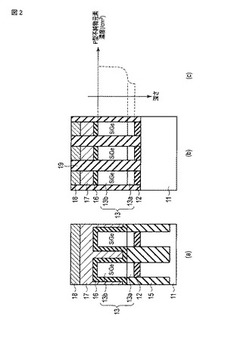

【課題】縦型トランジスタにおける上部拡散層の深さ方向のばらつきを低減することのできる半導体装置の製造方法を提供する。

【解決手段】本発明は表面が平坦なシリコン層からなる上部拡散層11を形成しようとするものであり、具体的には、ファセットを有するシリコン層を選択的に過剰成長させた後、層間絶縁膜7表面に形成されたシリコン層をCMPで擦り切ってシリコン層の表面を平坦化する。シリコン層の成長は、シリコン層を単結晶シリコンで選択的にエピタキシャル成長させる。この場合、ファセットが生じるので、最も成長が遅いファセットが層間絶縁膜表面より上方に位置するまで充分過剰に成長させる。

(もっと読む)

1 - 20 / 1,881

[ Back to top ]