Fターム[5F083GA19]の内容

Fターム[5F083GA19]に分類される特許

1 - 20 / 168

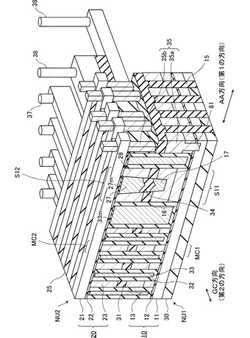

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】パンチスルーを抑制しつつ、セレクトゲート電極からのフリンジ電界を低減する。

【解決手段】空隙AG1は、制御ゲート電極8およびセレクトゲート電極12下に潜るようにしてトレンチ2に沿って連続して形成され、セレクトゲートトランジスタのドレイン領域間に達している。そして、セレクトゲートトランジスタのドレイン領域間において、空隙AG1が埋め戻し絶縁膜RBにて埋め戻されている。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】酸化物半導体層、及びチャネル保護層を覆うようにソース電極層、及びドレイン電極層となる導電膜を形成した後、酸化物半導体層、及びチャネル保護層と重畳する領域の導電膜を化学的機械研磨処理により除去する。ソース電極層、及びドレイン電極層となる導電膜の一部を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、チャネル保護層を有することにより、導電膜の化学的機械研磨処理時に当該酸化物半導体層に与える損傷、または膜減りを低減できる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

半導体装置、メモリカード、データ処理システムおよび半導体装置の製造方法

【課題】歩留まりや信頼性の低下を招くことなく、隣接セルのフローティング・ゲート間の結合容量を小さくすることができ、隣接セルの書き込み情報の影響を小さくした状態でフローティング・ゲートの電位を制御することが可能なNAND型フラッシュメモリを提供する。

【解決手段】一導電型の半導体材料層表面のチャネル領域上方に第2の絶縁膜12を介して形成されたゲート電極部と、ゲート電極部の上方に前記ゲート電極部と一体形成されたキャパシタ電極部と含むフローティング・ゲート13と、キャパシタ電極部の側面を囲むように第1の絶縁膜12を介して形成されたコントロールゲート10となる第1の電極と、を有する。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を提供する。また、バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を具備する半導体装置を提供する。

【解決手段】インジウム、ランタン、亜鉛及び酸素を有する結晶構造の酸化物半導体膜とする。また、当該結晶構造において、ランタンは酸素が6配位した構造とし、インジウムは酸素が5配位した構造とする。酸化物半導体膜の結晶構造中にランタンを用いることで、インジウム、ガリウム、亜鉛及び酸素を有する結晶構造の酸化物半導体膜よりもバンドギャップが大きく、結合エネルギーを大きくした酸化物半導体膜とすることができる。また、該酸化物半導体膜を用いた半導体装置の特性を向上させることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】隣接セルの書き込み閾値の変動を抑制すると共に、制御ゲート電極膜とシリコン基板との間のリーク電流を低減して消去特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。前記電極間絶縁膜は、第1のシリコン酸化膜、第1のシリコン窒化膜、第2のシリコン酸化膜および第2のシリコン窒化膜を積層形成した積層構造を有する。そして、前記電極間絶縁膜は、前記第2のシリコン酸化膜のうちの前記素子分離絶縁膜の上面上の部分の膜厚が前記電荷蓄積層の上面上の部分の膜厚より薄くなるように構成した。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高電界リークを低減して、書き込み特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。そして、前記電極間絶縁膜は、シリコン窒化膜もしくは高誘電率膜を2層のシリコン酸化膜で挟んだ積層構造または高誘電率膜とシリコン酸化膜の積層構造及び前記積層構造と前記制御電極層の間に形成された第2のシリコン窒化膜を有し、前記第2のシリコン窒化膜のうちの前記電荷蓄積層の上面上の部分を消失させた。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、コントロールゲートとフローティングゲートとの間のカップリング容量比を増大させることができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。第1の絶縁膜は、半導体基板上に形成されている。フローティングゲートは、第1の絶縁膜上に設けられた第1のフローティングゲート部分、第1のフローティングゲート部分上に設けられた中間絶縁膜、および、中間絶縁膜上に設けられた第2のフローティングゲート部分を含み、電荷を蓄積可能に構成されている。第2の絶縁膜は、フローティングゲートの上面および側面に設けられている。コントロールゲートは、第2の絶縁膜を介してフローティングゲートの上面および側面に対向し、フローティングゲートの電圧を制御する。フローティングゲートの側面において中間絶縁膜が第1および第2のフローティングゲート部分に対して窪んでいる。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体装置

【課題】1T−DRAMにおいて、高いGIDL電流は、主にPN接合でのリーク電流によるものであり、データ保持時にリーク電流が発生する原因にもなり、DRAMにおける電荷保持時間を低下させている。

【解決手段】ドレイン拡散層のうちゲート電極とオーバーラップする部分を、不純物濃度の異なる2つの部分に分けている。これら2つの部分のうち、不純物濃度がより低い一方の部分では、ボディ部に隣接しており、電界が低減されるためリーク電流が抑制される。また、不純物濃度がより高い他方の部分では、ボディ部から絶縁されており、ゲート絶縁層との界面において比較的大きなトンネル効果が得られる。その結果、GIDL電流を増大しつつ、PN接合によるリーク電流を抑制し、データ保持時間を増大させることが可能となっている。

(もっと読む)

半導体装置

【課題】消去特性と消去ディスターブ特性との双方を向上することが可能な、MONOS型メモリセルなどの半導体装置を提供する。

【解決手段】半導体基板SUBの主表面に形成される第1のゲート電極CGと、主表面上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる絶縁膜ONOと、第1および第2のゲート電極CG,MGの真下のチャネル領域を挟むように、主表面に形成される1対のソース/ドレイン領域NR1,NR2とを備える。上記ソース領域NR1は、第1のソース領域N11および第2のソース領域N12を含んでいる。上記第2のソース領域N12は第1のソース領域N11よりも主表面から深い領域に形成されている。上記第1のソース領域N11と第2のソース領域N12とに含まれる不純物の材質が異なっている。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

メモリセルキャパシタ構造におけるメモリセルキャパシタプレートの形成方法

【課題】酸素にさらされても絶縁膜を形成しない材料からメモリセルキャパシタプレートを製造するための形成方法を提供する。

【解決手段】メモリセルキャパシタプレートの形成方法は、犠牲層を堆積する工程と、その犠牲層内に開口部を形成する工程とを含む。続いて、酸素にさらされても相当の導電性を維持する導電性料を含む電極材料層702を、犠牲層の上面に堆積し、開口部の少なくとも一部を充填する。次に、電極材料層702の一部を少なくとも犠牲層の上面と同じ略同じ高さにまで除去することによりメモリセルキャパシタプレートの上面を画定し、その後、犠牲層を除去する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】浮遊ゲートと制御ゲートとの間におけるリークを抑制することができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた浮遊ゲートと、前記浮遊ゲート上に設けられたリーク抑制部と、前記リーク抑制部上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられた制御ゲートと、を備える。前記リーク抑制部の誘電率は、前記ゲート間絶縁膜の誘電率よりも高くなっている。

(もっと読む)

1 - 20 / 168

[ Back to top ]