Fターム[5F083GA25]の内容

Fターム[5F083GA25]に分類される特許

141 - 160 / 686

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

不揮発性メモリセル、抵抗可変型不揮発性メモリ装置および不揮発性メモリセルの設計方法

【課題】電圧を印加する前の抵抗と印加した後の抵抗との抵抗比が大きい酸化物層を備える不揮発性メモリセルを提供を実現する。

【解決手段】本発明の不揮発性メモリセル1は、電極10と、電極20と、電極10と電極20との間に配置された酸化物層30とを備え、電極間に電圧あるいは電流を印加することで抵抗が変化する。そして、電極10を陽極として電極間に電圧あるいは電流を印加したとき、電極10と酸化物層30との界面において、電極10は、酸化物層30における電極10に隣接する酸素原子とともに、酸化物層30から離れる方向に移動し、電極10および酸素原子の上記移動によって、酸化物層30のエネルギーギャップの大きさが変化する、あるいは、フェルミエネルギー近傍に状態密度の変化が生じる。

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 トンネル絶縁膜を有するトランジスタにおいて、トンネル絶縁膜の電子トラップが増加することによるトランジスタの電気特性の劣化を抑制することが可能な半導体装置及びその製造方法を提供する

【解決手段】 実施形態に係る半導体装置は、半導体基板1と、前記半導体基板1上に形成されたトンネル絶縁膜2を含むトランジスタと、前記トランジスタの上方に形成されたBを含むシリコン窒化膜7と、を備える。前記シリコン窒化膜7は、B−N結合を有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体記憶装置におけるトランジスタの特性向上と、キャパシタのリーク電流特性の両方を改善し、高信頼、高歩留のデバイスを提供する。

【解決手段】窒化チタンからなる下部電極102上に酸化ジルコニウムを主成分とする誘電体膜103を有するキャパシタにおいて、微結晶状態の酸化ジルコニウムを主成分とする誘電体膜を成膜し、2次的な結晶粒成長を伴わない条件でチタン化合物を主成分とする第一の保護膜110を形成し、その後、上部電極111を形成することで、上部電極形成時に伴う熱処理を行っても、またトランジスタの界面準位を低減する水素アニールを行っても、リーク電流の増大を抑制できる。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

スパッタターゲット

【課題】バリア膜としての特性や品質に優れるTi−Al−N膜を再現性よく形成することを可能にしたスパッタターゲットを提供する。

【解決手段】Alを1〜30原子%の範囲で含有するTi−Al合金により構成されたスパッタターゲットであって、前記Ti−Al合金中のAlは、Ti中に固溶した状態、およびTiと金属間化合物を形成した状態の少なくとも一方の状態で存在しており、かつ前記Ti−Al合金の平均結晶粒径が500μm以下であると共に、ターゲット全体としての結晶粒径のバラツキが30%以内、前記Ti−Al合金の平均酸素含有量が1070ppmw以下であることを特徴とするスパッタターゲット。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ膜の薄膜化を図るも、リーク電流の増加を抑止しつつ大きな分極反転量を確保し、薄いキャパシタ膜を有する信頼性の高いキャパシタ構造を備えた半導体装置を実現する。

【解決手段】FeRAMの強誘電体キャパシタ構造を形成するに際して、下部電極膜を形成し(ステップS1)、第1の強誘電体膜を形成し(ステップS2)、第1の熱処理で第1の強誘電体膜を結晶化し(ステップS3)、第1の強誘電体膜上にアモルファス状態の第2の強誘電体膜を形成し(ステップS4)、第2の強誘電体膜上にアモルファス状態のSRO膜を形成し(ステップS5)、SRO膜上に第1の上部電極膜を形成し(ステップS6)、第2の熱処理で第2の強誘電体膜及びSRO膜を結晶化する(ステップS7)。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の形成を1000℃以上で行う場合に、Grow−in欠陥の発生の抑制と、BMDを用いたゲッタリング効果の向上を両立させる。

【解決手段】初期状態での酸素濃度が5×1017atoms/cm3以下の半導体基板に素子分離領域3を形成し、ゲート絶縁膜5aを1000℃以上の熱酸化により形成した後、酸素をイオン注入して熱処理することで、BMD層30を素子分離領域3の底面よりも下方に形成する。

(もっと読む)

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】 膜中の酸素濃度を制御しつつ、良好な段差被覆性を有する酸化タンタル系の膜を形成する。

【解決手段】 基板を収容した処理室内にCVD反応が生じる条件下で、タンタルを含む原料ガスと窒化剤とを供給して、基板上に窒化タンタル層を形成する工程と、処理室内に酸化剤を供給して、窒化タンタル層の酸化剤による酸化反応が不飽和となる条件下で、窒化タンタル層を酸化する工程と、を交互に複数回繰り返すことで、基板上に、化学量論的にタンタルおよび窒素に対し酸素が不足した導電性の酸窒化タンタル膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】動作マージンの向上に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板上に、互いのゲート電極が接続されて配置される第1トランジスタ(P2)と、前記第1トランジスタと異なる導電型を有する第2トランジスタ(N4)とを具備し、前記第1トランジスタのゲート電極は、第1不純物と前記第1不純物の拡散を抑制する第2不純物とを含有し、前記第1不純物の濃度ピーク(PE1)は、前記第2不純物の濃度ピーク(PE2)よりも浅い位置に形成されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】容量絶縁膜である強誘電体のアニール工程を経ても、PchMOS型トランジスタのVth変動を抑制することができる半導体記憶装置およびその製造方法を提供すること。

【解決手段】半導体基板1上に形成され、P型不純物が導入されたゲート電極を有するPchMOS型トランジスタ4と、前記PchMOS型トランジスタ4の上方を覆うように、前記半導体基板1上に形成された第1の水素バリア膜8と、前記第1の水素バリア膜8上に形成され、容量絶縁膜として強誘電体を用いた強誘電体キャパシタ7と、前記強誘電体キャパシタ7の上方および側方を覆い、前記強誘電体キャパシタ7の周縁部において前記第1の水素バリア膜8と接続する第2の水素バリア膜14とを備え、前記第1の水素バリア膜8は、シリコン元素、水素元素、およびシリコン元素よりも水素元素を脱離しにくい第3の元素を含む。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

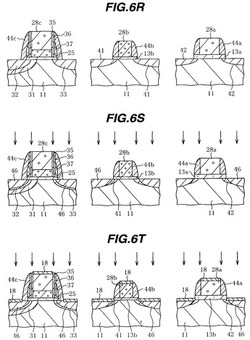

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】カルコゲナイド材料は高融点金属やシリコン酸化膜との接着性が低いため、相変化メモリの製造工程中に剥離しやすいという課題があった。また、カルコゲナイド材料は熱安定性が低いため、相変化メモリの製造工程中に昇華しやすいという課題があった。

【解決手段】カルコゲナイド材料層の上部及び下部に導電性や絶縁性の接着層を形成して剥離強度を向上させる。また、カルコゲナイド材料層の側壁に窒化膜からなる保護膜を形成して昇華を抑制する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、キャパシタ誘電体膜の劣化を防止すること。

【解決手段】半導体基板の上方に絶縁膜27を形成する工程と、絶縁膜27の上に、下部電極31a、強誘電体材料を含むキャパシタ誘電体膜32a、及び上部電極33aを備えたキャパシタQを形成する工程と、キャパシタQの側面と上面に、スパッタ法で第2の保護絶縁膜43を形成する工程と、第2の保護絶縁膜43の上に、原子層堆積法により第3の保護絶縁膜44を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

メモリ素子

【課題】低消費電力であり、信頼性の高いメモリ素子を提供する。

【解決手段】半導体層14と可動イオンを含む固体電解質層16との間に非晶質半導体層13を有する。半導体層14と非晶質半導体層13との伝導型が異なる。セットあるいはリセット電圧の印加により、可動イオンが固体電解質層16と非晶質半導体層13との間で移動し、非晶質半導体層13の伝導型が変化することにより、データの書き込み・消去が行われる。伝導型と共に電気抵抗も変化するため、高い抵抗分離特性が得られる。この非晶質半導体層13の変化は第二種相転移であり、潜熱の放出・吸収、非晶質半導体層の融点を超える温度上昇および体積変化を伴わず、消費電力が低く、高い信頼性を示す。

(もっと読む)

141 - 160 / 686

[ Back to top ]