Fターム[5F083GA25]の内容

Fターム[5F083GA25]に分類される特許

161 - 180 / 686

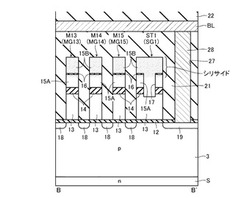

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル領域でシリサイドの成長速度を抑制しつつ、周辺回路領域では十分な量のシリサイドを形成することのできる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、メモリセル領域に形成されたメモリセルトランジスタと、周辺回路領域に形成された電界効果トランジスタとを備える。メモリセルトランジスタは、半導体基板上に第1のゲート絶縁膜を介して形成された浮遊ゲート電極と、浮遊ゲート電極上に配置される第1の電極間絶縁膜と、第1の電極間絶縁膜上に配置される制御ゲート電極とを有する。制御ゲート電極は、積層された複数の導電膜により形成される。制御ゲート電極は、積層された複数の導電膜間の界面のうちの少なくとも1つに形成され金属原子の拡散を抑制するバリア膜を有する。制御ゲート電極は、その一部がシリサイド化されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】低消費電力で動作し、記憶情報の信頼性が高く、小型で軽量、安価な記憶装置と

その駆動方法を提供することを課題とする。さらに低消費電力で動作し、記憶情報の信頼

性が高く、無線通信距離の長い、小型で軽量、安価な半導体装置とその駆動方法を提供す

ることを課題とする。

【解決手段】記憶装置は、少なくとも記憶素子がマトリックス状に配置されたメモリセル

アレイと、書き込み回路とを有し、記憶素子は第一の導電層と、第二の導電層と第一の導

電層と第二の導電層とに挟まれて設けられた有機化合物層とを有し、書き込み回路は、複

数回印加する電圧を発生させる電圧発生回路と、電圧の出力時間を制御するタイミング制

御回路とを有することを特徴とする。

(もっと読む)

記憶素子およびその駆動方法、並びに記憶装置

【課題】高抵抗状態の抵抗分布を改善し、大容量化が可能な記憶素子およびその動作方法、並びに記憶装置を提供する。

【解決手段】第1電極10および第2電極20の間に、各々抵抗変化層31A,32Aおよびイオン源層31B,32Bを有する二つの抵抗変化素子31,32を電気的に直列に接続し、電圧印加に対して互いに同じ抵抗状態へと変化させる。電圧印加によって抵抗変化素子31,32の抵抗値が同時に低下または上昇することにより、抵抗変化素子31,32が単一素子として動作する。各抵抗変化素子31,32において例えば熱や電界などの要因によって抵抗値が変化してしまう現象が生じた場合にも、記憶素子1の電気的特性としては、抵抗値の高い方に規定されるので、第1電極10および第2電極20の間の抵抗値変化は小さくなる。よって、高抵抗状態の抵抗分布が改善される。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】ゲート電極を形成し、ゲート電極上に第1の絶縁膜を形成し、第1の絶縁膜にハロゲンドープ処理を行って、第1の絶縁膜にハロゲン原子を供給し、第1の絶縁膜上に、ゲート電極と重畳して酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜に熱処理を行い、酸化物半導体膜上に接して、ソース電極およびドレイン電極を形成し、第2の絶縁膜を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】経年劣化および分極反転の繰り返しによる劣化の少ない強誘電体キャパシタまたは高誘電率を有する誘電体キャパシタを提供する。比抵抗の増大なしに信頼性の高い配線を有する半導体装置を提供する。

【解決手段】半導体基板表面上に形成された電極を含み、前記電極が、配向性を有する導電体層からなり、前記電極に加え、

下式

M1xM21-x

M1:Au、Pt、Ir、Pd、Os、Re、Rh、Tu、Cu、Co、Fe、Ni、V、Cr

M2:Ta、Ti、Zr、Hf、W、Y、Mo、Nb

で表されるアモルファスまたは微結晶からなるバリア層を含むことを特徴とする。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁層、電荷蓄積層、及びトンネル絶縁層のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、情報の書込みと消去を繰り返しても閾値電圧の変動が抑制された不揮発性記憶素子を提供する。

【解決手段】基板と、ソース電極と、ドレイン電極と、チャネル層と、電荷蓄積層と、ゲート電極と、前記チャネル層及び前記電荷蓄積層の間に設けられたトンネル絶縁層と、前記電荷蓄積層及び前記ゲート電極の間に設けられた、中間絶縁層と、を備え、前記中間絶縁層、前記電荷蓄積層、及び前記トンネル絶縁層が酸化ガリウムを含み、前記チャネル層が有機半導体層である不揮発性記憶素子である。

(もっと読む)

半導体基板、半導体装置、および半導体装置の製造方法

【課題】半導体装置の製造工程において、十分にゲッタリング効果を得ることができる半導体基板を提供する。

【解決手段】半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7と、を備えることを特徴とする半導体基板3を提供する。また、半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7を備える半導体基板3と、前記半導体層7上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記半導体層7内であって、前記ゲート電極に対して自己整合となる位置に設けられた不純物拡散領域と、を有することを特徴とする半導体装置を提供する。

(もっと読む)

不揮発性半導体記憶装置

【課題】素子領域内に含まれる不純物の拡散を抑制する。

【解決手段】不揮発性半導体記憶装置は、基板101と、前記基板101内に形成されたウェル領域102とを備える。前記装置は、前記ウェル領域102内に形成された素子分離溝Tにより、前記基板の主面に平行な第1方向に延び、前記第1方向に垂直な第2方向に互いに隣接するよう区画された複数の素子領域103と、前記素子分離溝T内に埋め込まれ、前記素子領域103同士を分離する素子分離絶縁膜104とを備える。前記装置は、前記複数の素子領域103の内部に、前記複数の素子領域のそれぞれを上部素子領域103Aと下部素子領域103Bとに分断するよう形成され、前記ウェル領域102内に注入された不純物の拡散を抑制する第1の拡散抑制層111と、前記上部素子領域103Aの前記第2方向に垂直な側面に形成され、前記不純物の拡散を抑制する第2の拡散抑制層112とを備える。

(もっと読む)

液体噴射ヘッドおよび液体噴射装置

【課題】Bi(Fe,Mn)O3およびBa(Zr,Ti)O3をベースにした圧電材料の特性を向上させる非鉛系圧電材料を提供する。

【解決手段】基板1上に弾性膜2、密着層3,4,5、下部電極6、圧電膜9を形成する。圧電材料は、Bi(Fe,Mn)O3とBa(Zr,Ti)O3の混晶からなる圧電材料であって、組成式(1−x)Bi(Fe1-yMny)O3−xBa(ZruTi1-u)O3で表され、0<x<0.40、0.01<y<0.10および0≦u<0.16である。かかる構成によれば、Bi(Fe1-yMny)O3の自発分極量や高いキュリー温度を維持しつつ、Ba(ZruTi1-u)O3により圧電特性の向上を図ることができる。

(もっと読む)

低蒸気圧のガス前駆体を用いて基板上にフィルムを蒸着させるシステム

【課題】基板(35)上にフィルムを蒸着する方法を提供する。

【解決手段】基板(35)は、約0.1ミリトールから約100ミリトールの圧力で反応容器(1)に入れられる。この方法は、i)少なくとも1つの有機金属化合物を含むガス前駆体を、約20℃から約150℃の温度、約0.1トールから約100トールの蒸気圧で反応容器に供給し、ii)反応容器に、パージガス、酸化ガス又はこれらの組み合わせを供給する、ことを含む反応サイクルを基板に施すことを含む。

(もっと読む)

SRAM

【課題】微細かつリーク電流が抑制されたSRAM。

【解決手段】第1の負荷トランジスタLT1を構成する第1のゲート電極G1bと、第1のゲート電極G1bの長手方向の延長上に、これと離間して延設され、第1の駆動トランジスタDT1を構成する第2のゲート電極G1aと、第1のゲート電極G1bと平行に延設され、第2の負荷トランジスタLT2を構成する第3のゲート電極G1bと、第3のゲート電極G1bと交差して形成され、第2の負荷トランジスタLT2を構成する第1のP型拡散領域PD21と、第1のゲート電極G1b及び第2のゲート電極G1a及び第1のP型拡散領域PD21に跨って形成された第1の共通コンタクトSC2と、を備えるSRAM。第1のP型拡散領域PD21は、第1のゲート電極G1bと第2のゲート電極G1aとの間隙領域近傍まで延設され、かつ、当該間隙領域には形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

液体噴射ヘッドの製造方法及びこれを用いた液体噴射装置、並びに圧電素子の製造方法

【課題】1.0×10―1A/cm2以上のリーク電流を抑制できる液体噴射ヘッドの製造方法及びこれを用いた液体噴射装置、並びに圧電素子の製造方法を提供する。

【解決手段】液体噴射ヘッドの製造方法は、第1電極60と第2電極80とに挟持された圧電体層70を備え、圧力発生室12に圧力変化を生じさせる圧電素子300とを有する液体噴射ヘッドの製造方法であって、蒸着法により白金又はイリジウムの少なくとも1種を含む拡散抑制層62を形成する工程を含む第1電極60を形成する第1電極形成工程と、第1電極60上に、チタン、ビスマス、バリウム、カリウム及びナトリウムを含む複合酸化物からなる圧電体層70を形成する圧電体層形成工程と圧電体層70上に、第2電極80を形成する第2電極形成工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗変化素子を半導体装置に組み込む際の必要なフォトマスクを削減しても高密度化が可能な抵抗変化素子を搭載した半導体装置及びその製造方法を提供すること。

【解決手段】配線溝を有する層間絶縁膜14と、配線溝に埋め込まれた配線16aと、配線16aを含む層間絶縁膜14上に形成されるとともに、配線16aに通ずる下穴を有する層間絶縁膜18と、少なくとも下穴が配置された領域における配線16a上に形成されるとともに、抵抗が変化する抵抗変化膜19aと、下穴が配置された領域における抵抗変化膜19a上に形成されたバリアメタル20aと、下穴が配置された領域におけるバリアメタル20a上に形成されたプラグ21aと、を備え、抵抗変化素子5は、第1電極と第2電極との間に抵抗変化膜19aが介在した構成となっており、配線16aは、第1電極を兼ね、バリアメタル20aは、第2電極を兼ねる。

(もっと読む)

液体噴射ヘッドの製造方法及びこれを用いた液体噴射装置、並びに圧電素子の製造方法

【課題】鉛を含有せず、かつリーク電流を抑制できる液体噴射ヘッドの製造方法及びこれを用いた液体噴射装置、並びに圧電素子の製造方法を提供する。

【解決手段】酸化ジルコニウムからなる絶縁体膜55を形成する工程と、絶縁体膜55上に反応性スパッタリング法により酸化チタンからなる密着層56を形成する工程と、密着層56上に第1電極60を形成する工程と、第1電極60上にチタン、ビスマス、バリウム、カリウム及びナトリウムを含む複合酸化物からなる圧電体層70を形成する工程と、圧電体層70上に第2電極80を形成する工程と、を具備する。

(もっと読む)

半導体装置

【課題】本発明は、不純物拡散層と半導体基板との間に形成される空乏層中におけるGIDLを抑制することのできる半導体装置を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成された第2の溝32と、少なくとも第2の溝32の側面32aを覆うゲート絶縁膜38と、ゲート絶縁膜38を介して、第2の溝32の側面32aに形成され、その上端面45aが半導体基板11の表面11aより低い位置にあってゲート電極39となる第1の導電膜45と、第1の導電膜45に形成され、その上端面46aが第1の導電膜45の上端面45bよりも高く、かつ半導体基板11の表面11aより低い位置にあってゲート電極39となる第2の導電膜46と、第1の導電膜45の上端面45b、及び第1の導電膜45の上端面45bから突出した第2の導電膜46を覆うように、第2の溝32内に設けられた第2の絶縁膜と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

半導体装置

【課題】容量素子の上部電極の配線抵抗の上昇を防ぐ半導体装置を提供する。

【解決手段】半導体装置100は、基板上に形成された層間絶縁膜104と、層間絶縁膜104上に形成され、導電材料により構成された下部電極108、下部電極108上に形成された容量絶縁膜110、および容量絶縁膜110上に形成され、下層TiN膜114、タングステン膜116、および上層TiN膜118が下層からこの順で積層された構成を有する上部電極112、により構成された容量素子101と、容量素子101上に形成され、酸素を含む層間絶縁膜120と、を含む。

(もっと読む)

161 - 180 / 686

[ Back to top ]