Fターム[5F083HA06]の内容

Fターム[5F083HA06]に分類される特許

101 - 120 / 569

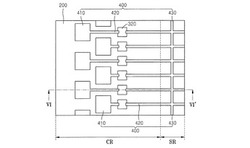

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

ゲインセル型半導体メモリ装置およびその駆動方法

【課題】ゲインセルとして知られている2つのトランジスタと1つのキャパシタよりなるメモリセルを改良する。

【解決手段】キャパシタの一方の電極をビット線に接続し、他方の電極を書き込みトランジスタのドレインに接続する。また、書き込みトランジスタのソースは、ソース線に接続される。この結果、例えば、キャパシタとしてスタック型キャパシタを採用する場合には、キャパシタの電極の一方をビット線の一部とすることができる。ソース線の電位と書き込みビット線の電位を設定することで、特定の書き込みトランジスタのみをオンとし、1つのメモリセルだけを書き換えることもできる。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

記憶素子、信号処理回路および記憶素子の駆動方法

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を位相反転素子の入力あるいは出力に接続し、他方の電極をスイッチング素子に接続する。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】絶縁層に凸状部またはトレンチ(溝部)を形成し、該凸状部またはトレンチに接して半導体層のチャネル形成領域を設けることで、チャネル形成領域を基板垂直方向に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、半導体層成膜前に、半導体層が接する凸状部またはトレンチの上端コーナー部に、R加工処理を行うことで、薄膜の半導体層を被覆性良く成膜する。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供すること。また、安定した電気的特性が付与された、信頼性の高い半導体装置を提供すること。

【解決手段】絶縁層に凸状構造体を形成し、該凸状構造体に接して酸化物半導体層のチャネル形成領域を設けることで、チャネル形成領域を3次元方向(基板垂直方向)に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、凸状構造体の上面と側面とが交わる上端コーナー部に曲面を形成し、酸化物半導体層が当該曲面に垂直なc軸を有する結晶を含むように形成する。これによって、酸化物半導体層の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルが3次元的に積層された不揮発性半導体記憶装置を工程数の増大を抑制しながら製造可能な不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板101上にスペーサ膜104とチャネル半導体膜103とを交互に複数層積層させた積層構造を形成し、積層構造に第1の方向に延在するトレンチを形成する。ついで、トレンチからチャネル半導体膜103を第2の方向にリセスして空隙を形成し、空隙内のチャネル半導体膜103上にトンネル誘電体膜108を形成し、フローティングゲート電極膜109を埋め込む。その後、第1の方向に隣接するメモリセル間でフローティングゲート電極膜109が分離され、チャネル半導体膜103が分離されないように、積層構造を第1の方向に所定の間隔で分割する。また、第2の方向に隣接するメモリセル間でチャネル半導体膜103が分離されるように、積層構造を第2の方向に所定の間隔で分割する。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体基板、半導体装置及びその製造方法

【課題】キャリア移動度(チャネル移動度)を増加させて、オン電流を増加させること。

【解決手段】トランジスタを形成するための半導体基板(10)は、主面(11a)を持つシリコン基板(11)と、このシリコン基板(11)の主面(11a)上に形成された歪緩和SiGe層(12)と、この歪緩和SiGe層(12)上に形成された歪Si層(13)と、を含む。

(もっと読む)

記憶素子および信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、アモルファスシリコン、ポリシリコン、微結晶シリコン、あるいは酸化物半導体等の化合物半導体をチャネル形成領域に含み、そのチャネル長が最小加工線幅の10倍以上あるいは、1μm以上であるトランジスタを用いる。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

101 - 120 / 569

[ Back to top ]