Fターム[5F083JA02]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104)

Fターム[5F083JA02]の下位に属するFターム

酸化膜を含む複合膜 (2,564)

酸化窒化膜 (1,013)

タンタル酸化膜(Ta2O5) (705)

ハロゲンを含む酸化膜 (7)

複酸化物 (3,106)

Fターム[5F083JA02]に分類される特許

1,701 - 1,709 / 1,709

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

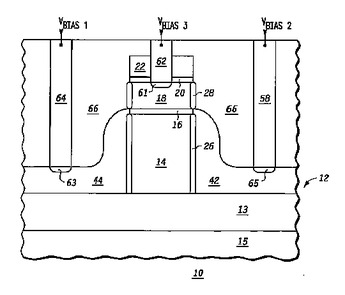

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

強誘電体キャパシタデバイスおよびFeRAMデバイス

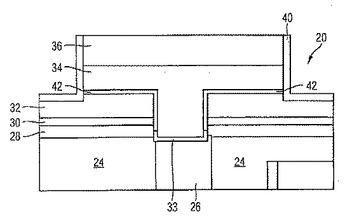

1つ以上のコンタクトプラグが通過して延びている基板と、上記基板上に形成された第1の層間絶縁膜とから、強誘電体キャパシタデバイス(例えばFeRAMデバイス)が形成されている。上記第1の層間絶縁膜上にはスペーサ層が形成されていて、このスペーサ層上には第1の酸素バリア層が形成されていて、この第1の酸素バリア層上にはバッファ層が形成されている。上記バッファ層上において、上記バッファ層と上記コンタクトプラグとの間に下地材料の層が形成されていて、第1の電極と第2の電極との間に誘電体層が挟まれている。上記デバイスに第2の酸素バリア層が塗布される。上記スペーサ層があれば、上記下地材料と上記コンタクトプラグとの界面まで酸化が及ぶことが抑制される。なぜなら、上記界面が、上記第1の酸素バリア層の下に位置しているからである。この結果、電気コンタクトが破損することはない。  (もっと読む)

(もっと読む)

自己整合型電荷分離構造NROMフラッシュメモリ

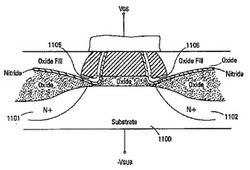

【課題】電荷捕獲領域が重ならずにセルを小さくすることが可能なトランジスタを提供する。

【解決手段】窒化物リードオンリーメモリ(NROM)セルは、窒化物層を有し、前記窒化物層は、トランジスタの中心部の下方に配置されない。前記窒化物層を有するゲート絶縁層は、2つの部分を有する。各部分は、構造分離された(structurally defined and separated)電荷捕獲領域を有する。電荷は、トランジスタの動作方向に応じて、ある特定の捕獲領域に蓄積される。前記ゲート絶縁層の前記2つの部分は、ポリシリコンゲート構造体の中間部分から外側部分を分離する。

(もっと読む)

スタガー式ローカル接続構造を持つメモリセルアレイ

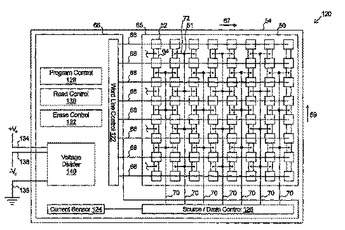

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

ナノクラスターを備えた半導体デバイス

ナノクラスターを備えたデバイスを形成するプロセス。本プロセスは、ナノクラスター(例えばシリコンナノ結晶)を形成する段階と、デバイスの誘電体を形成する次の段階中に酸化剤によるナノクラスターの酸化を抑制するためにナノクラスターを覆って酸化バリア層を形成する段階とを含む。酸化バリア層の少なくとも一部は、誘電体の形成後に除去される。1つの実施例では、本デバイスは、ナノクラスターがメモリの電荷蓄積トランジスタの電荷蓄積位置として利用されるメモリである。この実施例では、酸化バリア層が、メモリの高電圧トランジスタ用のゲート誘電体を形成することにより、ナノクラスターを酸化剤から保護する。 (もっと読む)

ハフニウムベースの高誘電率誘電体の原子層堆積

ハフニウムベースの誘電体膜を堆積する方法が提供される。本方法は、オゾンとハフニウム前駆体を含む1つ又はそれ以上の反応物質とを用いた原子層堆積段階を含む。半導体デバイスもまた提供される。該デバイスは、基板と、基板上に形成されたハフニウムベースの誘電体層と、基板及びハフニウムベースの誘電体層間に形成された界面層とを含み、該界面層は二酸化ケイ素を含み且つ結晶構造を有する。 (もっと読む)

酸化物薄膜製造方法及びその製造装置

酸化物薄膜の酸素欠損の低下とエピタキシャル成長との促進を図ることにより、優れた特性を有する酸化物薄膜を製造する薄膜製造方法であって、原料ガス、キャリアガス及び酸化ガスを混合して得た混合ガスを、加熱手段により原料の液化、析出、成膜が起こらない温度に維持されたガス活性化手段を通してシャワープレートから反応室内の加熱基板上に供給して反応させ、基板上に酸化物薄膜を製造する。その際、酸化ガスの割合を混合ガス基準で60%以上とする。また、核形成による初期層を形成する場合、その成膜プロセスにおける酸化ガス流量割合を60%未満とし、その後の成膜プロセスにおける酸化ガス流量割合を60%以上として行う。また、酸化物薄膜製造装置において、混合器とシャワープレートとの間に加熱手段を備えてなる。 (もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

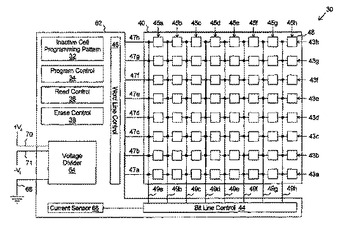

非揮発性メモリセルアレイの非活性領域に隣接する非揮発性メモリセルを読み出すための改善された方法

メモリセル48のアレイ30にデータパターンをストアし、再生するための方法であり、活性コラム45b及び45gと、不活性コラム45c及び45fとを含み、活性コラム45b及び45gにデータパターンをストアする。不活性メモリセルプログラミングパターン32が識別される。バルク消去中、過消去及び活性メモリセル48への電流リークを回避するために定期的に電荷をストアする目的で電荷がストアされる、不活性コラム45c及び45fのメモリセル48の全てあるいは選択された複数のメモリセルを、前述の不活性メモリセルプログラミングパターン32が識別する。  (もっと読む)

(もっと読む)

1,701 - 1,709 / 1,709

[ Back to top ]