Fターム[5F083JA39]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 高融点金属(W、Mo、Ta、Ti、Ni)及びその合金 (5,337)

Fターム[5F083JA39]に分類される特許

1 - 20 / 5,337

メタルブリッジ型記憶装置

半導体装置の製造方法

記憶装置

半導体装置の製造方法

半導体装置及びその製造方法

半導体装置及びその製造方法

半導体装置及びその製造方法

半導体装置

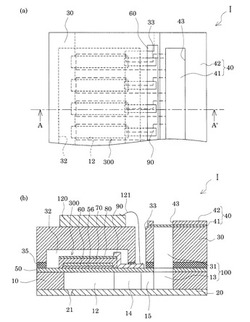

液体噴射ヘッド、液体噴射装置及び圧電素子

ニッケル酸ランタン膜形成用組成物及びその製造方法、ニッケル酸ランタン膜の製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、並びに液体噴射装置の製造方法

酸化ルテニウム膜の成膜方法

液体噴射ヘッド及び液体噴射装置並びに圧電素子

【課題】環境負荷が小さく、歪量が大きい液体噴射ヘッド、液体噴射装置及び圧電素子を提供する。

【解決手段】圧電体層70と圧電体層70に設けられた電極60,80とを具備する圧電素子300を備え、圧電体層70は、ビスマス、鉄、バリウム及びチタンを含みペロブスカイト構造を有する複合酸化物からなり、圧電体層70に駆動電圧Vaを印加したときの変位量をZmax、その後印加電圧を0Vにしたときの変位量をZ0としたとき、(Zmax−Z0)/Vaが70pm/V以上且つ比誘電率が700以下である。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

有機分子メモリおよび有機分子メモリ用有機分子

【課題】メモリ保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは、第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、分子軸に沿ってπ電子系が拡がっている分子骨格を持つ分子系において、(I)分子の最高被占軌道(HOMO)と最低空軌道(LUMO)のうちいずれか一方が分子軸にそって非局在化し、他方が分子軸に対して局在化している、(II)分子の最高被占軌道(HOMO)エネルギー準位が−5.75eV以上の値を持つ、を同時に満たす分子群より選ばれる有機分子を含む有機分子層と、を備える。

(もっと読む)

分子メモリ装置の製造方法

【課題】メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に第2方向に延びる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって前記第2配線間に複数本の第2絶縁部材を前記配線層に接するように形成する工程と、前記犠牲膜を除去することによりギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し他方には結合しない分子材料を形成する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体記憶装置

【課題】不揮発性メモリ部内蔵のSRAMの特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1とビット線BLとの間に抵抗変化層Rを有するReRAM部RM1を設け、アクセストランジスタAcc2とビット線/BLとの間に抵抗変化層Rを有するReRAM部RM2を設ける。SRAM通常動作期間の終了時において、例えば、蓄積ノードAに低電位(L=0V)、蓄積ノードBに高電位(H=1.5V)が保持されている場合、ReRAM部RM1をオン状態(ON)とし、ReRAM部RM2をオフ状態(OFF)とすることで、SRAMの保持データをReRAM部へ書き込み、再び、SRAM通常動作となった場合には、蓄積ノードAおよびBに対応するデータ書き戻すとともに、ReRAM部RM1、RM2の双方をオン状態に(リセット)する。

(もっと読む)

メモリ用途のセレクタデバイス

【課題】本発明は、メモリ用途のセレクタデバイスに関する。

【解決手段】本発明に係るセレクタデバイスは、MIT素子およびこれに熱的に連動する分割ヒータを備えたメモリアレイ内のメモリ素子を選択するためのセレクタデバイスであって、MIT素子は、MIT材料構成要素とバリア構成要素とを有し、分割ヒータを用いて相転移温度より高い温度に加熱されることにより、高抵抗状態から低抵抗状態に切り換え可能であり、バリア構成要素は、高抵抗状態にあるMIT素子の抵抗値を大きくするように構成されたことを特徴とするものである。セレクタデバイス。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置のスイッチング耐久性の向上を図る。

【解決手段】実施形態によれば、半導体記憶装置は、複数のセルアレイブロックと、制御回路とを備えている。制御回路は、選択ビット線を0ボルトにし、選択ワード線に0ボルトよりも高い第1の電位を与え、非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、選択セルアレイブロックに第1の方向で隣接し選択ビット線を選択セルアレイブロックと共有する隣接セルアレイブロックにおける、選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、選択メモリセルの抵抗変化膜の抵抗状態を変化させる。

(もっと読む)

1 - 20 / 5,337

[ Back to top ]