Fターム[5F083JA53]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | ポリサイド構造、サリサイド構造 (1,816)

Fターム[5F083JA53]に分類される特許

1 - 20 / 1,816

半導体装置及びその製造方法

半導体装置の製造方法

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体記憶装置

【課題】不揮発性メモリ部内蔵のSRAMの特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1とビット線BLとの間に抵抗変化層Rを有するReRAM部RM1を設け、アクセストランジスタAcc2とビット線/BLとの間に抵抗変化層Rを有するReRAM部RM2を設ける。SRAM通常動作期間の終了時において、例えば、蓄積ノードAに低電位(L=0V)、蓄積ノードBに高電位(H=1.5V)が保持されている場合、ReRAM部RM1をオン状態(ON)とし、ReRAM部RM2をオフ状態(OFF)とすることで、SRAMの保持データをReRAM部へ書き込み、再び、SRAM通常動作となった場合には、蓄積ノードAおよびBに対応するデータ書き戻すとともに、ReRAM部RM1、RM2の双方をオン状態に(リセット)する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

(もっと読む)

半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタとコンタクトパッド間のコンタクト抵抗の上昇を防ぎ、書き込み・読み出し不良を低減する、装置特性が優れた半導体装置を提供する。

【解決手段】タングステン膜8bを形成する工程と、タングステン膜8b上に窒化チタン膜からなる下部電極13を形成する工程と、酸化雰囲気下で窒化チタン膜に熱処理を行うことにより窒化チタン膜を酸化する工程と、下部電極13上に容量絶縁膜14を形成する工程と、容量絶縁膜14上に上部電極15を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造の容易な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第2のメモリセルを具備する第2のNANDセルユニットを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1のNANDセルユニットの両端に位置し、第1の浮遊ゲートと同層に形成され、第1の半導体層と接続される下部コンタクトと、第2のNANDセルユニットの両端に位置し、第2の半導体層と下部コンタクトとを接続する上部コンタクトとを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体記憶装置

【課題】データ書き込みエラー発生と消費電力を低減させた半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る半導体記憶装置は、第1極性の電圧パルス印加によってメモリセルに第1動作及び第2動作をさせるユニポーラ方式、並びに、第1極性とは異なる第2極性の電圧パルス印加によってメモリセルに第1動作をさせ且つ第1極性の電圧パルス印加によってメモリセルに第2動作をさせるバイポーラ方式の動作モードを有するデータ書き込み部と、メモリセルの第1動作の回数をカウントする第1動作回数カウント回路と、第1動作回数カウント回路を参照し、ユニポーラ方式による第1動作回数が第1規定回数に達した場合にデータ書き込み部の動作モードをバイポーラ方式に切り替える動作モード切り替え部とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】パンチスルーを抑制しつつ、セレクトゲート電極からのフリンジ電界を低減する。

【解決手段】空隙AG1は、制御ゲート電極8およびセレクトゲート電極12下に潜るようにしてトレンチ2に沿って連続して形成され、セレクトゲートトランジスタのドレイン領域間に達している。そして、セレクトゲートトランジスタのドレイン領域間において、空隙AG1が埋め戻し絶縁膜RBにて埋め戻されている。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1が配置される活性領域AcP1の下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wの底部および側部が、n型の半導体領域2Wと接するように配置し、p型の半導体領域1Wをn型の半導体領域2Wでpn分離し、アクセストランジスタAcc1のゲート電極G2とp型の半導体領域1Wを接続する。そして、この接続は、アクセストランジスタAcc1のゲート電極G2の上部からp型の半導体領域1Wの上部まで延在する一体の導電性膜であるシェアードプラグSP1wによりなされる。これにより、アクセストランジスタAcc1がオン状態の場合において、バックゲートであるp型の半導体領域1Wの電位が同時に高くなり、トランジスタのオン電流を大きくできる。

(もっと読む)

半導体装置

【課題】有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導

体装置を歩留まり高く作製する。また、信頼性の高いフレキシブルな記憶装置及び半導体

装置を歩留まり高く作製する。

【解決手段】剥離層を有する基板上に素子層及び素子層を封止する絶縁層を有する積層体

を形成し、剥離層から積層体を剥離してフレキシブルな記憶装置及び半導体装置を作製す

る方法であって、素子層において第1の電極層及び第2の電極層からなる一対の電極間に

有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金

層で形成する。また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物

を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成さ

れるフレキシブルな記憶装置及び半導体装置である。

(もっと読む)

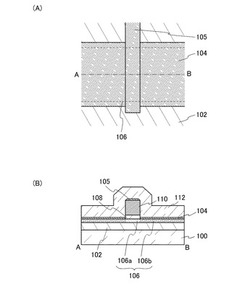

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】酸化物半導体層、及びチャネル保護層を覆うようにソース電極層、及びドレイン電極層となる導電膜を形成した後、酸化物半導体層、及びチャネル保護層と重畳する領域の導電膜を化学的機械研磨処理により除去する。ソース電極層、及びドレイン電極層となる導電膜の一部を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、チャネル保護層を有することにより、導電膜の化学的機械研磨処理時に当該酸化物半導体層に与える損傷、または膜減りを低減できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域、第1電極、及び第2電極を有する。メモリセル領域は、基板上に形成され、複数のメモリセルが積層される。第1電極は、基板上に複数の導電層が積層されて、容量素子の一方の電極として機能する。第2電極は、基板上に複数の導電層が積層されて、第1電極と基板に水平な方向において分離され、容量素子の他方の電極として機能する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

1 - 20 / 1,816

[ Back to top ]