Fターム[5F083JA55]の内容

Fターム[5F083JA55]の下位に属するFターム

Fターム[5F083JA55]に分類される特許

1 - 20 / 42

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

分子メモリ装置の製造方法

【課題】LSIプロセスによって製造可能な分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、前記第1配線層上に犠牲膜を形成する工程と、前記第1配線層上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料によって形成された複数本の芯材を形成する工程と、前記芯材の側面上に第2配線を形成する工程と、前記犠牲膜における前記第2配線の直下域に相当する部分を除去する工程と、前記第1配線と前記第2配線との間に、メモリ材料となる高分子を埋め込む工程と、前記芯材間であって前記第2配線間の空間に絶縁部材を埋め込む工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置は、半導体基板と、第1の方向に伸長する複数の第1の素子領域と、第1の素子領域を互いに分離する第1の素子分離領域と、第1の方向に伸長する複数の第2の素子領域と、第2の素子領域を互いに分離する第2の素子分離領域と、第1の素子領域と第2の素子領域との間に設けられ、第1および第2の素子領域に接続され、第1の方向と直交する第2の方向に伸長する第3の素子領域と、第1および第3の素子領域上にまたがり、第2の方向に伸長する第1の選択ゲート電極と、第2および第3の素子領域上にまたがり、第1の選択ゲート電極に隣接して平行に配置される第2の選択ゲート電極と、第1および第2の選択ゲート電極間の第3の素子領域に接続されるコンタクト電極を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】SiN膜等の犠牲膜の残存を防止する。

【解決手段】一の実施形態による不揮発性半導体記憶装置の製造方法では、基板上に、複数のメモリセルトランジスタと、複数の選択トランジスタとを形成する。さらに、前記方法では、前記メモリセルトランジスタ間と、前記メモリセルトランジスタと前記選択トランジスタとの間と、前記選択トランジスタ間に、第1から第5の絶縁膜を順に埋め込む。さらに、前記方法では、前記選択トランジスタ間の前記第2及び第4の絶縁膜が一部残存するように、第1のエッチング処理により、前記第2及び第4の絶縁膜を除去する。さらに、前記方法では、前記選択トランジスタ間に残存した前記第2及び第4の絶縁膜を、前記第1のエッチング処理後に行う第2のエッチング処理により除去する。

(もっと読む)

半導体装置

【課題】隣接するメモリセル間およびメモリセルと選択トランジスタとの間に間隙を設け

つつ、選択トランジスタおよび周辺回路における短絡を抑制する。

【解決手段】本実施形態による半導体記憶装置は、ゲートを有する複数のメモリセルが直

列に接続されたメモリセルストリングを備える。選択トランジスタが、メモリセルストリ

ングの一端にある端部メモリセルに接続されている。側壁膜が、端部メモリセルと選択ト

ランジスタとの間において、端部メモリセルのゲートの側面および選択トランジスタのゲ

ートの側面を被覆する。端部メモリセルの側壁膜と選択トランジスタの側壁膜との間に空

隙がある。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルの高集積化を図ることができる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板上に設けられた複数本の第1積層体と、前記複数本の第1積層体が配置された領域の外側に配置された第2積層体と、前記第1積層体及び前記第2積層体を覆う層間絶縁膜と、を備える。前記第1積層体と前記第2積層体との距離は、隣り合う前記第1積層体間の距離よりも長く、前記層間絶縁膜における前記第1積層体の相互間には第1の空隙が形成されており、前記層間絶縁膜における前記第1積層体と前記第2積層体との間には第2の空隙が形成されている。そして、前記第2の空隙の下端は、前記第1の空隙の下端よりも上方に位置している。

(もっと読む)

半導体記憶装置の製造方法

【課題】隣接するメモリセル間およびメモリセルと選択トランジスタとの間に間隙を設けつつ、選択トランジスタおよび周辺回路における短絡を抑制する。

【解決手段】本実施形態による半導体記憶装置は、ゲートを有する複数のメモリセルが直列に接続されたメモリセルストリングを備える。選択トランジスタが、メモリセルストリングの一端にある端部メモリセルに接続されている。側壁膜が、端部メモリセルと選択トランジスタとの間において、端部メモリセルのゲートの側面および選択トランジスタのゲートの側面を被覆する。端部メモリセルの側壁膜と選択トランジスタの側壁膜との間に空隙がある。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、一方向に沿って相互に平行に配列された複数枚のゲート電極膜と、前記一方向に延び、前記複数枚のゲート電極膜を貫通する半導体部材と、前記ゲート電極膜と前記半導体部材との間に設けられた電荷蓄積膜と、を備える。前記ゲート電極膜における前記半導体部材に対向した端部には、前記一方向に沿って突出した凸部が設けられており、前記ゲート電極膜間の空間の一部は気体層となっている。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 エアギャップ構造を簡易な方法で形成する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、半導体基板上に導電層を含む被加工膜を形成する工程と、前記被加工膜上にダミー膜を形成する工程と、を備えている。さらに、前記ダミー膜を所望の形状にデポ条件の異方性エッチングにより加工する工程と、前記被加工膜を所望の形状に異方性エッチングにより加工する工程と、前記所望の形状に加工された被加工膜上の前記ダミー膜を異方性エッチングにより除去する工程と、前記被加工膜上に上層膜を形成する工程と、を備えている。

(もっと読む)

不揮発性半導体記憶装置の製造方法、及び不揮発性半導体記憶装置

【課題】3次元的にトランジスタが配置された構成において、垂直方向に隣接するトランジスタの間隔を小さくした場合に、カップリング容量に起因したトランジスタの誤動作を低減できる不揮発性半導体記憶装置の製造方法、及び不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置の製造方法は、半導体基板の上に、第1の半導体膜と第2の半導体膜とが交互に複数回積層された積層膜における少なくとも複数の第2の半導体膜がゲート絶縁膜を介して半導体又は導電体の柱状部材によりそれぞれ保持された複数の構造を形成する形成工程と、前記形成工程で形成された前記複数の構造のそれぞれについて、前記複数の第2の半導体膜が前記柱状部材により保持された状態を維持しながら、前記積層膜から複数の前記第1の半導体膜を選択的に除去する除去工程と、前記除去工程を経た前記複数の構造のそれぞれにおける複数の前記第2の半導体膜の間に空洞を残すように、層間絶縁膜を埋め込む埋め込み工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

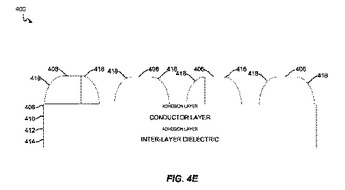

4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いたメモリ線および構造を形成する装置および方法

本発明は、4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いてメモリ線および構造を製作する装置、方法およびシステムを提供する。本発明は、基板の上方に配される第1のテンプレート層からフィーチャを形成することと、フィーチャに隣接してハーフピッチの側壁スペーサを形成することと、ハーフピッチの側壁スペーサをハードマスクとして用いることによって第2のテンプレート層内により小さいフィーチャを形成することと、より小さいフィーチャに隣接して4分の1ピッチの側壁スペーサを形成することと、4分の1ピッチの側壁スペーサをハードマスクとして用いることによって導体層から導体フィーチャを形成することとを含む。多数の追加の態様が開示される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

デバイスの製造方法及びデバイス

【課題】メモリ機能等を有する機能膜の水による劣化を防止すること。

【解決手段】成膜装置内で、機能膜が形成された基板上に、上記機能膜を覆うように、絶縁膜を形成する絶縁膜形成工程と、形成した上記絶縁膜の表面をプラズマに曝すプラズマ処理工程とを繰り返すこと。

(もっと読む)

半導体記憶装置

【課題】隣接セルとの容量を低減し、カップリング比を向上させる。

【解決手段】半導体記憶装置は、半導体基板101と、前記半導体基板上に所定間隔を空けて設けられた複数の第1の絶縁膜103と、前記第1の絶縁膜間にビット線方向に沿って設けられた素子分離領域102と、前記第1の絶縁膜上に設けられた第1の電荷蓄積膜104a、前記第1の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第1の電荷蓄積膜より狭い第2の電荷蓄積膜104b、及び前記第2の電荷蓄積膜上に設けられ、ワード線方向の幅が前記第2の電荷蓄積膜より広い第3の電荷蓄積膜104cを有する電荷蓄積層104と、前記第2の電荷蓄積膜と前記素子分離領域との間に設けられた第2の絶縁膜107と、前記電荷蓄積層上及び前記素子分離領域上に前記第2の方向に沿って設けられた第3の絶縁膜105と、前記第3の絶縁膜上に設けられた制御ゲート電極106と、を備える。

(もっと読む)

相変化メモリ装置

【課題】集積度を向上させつつ、或るメモリセルの熱源素子が発する熱が、隣接する他のメモリセルの相変化素子に対して与える影響を低減することが可能な相変化メモリ装置を提供する。

【解決手段】相変化メモリ装置は、複数の第1の配線と、第1の配線上に配置された複数のメモリセルと、複数のメモリセル上にそれぞれ配置された複数の第2の配線と、複数の第1の配線と複数の第2の配線との間に形成され、複数の第1の配線と複数の第2の配線とを絶縁する層間絶縁膜と、を備える。メモリセルは、電流が流れることにより発熱する熱源素子と、熱源素子による加熱後の冷却速度に応じて非晶状態または結晶状態の何れかの状態に遷移することにより抵抗値が変化する相変化素子と、を有し、隣接するメモリセル間の層間絶縁膜中に、空隙が形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】読み出し時のセル電流を増大させる揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングMSは、基板Baに対して垂直方向に延びるメモリ柱状半導体層35と、メモリ柱状半導体層35の側面を取り囲むように形成された電荷蓄積層34bと、電荷蓄積層34bの側面を取り囲むように形成され、メモリトランジスタMTr1〜MTr4の制御電極として機能するワード線導電層31a〜31dとを備える。ワード線導電層31a〜31dは、その間に誘電体を挟んで前記垂直方向に所定間隔Lをもって設けられている。誘電体は、酸化シリコンの比誘電率よりも小さい比誘電率を有する空気にて構成されている。所定間隔Lは、空気の等価酸化膜厚DEOTが、次の関係式[数1]を満たすように設定されている。

[数1]

Dsio2<DEOT<Dk

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】ダイオードの順方向特性を劣化させることなく逆方向特性を改善させる。

【解決手段】半導体記憶装置は、可変抵抗素子19及びダイオードDを有し、かつピラー状の第1及び第2のメモリセルと、第1のメモリセル及び第2のメモリセル間に設けられ、かつボイド21を有する絶縁層20とを含む。さらに、ダイオードDの中央部は、その上部及び下部よりも幅が狭くなっている。

(もっと読む)

1 - 20 / 42

[ Back to top ]