Fターム[5F083JA56]の内容

Fターム[5F083JA56]の下位に属するFターム

SiOF (63)

Fターム[5F083JA56]に分類される特許

1 - 20 / 1,742

半導体装置の製造方法

半導体装置及びその製造方法

半導体装置及びその製造方法

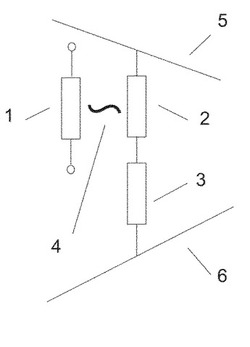

メモリ用途のセレクタデバイス

【課題】本発明は、メモリ用途のセレクタデバイスに関する。

【解決手段】本発明に係るセレクタデバイスは、MIT素子およびこれに熱的に連動する分割ヒータを備えたメモリアレイ内のメモリ素子を選択するためのセレクタデバイスであって、MIT素子は、MIT材料構成要素とバリア構成要素とを有し、分割ヒータを用いて相転移温度より高い温度に加熱されることにより、高抵抗状態から低抵抗状態に切り換え可能であり、バリア構成要素は、高抵抗状態にあるMIT素子の抵抗値を大きくするように構成されたことを特徴とするものである。セレクタデバイス。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物を低減する。また、酸化物半導体膜の被形成面近傍の結晶性を向上させる。また、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】シリコンを含む下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも酸化物半導体膜と重畳する領域に設けられたゲート電極と、酸化物半導体膜に電気的に接続されたソース電極、及びドレイン電極と、を有し、酸化物半導体膜は、下地絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度で分布する領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の領域に容易に第1の膜を形成して半導体装置の不良を低減する。また、スループットが向上して、製造コストの低減を図る。

【解決手段】半導体装置の製造方法では、半導体基板の第1及び第2の領域上に第1の膜を形成した後、第1の膜上にフォトレジストパターンを形成する。フォトレジストパターンをマスクに用いた第1の膜のエッチングにより、第2の領域上の第1の膜を除去すると共に第2の領域上を覆うように被覆膜を形成する。半導体基板に熱処理を行うことにより、被覆膜を除去すると共にフォトレジストパターンに焼き締め処理を行う。この後、フォトレジストパターンを除去する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】Inと、M1と、M2と、Znと、を含む酸化物材料であり、M1=13族元素、代表的にはGaであり、M2の元素は、M1の元素よりも含有量が少ない材料を提供する。M2としてはTi、Zr、Hf、Ge、Snなどが挙げられる。M2を含ませることで、酸化物半導体材料における酸素欠損の発生を抑制することができる。酸素欠損がほとんど存在しないトランジスタを実現できれば、半導体装置の信頼性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタとコンタクトパッド間のコンタクト抵抗の上昇を防ぎ、書き込み・読み出し不良を低減する、装置特性が優れた半導体装置を提供する。

【解決手段】タングステン膜8bを形成する工程と、タングステン膜8b上に窒化チタン膜からなる下部電極13を形成する工程と、酸化雰囲気下で窒化チタン膜に熱処理を行うことにより窒化チタン膜を酸化する工程と、下部電極13上に容量絶縁膜14を形成する工程と、容量絶縁膜14上に上部電極15を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ホールの微細化を図りつつ、ホールとスリットとを一括形成する。

【解決手段】4層分のワード線WL4〜WL1が順次積層されるとともに、ワード線WL4〜WL1にそれぞれ隣接するように4層分のワード線WL5〜WL8が順次積層され、ワード線WL5〜WL8が柱状体MP1にて貫かれるとともに、ワード線WL1〜WL4が柱状体MP2にて貫かれることで、NANDストリングNSが構成され、ワード線WL1〜WL8およびセレクトゲート電極SGD、SGSはロウ方向に沿って幅が周期的に変化されている。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

半導体装置の製造方法および半導体装置

【目的】配線間のコンタクト配置において配線間距離をより小さく形成する。

【構成】実施形態の半導体装置は、第1と第2の配線と、第1の絶縁膜と、第2の絶縁膜と、第1のコンタクトと、第2のコンタクトと、を備えている。第1と第2の配線は、基板上に互いに並行するように形成される。第1の絶縁膜は、第1と第2の配線を覆うように形成される。第2の絶縁膜は、第1と第2の制御ゲート線間の所定位置で第1と第2の配線と並行して延びるように形成され、第1の絶縁膜と材料が異なる。第1のコンタクトは、第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成される。第2のコンタクトは、前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】パンチスルーを抑制しつつ、セレクトゲート電極からのフリンジ電界を低減する。

【解決手段】空隙AG1は、制御ゲート電極8およびセレクトゲート電極12下に潜るようにしてトレンチ2に沿って連続して形成され、セレクトゲートトランジスタのドレイン領域間に達している。そして、セレクトゲートトランジスタのドレイン領域間において、空隙AG1が埋め戻し絶縁膜RBにて埋め戻されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜の水素濃度および酸素欠損を低減する。また、酸化物半導体膜を用いたトランジスタを有する半導体装置の信頼性を向上させる。

【解決手段】下地絶縁膜と下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜に重畳して設けられたゲート電極と、を有し、下地絶縁膜は、電子スピン共鳴にてg値が2.01で信号を表し、酸化物半導体膜は、電子スピン共鳴にてg値が1.93で信号を表さない半導体装置である。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、半導体層として機能する酸化物半導体膜と、酸化物半導体膜上のシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有し、少なくともゲート電極と重畳する酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%以下の濃度で分布する領域を有する構造とする。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグに接続される配線間隔の縮小を可能にする半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板に第1の領域と第2の領域とを定義し、第1の領域に第1のサイズを持つ第1の素子を形成し、第2の領域に、第1のサイズとは異なる第2のサイズを持つ第2の素子を形成し、第1の素子及び第2の素子を覆うように半導体基板上に第1の層間絶縁膜を形成し、第1の領域上の第1の層間絶縁膜を貫通し第1の素子の一部を露出させる第1のコンタクトホールを形成し、第2の領域上の第1の層間絶縁膜を貫通し第2の素子の一部を露出させる第2のコンタクトホールを形成し、第1のコンタクトホール及び第2のコンタクトホールをそれぞれ埋める第1のコンタクトプラグ及び第2のコンタクトプラグを同時に形成する。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜近傍の酸化物半導体膜に含まれる不純物元素濃度を低減する。また、ゲート絶縁膜近傍の酸化物半導体膜の結晶性を向上させる。また、当該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極、及びドレイン電極と、酸化物半導体膜、ソース電極、及びドレイン電極上に形成されたシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記酸化物半導体膜と重畳する領域に設けられたゲート電極と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度である領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

1 - 20 / 1,742

[ Back to top ]