Fターム[5F083JA57]の内容

Fターム[5F083JA57]に分類される特許

1 - 20 / 63

半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】酸素不足度の異なる遷移金属酸化物層を積層して抵抗変化層に用いた不揮発性記憶装置において、素子特性のばらつきを従来よりもさらに抑制する。

【解決手段】第1電極層を形成する工程(A)と、第1電極層の上に酸素不足型の遷移金属酸化物で構成される第1抵抗変化層を形成する工程(B)と、第1抵抗変化層の上端面を液体の酸化剤で化学的に酸化処理して中間酸化層を形成する工程(C)と、中間酸化層をさらに酸化し、第1抵抗変化層の上に第1抵抗変化層を構成する遷移金属酸化物よりも酸素不足度が少ない遷移金属酸化物で構成される第2抵抗変化層を形成する工程(D)と、第2抵抗変化層の上に、第2電極層を形成する工程(E)と、を有する、不揮発性記憶装置の製造方法。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を

含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成

領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領

域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成

された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、

を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜

厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳

する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

不揮発性記憶素子および不揮発性記憶装置

【課題】電極と抵抗変化層の界面に小さな突起を形成することなく、低電圧での初期化が可能な不揮発性記憶素子を提供する。

【解決手段】下部電極105と上部電極107との間に介在され、両電極間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層116を備える。抵抗変化層116は、第1の抵抗変化層1161と第2の抵抗変化層1162との少なくとも2層から構成され、第1の抵抗変化層1161は第1の遷移金属酸化物116bから構成され、第2の抵抗変化層1162は、第2の遷移金属酸化物116aと第3の遷移金属酸化物116cとから構成され、第2の遷移金属酸化物116aの酸素不足度は第1の遷移金属酸化物116bの酸素不足度及び第3の遷移金属酸化物116cの酸素不足度のいずれよりも高く、第2の遷移金属酸化物116a及び第3の遷移金属酸化物116cは、第1の抵抗変化層1161と接している。

(もっと読む)

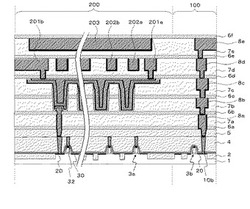

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

不揮発性記憶装置

【課題】不揮発性記憶装置の特性を向上させる。

【解決手段】第1の配線と第2の配線とに接続された記憶セルを備え、前記記憶セルは、複数の層を有し、前記複数の層は、第1の電極膜と第2の電極膜に挟まれ、炭素を含有する記憶層と、前記第1の電極膜と前記記憶層との間および前記第2の電極膜と前記記憶層との間の少なくともいずれかに設けられた、炭素を含有するバリア層と、を有し、前記バリア層は、前記記憶層よりも電気抵抗率が低いことを特徴とする不揮発性記憶装置が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】D−RAMのキャパシタを形成するシリンダのドライエッチ加工において、従来技術の製造方法ではアスペクト比が高いシリンダやコンタクトの形状がボーイング形状となり隣接するホール間ショートの問題やホール内に形成する電極成膜のカバレッジ異常などの問題が発生する。

【解決手段】本発明ではシリコン酸化膜4aにコンタクトホールを形成する際にボーイングが発生する部分にLow−k膜の炭化シリコン酸化膜5を挿入して積層構造とし、ドライエッチでシリコン酸化膜4aのエッチング速度に対し、炭化シリコン酸化膜5のエッチング速度が1/5〜1/10と遅い条件にすることでボーイング形状の抑制を可能にした。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

半導体装置の製造方法

【課題】デュアルゲート構造を有する半導体装置の製造技術において、MISFETのしきい値電圧の上昇を抑制することができる製造技術を提供する。

【解決手段】ポリシリコン膜PF1上にレジスト膜FR2を形成する。そして、レジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FR2をパターニングする。その後、パターニングしたレジスト膜FR2をマスクにしたイオン注入法により、露出しているnチャネル型MISFET形成領域NTRのポリシリコン膜PF1にアルゴン(Ar+)を導入する。このアルゴン注入工程により、nチャネル型MISFET形成領域NTRのポリシリコン膜PF1はアモルファス化する。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル領域の配線容量を低減し、かつ、周辺回路領域の配線抵抗を低減した半導体装置とその製造方法の提供。

【解決手段】本発明の半導体装置の製造方法は、メモリセル領域に縦型MOSトランジスタを、周辺回路領域にプレーナ型MOSトランジスタを形成し、前記縦型MOSトランジスタ上に深孔型立体キャパシタ素子10を形成する第1工程と、キャパシタ素子10上にメモリセル領域全体を覆うようにキャパシタ上部電極層31を形成し、前記メモリセル領域の上面の位置を、前記周辺回路領域の上面の位置よりも高く設定する第2工程と、前記周辺回路領域に第2コンタクトプラグ35を形成する第3工程と、前記メモリセル領域のキャパシタ上部電極層31上にセル部上部配線38を形成し、前記周辺回路領域に第2コンタクトプラグ35と接続し、セル部上部配線38よりも鉛直方向の膜厚が厚い周辺部上部配線39を形成する第4工程とを備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】非オーミック性素子と抵抗変化層とを組み合わせたクロスポイント型構成において充分な電流容量を確保し、安定な作動が可能な不揮発性半導体記憶装置を提供する。

【解決手段】下層電極配線15を含む基板11上に形成された層間絶縁層16と、下層電極配線上の層間絶縁層に形成されたコンタクトホールと、下層電極配線15上に形成された非オーミック性素子17と、コンタクトホール中に埋め込まれ、非オーミック性素子17上に形成された抵抗変化層22と、抵抗変化層22と接続し、層間絶縁層16上に形成された上層電極配線23とを備え、非オーミック性素子17は、複数層の半導体層の積層構成、金属電極体層と半導体層との積層構成または金属電極体層と絶縁体層との積層構成のうちの半導体層又は絶縁体層を含む少なくとも1層はコンタクトホールより大きな形状を有し、コンタクトホール中に積層構成のその他の層が埋め込み形成されている。

(もっと読む)

窒化膜の形成方法、酸窒化膜の形成方法、窒化膜のスパッタリング方法、ゲート絶縁膜の形成方法

【課題】実質的なリーク電流を生じることなく膜厚を減少させることができる高品質で均一な酸化膜、窒化膜あるいは酸窒化膜の形成方法を提供する。

【解決手段】基板上に絶縁膜を形成する工程と、前記絶縁膜をKrあるいはArを不活性ガスとしたプラズマに伴い生成された原子状酸素O*あるいは原子状窒化水素NH*に曝し、膜質を改変する工程とよりなる絶縁膜の形成方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】1容量素子当たりの面積を、微細加工に問題を起こすことなく縮小できるようにする容量素子を有するメモリーのような半導体装置を提供する。

【解決手段】酸素バリア膜16、層間絶縁膜17(酸化シリコン膜)上に、薄いエッチングストッパー膜18(窒化シリコン膜)、層間絶縁膜19(酸化シリコン膜)を形成し、酸素バリア膜16の直上にそれより大きい開口部をドライエッチングにより形成する。その後、強誘電体材料を容量絶縁膜とする容量素子の下部電極21を開口部20上を含むように形成する。開口部20を形成するための層間絶縁膜19のエッチングはエッチングストッパー膜18で容易に停止できるので、下地層間絶縁膜17がエッチングされない。こうして酸素バリア膜16を縮小し、容量素子占有面積を小さくできる。

(もっと読む)

デバイスの製造方法及びデバイス

【課題】メモリ機能等を有する機能膜の水による劣化を防止すること。

【解決手段】成膜装置内で、機能膜が形成された基板上に、上記機能膜を覆うように、絶縁膜を形成する絶縁膜形成工程と、形成した上記絶縁膜の表面をプラズマに曝すプラズマ処理工程とを繰り返すこと。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】製造工程による抵抗変化層の特性劣化を改善する抵抗変化層を用いた不揮発性記憶装置を提供する。

【解決手段】基板11上に形成された下層配線15と、下層配線15上の少なくとも一部に形成された抵抗変化層16と、下層配線15と抵抗変化層16とを含む基板11上に形成された層間絶縁層17と、層間絶縁層17を貫通して抵抗変化層16に接続するように形成されたコンタクトホール26と、抵抗変化層16に接続し、コンタクトホール26内に形成された埋め込み電極19と、層間絶縁層17上に埋め込み電極19と接続し、下層配線15に対して交差する上層配線20とを備え、抵抗変化層16は少なくとも酸素不足型の遷移金属酸化物を含み、かつコンタクトホール26が接続する領域の抵抗変化層16の表層部分がコンタクトホール26と接続する領域以外の抵抗変化層16の表層部分に比べて凹んだ形状になっている。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】不揮発性記憶装置の信頼性を向上させる。

【解決手段】第1の方向に延在する、少なくとも一つの第1の配線と、前記第1の配線の上層に配置され、前記第1の方向に対して非平行な第2の方向に延在する、少なくとも一つの第2の配線と、前記第1の配線と前記第2の配線とが交差する、前記第1の配線と前記第2の配線との間に配置された、記憶素子を有した記憶セルと、前記記憶セル間に配置された素子分離層と、を備え、前記記憶セルの側面に、前記素子分離層よりも密度の高い、少なくとも一層の絶縁膜が配置していることを特徴とする不揮発性記憶装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】水素バリア膜の成膜時に生じるダストを効果的に除去することができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板10上に設けられたトランジスタSTと、トランジスタST上に形成された第1の層間絶縁膜ILD1と、第1の層間絶縁膜ILD1内に設けられ、トランジスタSTの拡散層DL1に接続された下部コンタクトプラグCP1と、下部コンタクトプラグCP1および第1の層間絶縁膜ILD1上に形成された下部電極LE、強誘電体膜FEおよび上部電極UEを含む強誘電体キャパシタFCと、強誘電体キャパシタFCの周辺に設けられた第2の層間絶縁膜ILD2と、強誘電体キャパシタFCの側面と第2の層間絶縁膜ILD2との間に形成されたトレンチ50の内部を充填し、強誘電体キャパシタFCの側面を被覆し、水素の透過を抑制する第1のバリア膜BM1とを備えている。

(もっと読む)

1 - 20 / 63

[ Back to top ]