Fターム[5F083LA00]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937)

Fターム[5F083LA00]の下位に属するFターム

対称レイアウト (559)

メモリセルユニット間レイアウト (635)

センスアンプ (769)

カラムデコーダ (735)

ローデコーダ(ワード線昇圧回路等を含む) (888)

アドレスバッファ回路 (155)

入出力バッファ回路 (308)

基板バイアス回路 (46)

プリチャージ回路 (119)

周辺回路(制御回路) (893)

配線レイアウト (4,019)

コンタクトの配置レイアウト (1,397)

チップレイアウト (365)

Fターム[5F083LA00]に分類される特許

1 - 20 / 49

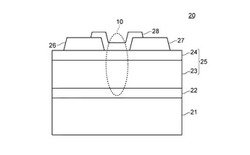

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタとコンタクトパッド間のコンタクト抵抗の上昇を防ぎ、書き込み・読み出し不良を低減する、装置特性が優れた半導体装置を提供する。

【解決手段】タングステン膜8bを形成する工程と、タングステン膜8b上に窒化チタン膜からなる下部電極13を形成する工程と、酸化雰囲気下で窒化チタン膜に熱処理を行うことにより窒化チタン膜を酸化する工程と、下部電極13上に容量絶縁膜14を形成する工程と、容量絶縁膜14上に上部電極15を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜とゲート絶縁膜との界面において、電子の界面散乱を抑制することで、電気的特性に優れたトランジスタを提供する。

【解決手段】基板上に酸化物半導体膜を形成し、酸化物半導体膜上に酸化物半導体以外の半導体膜を形成した後、酸化物半導体膜と該半導体膜との界面において、酸化物半導体膜中の酸素原子と半導体膜中の原子とを結合させる。これにより、酸化物半導体膜と該半導体膜との界面において構造を連続させることができる。また、酸化物半導体膜から脱離した酸素が、該半導体膜に拡散することで、該半導体膜は酸化されるため、絶縁膜とすることができる。このようにして形成されたゲート絶縁膜を用いることで、酸化物半導体膜とゲート絶縁膜との界面において電子の界面散乱が抑制され、電気的特性に優れたトランジスタを作製できる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置

【課題】素子分離すべき領域にダミーの補助ゲートを配置することで、電気的に分離する方法(FS方式)を採用しつつ、補助ゲートに給電するための新たな専用の配線を設けることによるチップの縮小化の弊害を解消する半導体装置を提供する。

【解決手段】半導体基板2に埋め込み形成された素子分離膜によって、複数のセル部活性領域が区画された半導体装置1であって、半導体基板2に設けられたゲート溝内に、ゲート絶縁膜を介して形成された補助セルゲート28aが、半導体基板2と電気的に接続されている。

(もっと読む)

デバイス製造方法

【課題】 ノズルから吐出された液滴に変質等が生じないように吐出空間の雰囲気を置換することが可能なデバイス製造方法を提供する。

【解決手段】 デバイスの製造方法は、基板をチャンバ内に搬入して載置台に載置する工程と、待機位置において封止部材により液滴吐出ノズルを隔離した状態で、チャンバの内部を減圧する減圧工程と、ガス供給機構からチャンバ内にパージガスを導入してチャンバ内部の雰囲気を置換するとともに大気圧状態に戻す雰囲気置換工程と、封止部材による液滴吐出ノズルの隔離を解除し、液滴吐出ノズルを吐出位置に移動させて被処理体へ向けて前記液滴を吐出する吐出工程とを含む。

(もっと読む)

アプリケーション回路及び半導体デバイスの動作方法

【課題】バッテリレス電子タイマに適用される半導体デバイス、及びその動作方法とアプリケーション回路を提供する。

【解決手段】半導体デバイス600は、第1導電型半導体基板と、ゲート誘電層と、フローティングゲート606と、第2導電型ウェル608と、第1導電型ウェル610と、第2導電型ソース拡散層612と、第2導電型ドレイン拡散層614と、第2導電型制御ゲート拡散層616と、を含む。制御ゲート拡散層616、ソース拡散層612及びドレイン614の間の漏れ電流が二重のウェル領域上に印加されるバイアスを調節することにより減少される。

(もっと読む)

半導体素子、記憶回路、集積回路、及び集積回路の駆動方法

【課題】回路規模の拡大に資する新規の半導体素子を提供する。

【解決手段】独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成することを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面(第1の面)近傍におけるチャネル(電流経路)の形成と、上面(第2の面)近傍におけるチャネルの形成とを独立して制御する。これにより、2つの電気的スイッチを別個に設ける場合(例えば、2つのトランジスタを別個に設ける場合)と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

半導体装置および該半導体装置の作製方法

【課題】良好な電気特性を有する半導体装置および該半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に水素透過膜を形成し、水素透過膜上に水素捕縛膜を形成し、加熱処理を行って、酸化物半導体膜から水素を脱離させ、酸化物半導体膜の一部に接するソース電極およびドレイン電極を形成し、水素捕縛膜の露出されている部分を除去して、水素透過膜のチャネル保護膜を形成する半導体装置の作製方法である。また、該作製方法で作製された半導体装置である。

(もっと読む)

半導体装置

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶装置及びそれを有する半導体装置を提供することを課題とする。また、信頼性が高く、安価な不揮発の記憶装置及び半導体装置の提供を課題とする。

【解決手段】絶縁表面上に形成される第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層に挟持される第1の絶縁層と、第1の導電層の一部を覆う第2の絶縁層とを有し、第1の絶縁層は第1の導電層の端部、絶縁表面、及び第2の絶縁層を覆うことを特徴とする記憶装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

1 - 20 / 49

[ Back to top ]