Fターム[5F083LA03]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | センスアンプ (769)

Fターム[5F083LA03]に分類される特許

1 - 20 / 769

記憶装置

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造の容易な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第2のメモリセルを具備する第2のNANDセルユニットを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1のNANDセルユニットの両端に位置し、第1の浮遊ゲートと同層に形成され、第1の半導体層と接続される下部コンタクトと、第2のNANDセルユニットの両端に位置し、第2の半導体層と下部コンタクトとを接続する上部コンタクトとを備える。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

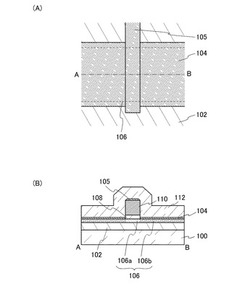

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減させ、オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】絶縁表面上の一対の電極と、一対の電極と接して設けられる酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳するゲート電極と、を有し、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含む半導体装置とする。さらに、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含ませる方法として、フッ素を含む雰囲気におけるプラズマ処理を用いることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜のソース領域およびドレイン領域の導電率を高めることで、高いオン特性を有する酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】第1の領域および第2の領域を有し、少なくともインジウム(In)を含む酸化物半導体膜と、少なくとも酸化物半導体膜の第1の領域と重畳して設けられたゲート電極と、酸化物半導体膜およびゲート電極の間に設けられたゲート絶縁膜と、少なくとも一部が酸化物半導体膜の第2の領域と接して設けられた電極と、を有し、酸化物半導体膜は、酸化物半導体膜と電極との界面近傍のInの濃度が高く、界面から15nmの範囲で遠ざかるに従いInの濃度が低くなる。なお、酸化物半導体膜の第1の領域はトランジスタのチャネル領域として機能し、第2の領域はトランジスタのソース領域、ドレイン領域として機能する。

(もっと読む)

不揮発性メモリ

【課題】メモリセルへのデータの書き込みと読出しの信頼性を高くした不揮発性メモリを提供する。

【解決手段】2つのメモリセルを隣接させた基本ユニットを単位にするメモリセルアレイを有し、前記基本ユニットの2つのメモリセルのメモリセル選択用トランジスタのソース端子を共通のソース線に接続し、前記2つのメモリセルを2つのビット線に接続した抵抗変化型メモリであって、前記ソース線の配線パターンと前記ビット線の配線パターンを平行に走行させ、前記ソース線の配線パターンと前記ビット線の配線パターンの一部の領域を上下で重ねあわせて対向させる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜の水素濃度および酸素欠損を低減する。また、酸化物半導体膜を用いたトランジスタを有する半導体装置の信頼性を向上させる。

【解決手段】下地絶縁膜と下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜に重畳して設けられたゲート電極と、を有し、下地絶縁膜は、電子スピン共鳴にてg値が2.01で信号を表し、酸化物半導体膜は、電子スピン共鳴にてg値が1.93で信号を表さない半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域、第1電極、及び第2電極を有する。メモリセル領域は、基板上に形成され、複数のメモリセルが積層される。第1電極は、基板上に複数の導電層が積層されて、容量素子の一方の電極として機能する。第2電極は、基板上に複数の導電層が積層されて、第1電極と基板に水平な方向において分離され、容量素子の他方の電極として機能する。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。第n行のメモリブロックはサブビット線SBL_n_mと複数のメモリセルを有する。メモリセルはトランジスタと容量素子を直列に接続し、容量素子の電極の一をサブビット線SBL_n_mに接続する。さらに第n行のメモリブロックは書き込みトランジスタWTr_n_mと読み出しトランジスタRTr_n_mを有し、また、読み出しトランジスタRTr_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの電位変動を増幅回路AMP_n_mで増幅する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】 可変抵抗素子への電圧印加極性が異なる2種類の書き込み動作後の各ベリファイ動作を夫々低消費電力且つ高速に実行可能な半導体記憶装置を提供する。

【解決手段】 書き込み回路22が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の電気抵抗を低抵抗化させるセット動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の電気抵抗を高抵抗化させるリセット動作を夫々実行可能に構成され、読み出し回路21が、メモリセルの一端側から可変抵抗素子を経由して他端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第1読み出し動作と、メモリセルの他端側から可変抵抗素子を経由して一端側へ電流を流すことで可変抵抗素子の抵抗状態を読み出す第2読み出し動作を夫々実行可能に構成されている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】熱工程による負担を減らし、メモリセル特性の向上を図る。

【解決手段】本実施形態による不揮発性半導体記憶装置の製造方法よれば、基板上30に、コントロールゲートCGとなる導電膜を形成する。前記導電膜の上面から下面まで貫通するホール40を形成する。前記ホールの内面上に、ブロック絶縁膜150を形成する。前記ブロック絶縁膜上に、電荷蓄積膜151を形成する。前記電荷蓄積膜上に、トンネル絶縁膜152を形成する。前記トンネル絶縁膜上に、半導体層SPを形成する。前記半導体層上に、前記ホールが埋め込まれないように酸素乖離の触媒作用を有する材料を含む膜153を形成する。前記ホールの内側から前記膜を介して、前記トンネル絶縁膜と前記半導体層との界面を酸化する。

(もっと読む)

高速OTP感知スキーム

【課題】不揮発性メモリアレイのための高速感知スキームを提供する。

【解決手段】メモリアレイは、ビット線をVSSなどの第1電圧レベルまで予備充電するための予備充電回路を備えた、相補形ビット線構成で配置された不揮発性メモリセルと、相補形ビット線対の基準ビット線に基準電荷を印加するための基準回路と、相補形ビット線対の間の電圧差を感知するためのビット線感知増幅器とを備えている。データビット線の電圧は、起動されたワード線に接続されたプログラム済みの不揮発性メモリセルがワード線電圧をデータビット線に結合すると変化する。

(もっと読む)

半導体装置

【課題】半導体チップに構成されるメモリコアにおける電源系を容易に分離可能な配線構造を実現しスループットの向上が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体チップC1に複数のメモリコア(DRAMコア)が構成される。各メモリコアは、第1電源によって動作しパラレルデータを双方向に伝送するデータバスを駆動する第1回路領域と、第1電源と分離された第2電源によって動作しデータバスを伝送されるパラレルデータと外部端子を介して入出力されるシリアルデータとを双方向に変換する第2回路領域と含む。第1貫通電極群23は、第1回路領域に第1電源を供給する複数の貫通電極をY方向に並べて配置され、第2貫通電極群21は、第2回路領域に第2電源を供給する複数の貫通電極をY方向と交差するX方向に並べて配置される、それぞれの貫通電極群を経由して第1及び第2電源の配線群が互いに分離した配置で形成される。

(もっと読む)

1 - 20 / 769

[ Back to top ]