Fターム[5F083LA05]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | ローデコーダ(ワード線昇圧回路等を含む) (888)

Fターム[5F083LA05]に分類される特許

41 - 60 / 888

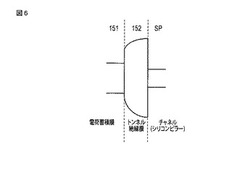

不揮発性半導体記憶装置

【課題】円筒型MONOSメモリセルで電荷保持特性の向上を図る。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に形成され、上面から下面まで達する円筒状の貫通ホールを有するコントロールゲートCGと、前記貫通ホール内における前記コントロールゲートの側面上に形成されたブロック絶縁膜150と、前記貫通ホール内における前記ブロック絶縁膜の側面上に形成された電荷蓄積膜151と、前記貫通ホール内における前記電荷蓄積膜の側面上に形成されたトンネル絶縁膜152と、前記貫通ホール内における前記トンネル絶縁膜の側面上に形成された半導体層SPと、を具備し、前記トンネル絶縁膜は、SiO2を母材とし、添加することで前記母材のバンドギャップを低下させる元素を含む第1絶縁膜を含み、前記元素の濃度および濃度勾配は、前記半導体層側から前記電荷蓄積膜側に向かって単調に増加する。

(もっと読む)

半導体記憶装置

【課題】アドレス信号の配線に起因する配線容量を低減させ、アクセス速度の高速化を実現する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のビット線と複数のワード線に対応して設けられた複数のメモリセルと、複数のメモリセルのいずれかを特定するためのアドレス信号を中継する中継バッファと、複数のワード線のうち、中継バッファにて中継されたアドレス信号に応じたワード線を選択するトランジスタを複数有するワード線ドライバ回路と、を備え、トランジスタでは、2つの拡散層のうち一方の拡散層が他のトランジスタの拡散層と共有し、拡散層を共有している2つのトランジスタで構成される複数の共有回路が、複数のトランジスタ群に分けられ、複数のトランジスタ群のうち隣り合う前記トランジスタ群の隙間部分に、隣り合うトランジスタ群のいずれかのゲート配線が設けられ、中継バッファはトランジスタ群のゲート配線と接続される。

(もっと読む)

抵抗変化型メモリデバイスおよびその駆動方法

【課題】リファレンスセルの抵抗状態に応じて、読み出し電流を設定する構成で、誤書き込みによる抵抗の変化が発生することなく、より信頼性の高いリファレンス電流を得ることが可能な抵抗変化型メモリデバイスおよびその駆動方法を提供する。

【解決手段】素子両端に極性の異なる信号を印加することで可逆的に記憶素子の抵抗値が変化するメインメモリセルを含むメモリアレイ部と、素子両端に極性の異なる信号を印加することで可逆的に抵抗値が変化する記憶素子を含み、メインメモリセルのデータを識別するために必要な参照電流を発生させるリファレンスセルを含むリファレンスセル部と、を有し、リファレンスセルの抵抗状態に応じた参照電流の印加電流の向きが設定されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

半導体装置

【課題】抵抗変化型記憶素子を用いた半導体装置の耐タンパ性を向上させること。

【解決手段】半導体装置は、1ビットのセルデータを記憶するユニットセル(10)と、制御回路(100)とを備える。ユニットセル(10)は、n個(nは2以上の整数)の抵抗変化型記憶素子(31)を備える。それらn個の抵抗変化型記憶素子(31)のうち少なくとも1つが、セルデータが記録される有効素子(40)である。セルデータの読み出し時、制御回路(100)は、少なくとも有効素子(40)を選択し、有効素子(40)に記録されているデータをセルデータとして読み出す。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、コンタクトプラグが形成されるセル部と、前記コンタクトプラグが形成されない周辺回路部とを平坦化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に最上部が第1の絶縁膜からなる配線層を形成する工程と、

前記半導体基板と前記配線層とを被う第2の絶縁膜を形成する工程と、前記第2の絶縁膜の所定の領域をエッチングし、前記配線層と前記半導体基板とを露出させる開口部を形成する工程と、前記開口部内と前記第2の絶縁膜上とに導電膜を形成する工程と、前記第1の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有し、前記第2の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有する条件で、前記第2の絶縁膜と前記導電膜とを前記第1の絶縁膜が露出するようCMP法で除去し、コンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

不揮発性メモリセルおよび不揮発性メモリ

【課題】 スタティックノイズマージンを損なうことなく、揮発性記憶部および不揮発性記憶部間のストアとリコールを行える不揮発性メモリセルを提供する。

【解決手段】 不揮発性記憶部12は、揮発性記憶部11のノードV1とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw1および抵抗変化型素子R1と、揮発性記憶部11のノードV2とバイアス供給ノードNSとの間に直列に介挿されたNチャネルトランジスタTw2および抵抗変化型素子R2を有する。ストア時、NチャネルトランジスタTw1およびTw2はONとされ、抵抗変化型素子R1およびR2は、ノードV1(V2)からバイアス供給ノードNSに向かう電流を通過させたときに高抵抗となり、逆方向の電流を通過させたときに低抵抗となる。リコール時は、揮発性記憶部11のフリップフロップに対する電源電圧を立ち上げる。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイと入出力バッファ間の遅延の最大値を抑制し高速に入出力動作が行える半導体記憶装置を提供する。

【解決手段】複数のメモリセルアレイが配置されたメモリセルアレイ部と、外部入出力回路が配置された周辺回路部と、複数のメモリセルアレイと周辺回路部とを接続する内部バス4と、を備え、周辺回路部は、複数の外部入出力バッファ23と、メモリセルアレイとの間で内部バスを並列に入出力するデータと複数の外部入出力バッファを直列に入出力するデータとを相互に変換する複数のバスインターフェース回路24と、を備え、複数のバスインターフェース回路間の距離d1が、複数の外部入出力バッファ間の距離d2及び内部バスの配線幅の最大値d3より狭くなるように、複数のバスインターフェース回路24は、内部バス4と複数の外部入出力バッファとの間にまとめて配置されている。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体記憶装置

【課題】 ビット線選択回路の小型化を図るとともにビット線の駆動時間を高速に行うことができる半導体記憶装置を提供する。

【解決手段】 フラッシュメモリ10は、セルユニットNUが行列状に複数配置されたメモリアレイ100と、セルユニットNUに接続されたビット線を選択するビット線選択回路200とを有する。ビット線選択回路200は、偶数ビット線GBL_e、奇数ビット線GBL_oをセンス回路に選択的に接続するための選択トランジスタSEL_e、SEL_o、BLSを含む第1の選択部210と、偶数ビット線GBL_eおよび奇数ビット線GBL_oに選択的にバイアス電圧を印加するためのバイアストランジスタYSEL_e、YSEL_oとを含む第2の選択部220とを有する。第2の選択部220のバイアストランジスタYSEL_e、YSEL_oは、記憶素子と共通のウエル内に形成される。

(もっと読む)

半導体装置

【課題】補償容量としてのキャパシタを備えた補償容量領域において、その容量値を上げずにその面積を大きくして、製造工程時のキャパシタの剥がれを防止する。

【解決手段】第1の領域AR1に設けられたキャパシタ23の下部電極の各々には、端子A(M1)からVPERI電圧が供給されている。第2の領域AR2に設けられたキャパシタ23の下部電極の各々には、端子B(M1)からVSS電圧が供給されている。第3の領域AR3に設けられたキャパシタ23の下部電極の各々は、端子C(M1)から1/2VPERI電圧が供給されている。プレート24は、1/2VPERI電圧を第1〜3の領域AR1〜AR3のキャパシタ23の各上部電極に共通に供給している。第3の領域AR3は、各々の下部電極及び上部電極に同一電圧(1/2VPERI)が供給されるため容量に電荷が溜まることがない。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】PRAMの高集積化を行うこと。

【解決手段】第1層間絶縁膜のホールの内壁面を覆うサイドウォール絶縁膜と、ホール内においてサイドウォール絶縁膜を介して埋め込まれたコンタクトプラグと、第1層間絶縁膜上の所定の領域にてコンタクトプラグに接続されるように配された下部電極と、下部電極を含む前記第1層間絶縁膜上を覆う第2層間絶縁膜と、第2層間絶縁膜を貫通し、下部電極の側端面の一部が表れ、かつ、第1層間絶縁膜の所定深さまで形成された開口部と、開口部を含む前記第2層間絶縁膜上の所定の領域に配されるとともに、前記開口部にて前記下部電極の側端面の一部と接続された相変化材料層と、相変化材料層上に配された上部電極と、を備える。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

半導体記憶装置

【課題】3次元型の半導体記憶装置のパフォーマンスを向上させる。

【解決手段】実施形態によれば、半導体記憶装置は、半導体基板と、半導体基板上に設けられ、積層された複数のメモリセルを含む複数のメモリユニットと、カラム方向に配列された複数のメモリユニット上に複数本形成されたビット線とを備え、複数のビット線のロウ方向の配列ピッチは、メモリユニットのロウ方向の配列ピッチよりも小さく、カラム方向に配列された各メモリユニットの端部は、複数本形成されたビット線のいずれか1つに接続される。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

41 - 60 / 888

[ Back to top ]