Fターム[5F083LA05]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | ローデコーダ(ワード線昇圧回路等を含む) (888)

Fターム[5F083LA05]に分類される特許

881 - 888 / 888

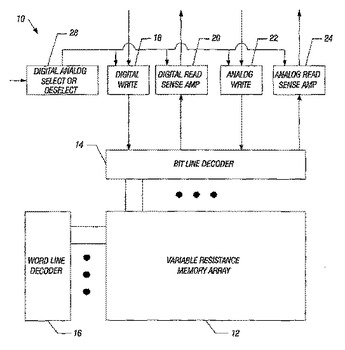

アナログ相変化メモリ

相変化材料を使ってアナログメモリを形成することができる。相変化材料は複数の抵抗状態のうちの一つをとり、それが保存すべき特定のアナログ特性を定義する。  (もっと読む)

(もっと読む)

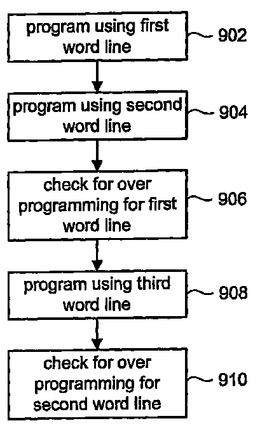

隣接するメモリセルのプログラミングの後にオーバー・プログラミングされたメモリセルを検出する技術

非揮発性半導体メモリシステム(又は他のタイプのメモリシステム)において、メモリセルは、その閾電圧を変更することによってプログラミングされる。システム内の様々なメモリセルに対するプログラミングのタイミングが異なることが原因で、いくつかのメモリセルは、オーバー・プログラミングされてしまう可能性がある。即ち、例えば、セルの閾電圧が、目的とされた値、又は、目的とされた範囲から外れてしまう可能性がある。本発明は、セルに対するプログラミングが原因で、それに隣接する行のメモリセルがオーバー・プログラミングされたか否かを判断することを含んでいる。

(もっと読む)

(もっと読む)

フラッシュ/ダイナミックランダムアクセスメモリフィールドプログラマブルゲートアレイ

集積回路デバイスにおいて2つのノードを選択的に相互接続するための回路は、複数のワード線及び複数のビット線を有するメモリアレイを含む。リフレッシュトランジスタは複数のビット線のうち一本に接続されたソース、ダイナミックランダムアクセスメモリワード線に接続された制御ゲート、及びドレインを有する。スイッチトランジスタはリフレッシュトランジスタのドレインに接続されたゲート、一番目のノードに接続されたソース、及び二番目のノードに接続されたドレインを有する。アドレスデコーダはワード線とダイナミックランダムアクセスメモリワード線に周期信号を供給する。  (もっと読む)

(もっと読む)

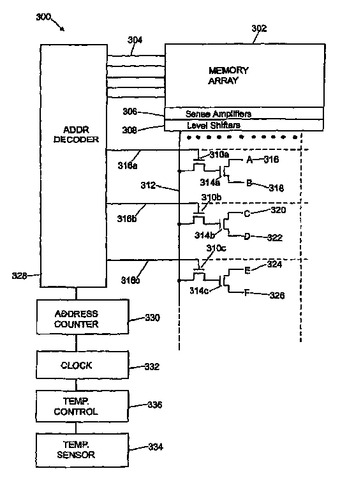

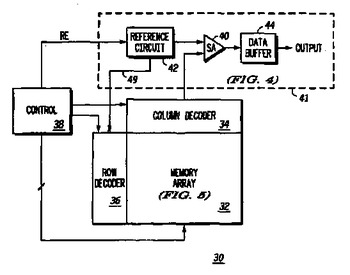

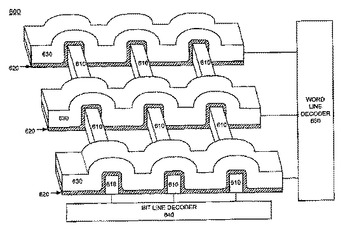

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

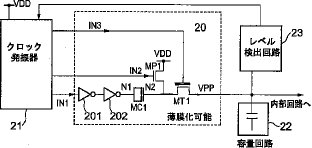

昇圧電位発生回路及び制御方法

【課題】 半導体メモリにおいて、外部電源電圧が低下しても、半導体メモリ内部では、高速動作を可能にすると共に、小型化をも可能にする昇圧電位発生回路を提供する。

【解決手段】 容量MOSトランジスタとトランスファMOSトランジスタとを備え、メモリセルを含むDRAMに使用される昇圧電位発生回路において、容量MOSトランジスタのゲート絶縁膜を、メモリセルを構成するMOSトランジスタのゲート絶縁膜の膜厚よりも薄い膜厚にすることにより、小面積で大容量の昇圧電位発生回路を実現する。この場合、トランスファMOSトランジスタのゲート絶縁膜の厚さを容量MOSトランジスタのゲート絶縁膜の厚さを同等以上に厚くすることが好ましい。

(もっと読む)

半導体記憶装置

【課題】 多ビットのデータを入出力可能であって、動作速度の遅延や消費電力の増大を抑えたDRAMを提供する。

【解決手段】 このDRAMでは、多数のグローバル入出力線対GIOがサブワードドライバ領域24間のメモリセルアレイ上を走る。ローカル入出力線対LIOはメモリサブブロック26ごとに複数に分割される。グローバル入出力線対GIOとローカル入出力線対LIOを接続するスイッチング素子30はセンスアンプ領域22上に分散して配置される。1つのローカル入出力線対LIOには複数のビット線対が共通に接続される。

(もっと読む)

不揮発性半導体記憶装置

【課題】NANDセル型EEPROMのデータ消去後に、ビット線コンタクト部とセルPウエルとの接合の順方向電流によるラッチアップを防止する。

【解決手段】NANDセル型EEPROMにおいて、浮遊ゲートおよび制御ゲートを有する不揮発性のメモリセルを少なくとも1つ含むメモリセルユニットと、メモリセルユニットが形成されるメモリセルウエルCPWELL、CNWELLと、メモリセルユニットの一端に接続された第1の信号線BLi と、メモリセルユニットの他端に接続された第2の信号線CELSRCと、メモリセルの記憶データを消去する際、メモリセルウエルに消去電圧を所定期間印加して消去動作を行わせた後、第1の信号線および第2の信号線をフローティング状態にして、メモリセルウエルの消去電圧を放電させるように制御する制御回路を具備する。

(もっと読む)

881 - 888 / 888

[ Back to top ]