Fターム[5F083LA05]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | ローデコーダ(ワード線昇圧回路等を含む) (888)

Fターム[5F083LA05]に分類される特許

101 - 120 / 888

半導体装置

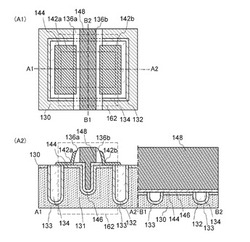

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

抵抗変化型不揮発性記憶装置

【課題】メモリセルのトランジスタのサイズを最適化可能とした抵抗変化型不揮発性記憶装置を提供する。

【解決手段】下部電極309aと上部電極309cと両電極間に与えられる極性の異なる電気的信号に基づいて高抵抗状態と低抵抗状態とを可逆的に変化する抵抗変化層309bとからなる抵抗変化素子309と、半導体基板301と2つのN型拡散層領域302a、302bとからなるトランジスタ317とを直列に接続してなるメモリセル300を備え、抵抗変化層309bは酸素不足型の遷移金属の酸化物層からなり、下部電極309aと上部電極309cは、異なる元素からなる材料によって構成され、下部電極309aの標準電極電位V1と上部電極309cの標準電極電位V2と前記遷移金属の標準電極電位VtとがVt<V2かつV1<V2なる関係を満足し、下部電極309aとN型拡散層領域302bとが接続されている。

(もっと読む)

抵抗変化型メモリ

【課題】メモリの動作マージンを向上する。

【解決手段】本実施形態の抵抗変化型メモリは、ビット線BLA,BLC間に接続された第1のセルSCAとビット線BLB,BLC間に接続された第2のセルSCBとを含むメモリセルMCと、第1のセルSCAを形成するメモリ素子8A及び選択トランジスタTrAと、第2のセルSCBを形成するメモリ素子8B及び選択トランジスタTrBとを具備し、メモリセルに対する書き込み動作時、ワード線が活性化されている期間において、メモリセルMC内の2つのメモリ素子8A,8Bを第1の抵抗状態に変化させた後、2つのメモリ素子8A,8Bのうち一方のメモリ素子を第2の抵抗状態に変化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流の発生を防止でき、微細化に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、素子分離膜により分離される素子領域を有する半導体基板31と、前記素子領域上にゲート絶縁膜を介して設けられる第1導電層FGと、前記第1導電層および前記素子分離膜上に設けられ、前記第1導電層上に開口を有するゲート間絶縁膜IPDと、前記ゲート間絶縁膜を介して、前記素子領域上および前記素子分離膜上にわたって配置される第2導電層CG1と、前記第1導電層上に設けられ、周囲の溝により前記第2導電層と電気的に分離され、前記ゲート間絶縁膜の前記開口を介して前記第1導電層と接続される第3導電層CG2と、前記第1導電層を挟むように、前記素子領域中に隔離して設けられるソースまたはドレイン拡散層38とを具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリ容量を容易に調整することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、Y方向に配列された4つのP型ウェルPWのうちの端の1つのP型ウェルPWに複数のメモリブロックMB0〜MB3を設け、残りの3つのP型ウェルPWにそれぞれ3つのメモリブロックMB10〜MB12を設ける。また、それぞれメモリブロックMB0〜MB3,MB10〜MB12のX方向に隣接してロウデコーダRD0〜RD3,RD10〜RD12を設ける。メモリブロックMB10〜MB12を削除してメモリ容量を減らす場合でも、周辺回路の再レイアウトが不要となる。

(もっと読む)

半導体記憶装置

【課題】メモリアレイの周辺に配置される周辺回路の専有面積を小さくすることができる半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、メモリアレイと、周辺回路と、を備える。メモリアレイは、複数のメモリセルと、複数のワード線と、複数のビット線と、を有し、4つのブロックを有する。周辺回路は、第1ブロックに属するワード線に接続された第1転送トランジスタと、第2ブロックに属する前記ワード線に接続された第2転送トランジスタと、第3ブロックに属するワード線に接続された第3転送トランジスタと、を含むトランジスタグループを有する。第1〜第3転送トランジスタにおいては、それぞれのソース及びドレインのいずれか他方を共有し、ソース及びドレインのいずれか一方と他方とをむすぶ方向が隣り合う転送トランジスタどうしで互いに90°または180°異なる。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な半導体装置を提供する。

【解決手段】P型の半導体基板10と、半導体基板10内に形成されるNウェル11、半導体基板10内かつNウェル11上に形成されるPウェル12、及びPウェル12上に形成されるメモリセルトランジスタMTを含むCell領域と、半導体基板10内に形成されるNウェル14、及びNウェル上14に形成されるトランジスタHVP−Trを含むHVP−Tr領域と、半導体基板10上に形成されるトランジスタHVN―Trを含むHVN―Tr領域と、半導体基板10内に形成されるNウェル22、半導体基板10内かつNウェル22上に形成されるPウェル23、およびPウェル23上に形成されるトランジスタLVNE−Trを含むLVNE−Tr領域と、を具備し、Nウェル11及びNウェル22の底面の位置はNウェル14の底面の位置よりも低く、Nウェル14の底面の位置はPウェル12及びPウェル23の底面の位置よりも低い。

(もっと読む)

半導体装置及び情報処理システム

【課題】ビット線構成が階層化されたメモリセルアレイにおいて、回路規模が小さくチップ面積の増加及びタイミングスキューを抑制可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ビット線構成がローカルビット線LBLとグローバルビット線GBLとに階層化され、ローカルビット線LBLとグローバルビット線GBLとの間の接続を制御する階層スイッチSWを備えている。階層スイッチSWの制御のため、ローカルスイッチ制御線LSLとメインスイッチ制御線MSLが配置される。ローカルスイッチ制御線LSLはローカルスイッチドライバLSDにより駆動され、メインスイッチ制御線MSLはメインスイッチドライバMSDにより選択的に活性化される。メモリセルアレイの規模が大きくなっても、ローカルスイッチドライバLSDとメインスイッチドライバMSDの配置によるレイアウト面積の増大及びタイミングスキューを抑制することができる。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

可変抵抗素子及びその製造方法、並びに、当該可変抵抗素子を備えた不揮発性半導体記憶装置

【課題】 フォーミング電圧の素子間ばらつきを低減しつつ、フォーミング電圧を低減できる構成の可変抵抗素子およびその製造方法、並びに当該可変抵抗素子を備えた高集積の不揮発性半導体記憶装置を提供する。

【解決手段】

可変抵抗素子2は、第1電極15と第2電極12の間に抵抗変化層(第1の金属酸化物膜)13、及び、第1電極15と接する制御層(第2の金属酸化物膜)14を挟持して構成される。制御層14は、仕事関数が小さく(4.5eV以下)、抵抗変化層から酸素を引き抜く能力を有する金属の酸化膜で構成される。第1電極は、当該金属と同様に仕事関数が小さい金属で構成されるが、尚且つ、制御層からの酸素の熱拡散を抑制するために、その酸化物生成自由エネルギーが、制御層を構成する元素の酸化物生成自由エネルギーよりも大きな材料で構成される。

(もっと読む)

半導体記憶装置

【課題】抵抗値の変化によって情報を記憶する積層型の半導体記憶装置において、メモリセル間の抵抗を抑制したメモリアレー構造を提供することを目的とする。

【解決手段】本発明に係る半導体記憶装置は、上側の第1半導体層と下側の第1半導体層との間に第2半導体層が積層された積層体を有し、第1半導体層を導通状態とする電位が第1半導体層に印加されている状態と印加されていない状態の双方において、第2半導体層を導通状態とする電位が印加されるように構成されている。

(もっと読む)

不揮発性半導体記憶装置及びフォーミング方法

【課題】フォーミング処理の時間を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】複数の不揮発性メモリセルは、可変抵抗素子及び整流素子が直列接続されている。制御部は、第1のタイミングにおいて、Nを1以上の整数とするとき複数のワードラインからN本おきに第1のラインを多重選択して選択電位に設定するとともに、少なくとも多重選択されたワードラインに隣接する非選択のワードラインの電位を固定する。制御部は、第2のタイミングにおいて、上記の多重選択されたワードラインを浮遊状態にする。第2のタイミングは、第1のタイミングより後のタイミングである。制御部は、第3のタイミングにおいて、複数のビットラインから1本の第2のラインを選択してフォーミング電位に設定する。第3のタイミングは、第2のタイミングより後のタイミングである。

(もっと読む)

半導体記憶装置

【課題】フィンに閉じ込められたホールの保持特性を向上させることが可能な半導体記憶装置を提供する。

【解決手段】フィン3は半導体基板1上に形成され、ゲート電極Gは、フィン3の両側にゲート絶縁膜5を介して設けられ、空乏層KUは、フィン3のチャネル領域間のボディ領域にホールを閉じ込めるポテンシャルバリアをフィン3内に形成し、ソース層Sとドレイン層Dは、ゲート電極Gを挟み込むようにしてフィン3に形成されている。

(もっと読む)

抵抗変化型不揮発性記憶装置

【課題】メモリセルのトランジスタのサイズを最適化可能とした抵抗変化型不揮発性記憶装置を提供する。

【解決手段】下部電極309aと上部電極309cと抵抗変化層309bとからなる抵抗変化素子309と、トランジスタ317とを直列に接続してなるメモリセル300において、トランジスタ317は、ゲート303bと、下部電極309aに電気的に接続されたドレイン又はソース302bと、ソース線SL0に電気的に接続されたソース又はドレイン302aとを有し、ソース線SL0は、互いに平行に配置されかつ1つ以上のビアで接続された複数のレイヤーで形成される配線層305、307からなり、抵抗変化素子309はいずれの配線層305、307よりも半導体基板301からより遠い側に配置され、ビット線BL0は、抵抗変化素子309に対し、半導体基板301からより遠い側に配置され上部電極309cと接続される。

(もっと読む)

半導体装置

【課題】相変化メモリを低電圧動作および高温の動作又は放置させる場合に、記録保持信頼性を向上させる技術を提供する。

【解決手段】読み出し電圧をセット電圧およびリセット電圧以上として高速動作させ、読み出し後に読み出し前の状態を再書込みする、いわゆる破壊読出しを行う。または、複数個のセルを用いて1ビットの情報を記録する、いわゆるオアセルを用いて、高温時の動作又は放置のける信頼性を向上させる。破壊読出しおよびオアセルを用いた相変化メモリに必要な、回路構成および動作方法を用いる。

(もっと読む)

半導体装置

【課題】 電源遮断機能付きで記憶容量の増減変更を伴う設計が容易なSRAMマクロを有する半導体装置を提供する。

【解決手段】 本発明の半導体装置では、SRAMのメモリセルが複数配置されているメモリアレイと、メモリアレイへのデータの書き込みおよびメモリアレイからのデータの読み出しを行う第1の周辺回路と、メモリアレイおよび第1の周辺回路と電源線との接続を遮断するスイッチ群とを含むレイアウトの単位が複数配置されている。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bとを有する。駆動対象の記憶素子21に対して、電極215Aと電極215Bとの間に所定の閾値以上の電圧V1を印加して、半導体層212Nと半導体層213Nとの間の領域にそれらの半導体層同士を電気的に繋ぐ導電パスであるフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ゲートの端部に集中する電界を緩和し、電荷のトラップおよびトンネル絶縁膜の破壊を抑制し、信頼性を向上させる。

【解決手段】半導体記憶装置は、半導体基板上に設けられたアクティブエリアを備えている。素子分離部が、アクティブエリア間に設けられ、絶縁膜で充填されている。データを記憶する複数のメモリセルがアクティブエリアに形成されている。空洞が、アクティブエリアのメモリセルが形成された部分の上端縁部と素子分離部内の絶縁膜との間に設けられている。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

101 - 120 / 888

[ Back to top ]