Fターム[5F083LA11]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019)

Fターム[5F083LA11]の下位に属するFターム

Fターム[5F083LA11]に分類される特許

1 - 20 / 222

半導体装置の製造方法及び半導体装置

記憶装置

半導体装置

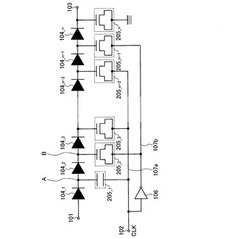

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ホールの微細化を図りつつ、ホールとスリットとを一括形成する。

【解決手段】4層分のワード線WL4〜WL1が順次積層されるとともに、ワード線WL4〜WL1にそれぞれ隣接するように4層分のワード線WL5〜WL8が順次積層され、ワード線WL5〜WL8が柱状体MP1にて貫かれるとともに、ワード線WL1〜WL4が柱状体MP2にて貫かれることで、NANDストリングNSが構成され、ワード線WL1〜WL8およびセレクトゲート電極SGD、SGSはロウ方向に沿って幅が周期的に変化されている。

(もっと読む)

半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜とゲート絶縁膜との界面において、電子の界面散乱を抑制することで、電気的特性に優れたトランジスタを提供する。

【解決手段】基板上に酸化物半導体膜を形成し、酸化物半導体膜上に酸化物半導体以外の半導体膜を形成した後、酸化物半導体膜と該半導体膜との界面において、酸化物半導体膜中の酸素原子と半導体膜中の原子とを結合させる。これにより、酸化物半導体膜と該半導体膜との界面において構造を連続させることができる。また、酸化物半導体膜から脱離した酸素が、該半導体膜に拡散することで、該半導体膜は酸化されるため、絶縁膜とすることができる。このようにして形成されたゲート絶縁膜を用いることで、酸化物半導体膜とゲート絶縁膜との界面において電子の界面散乱が抑制され、電気的特性に優れたトランジスタを作製できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線部に比べて引き出し部のスペースが広い場合においても、引き出し部の線幅を配線部の線幅に均一化できるようにする。

【解決手段】側壁パターン2a、2bおよび側壁ダミーパターン2c、2dをマスクとして被加工膜5を加工することにより、側壁パターン2aに対応した配線を下地層4上の配線部R1に形成するとともに、側壁パターン2bに対応した引き出し線5bを下地層4上の引き出し部R2に形成する。この時、下地層4上の引き出し部R2には、側壁ダミーパターン2cに対応したダミー引き出し線5cが引き出し線5bに並列に形成されるとともに、側壁ダミーパターン2dに対応したダミー引き出し線5dが引き出し線5bに並列に形成される。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

メモリ用シフトレジスタ

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

半導体記憶装置

【課題】比較的小振幅な信号が伝送される第1の信号線対で発生するカップリングノイズを低減しつつ、該第1の信号線対と直交する方向に異なる配線層で配置される、第1の信号線対よりも振幅が大きい信号が伝送される第2の信号線毎の信号遅延量の差異を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリアレイ上で配線される第1の振幅信号が伝送される複数の第1の信号線対と、該第1の信号線対と直交する方向に異なる配線層で配置される複数の第2の信号線とを有する。第1の信号線対は、メモリマットの列毎に配置され、メモリマットの列方向において、それぞれ所定の一定間隔で交差される。また、第1の信号線対の交差部位は第2の信号線の配線方向におけるメモリマットの列毎にずらして配置される。

(もっと読む)

メモリ装置

【課題】大容量化が容易であり、高収率且つ高信頼性を有する半導体メモリ装置が提供される。

【解決手段】本発明に従うメモリ装置は、記憶素子と前記記憶素子にデータを書き込むか、又は読み出す周辺回路を含む第1半導体チップ、及び外部と前記第1半導体チップとの間で交換されるデータ又は信号の入出力機能を遂行する第2半導体チップを含み、本発明のその他の特徴に従うメモリ装置は、外部とデータ又は信号を交換するための入出力回路チップ、及び各々前記入出力回路チップから提供される信号に応答して前記データを格納するか、或いは内部に格納されたデータを読み出して前記入出力回路チップへ出力する、垂直方向に積層される複数のコアチップを含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】比較的高い抵抗率を持つ導電体を電極に用いた場合でも、高信頼な抵抗変化素子を実現する。

【解決手段】不揮発性半導体記憶装置は、第1配線54と、第2配線55と、一端を前記第1配線54に、他端を前記第2配線55にそれぞれ電気的に接続されたメモリセル40とを具備する。メモリセル40は、抵抗値の変化で情報を記憶する抵抗変化層41と、抵抗変化層41の両端にそれぞれ接続され、貴金属を含まない第1電極51及び第2電極52とを備える。第1電極51は、外側電極43と、外側電極43と抵抗変化層41との間に設けられた界面電極42とを含む。界面電極42の膜厚は、外側電極43の膜厚よりも薄い。界面電極42の抵抗率は、外側電極43の抵抗率よりも高い。第1電極51の抵抗値Rsは、抵抗変化層52の低抵抗状態の抵抗値Ronよりも低い。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

半導体装置

【課題】抵抗変化型記憶素子を用いた半導体装置の耐タンパ性を向上させること。

【解決手段】半導体装置は、1ビットのセルデータを記憶するユニットセル(10)と、制御回路(100)とを備える。ユニットセル(10)は、n個(nは2以上の整数)の抵抗変化型記憶素子(31)を備える。それらn個の抵抗変化型記憶素子(31)のうち少なくとも1つが、セルデータが記録される有効素子(40)である。セルデータの読み出し時、制御回路(100)は、少なくとも有効素子(40)を選択し、有効素子(40)に記録されているデータをセルデータとして読み出す。

(もっと読む)

1 - 20 / 222

[ Back to top ]