Fターム[5F083MA00]の内容

半導体メモリ (164,393) | コンタクト (12,929)

Fターム[5F083MA00]の下位に属するFターム

Fターム[5F083MA00]に分類される特許

1 - 2 / 2

半導体装置及びその製造方法

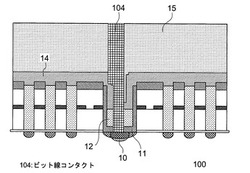

【課題】コンタクトの底部位置が高濃度不純物拡散層からはみ出すことを防止する半導体装置を提供する。

【解決手段】半導体基板100と、複数のメモリセルトランジスタ1と両端にそれぞれ1つずつ配置された選択トランジスタ2とからなるメモリセルアレイCAと、隣接する選択トランジスタ2間の前記半導体基板表面部に形成された拡散層10と、選択トランジスタ2の対向する各側壁に形成された側壁膜11と、側壁膜11上に形成された側壁膜14と、前記メモリセルトランジスタ間、前記メモリセルトランジスタと前記選択トランジスタの間、及び前記選択トランジスタ間を埋め込むように形成された絶縁層12と、拡散層10にコンタクトする導電層104と、を有し、前記導電層のコンタクト部のエッジが、選択トランジスタ2の側壁から、側壁膜11、14の合計膜厚以上の位置にある。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタ下部電極の直下のコンタクトプラグの歩留まりが向上し、それ以外のコンタクトプラグの設計が容易になる半導体装置とその製造方法を提供すること。

【解決手段】第1の絶縁膜8の第1のホール内8aに形成された第1の導電性プラグ10aと、第1の絶縁膜8上に形成された酸化防止絶縁膜11a及び下地絶縁膜11bと、第1の絶縁膜8、酸化防止絶縁膜11a、及び前記下地絶縁膜11bに形成された第2のホール8bと、第2のホール8b内に形成された第2の導電性プラグ12aと、第2の導電性プラグ12aに接続されたキャパシタQ1と、キャパシタQ1上に形成された第2の絶縁膜18と、第1の導電性プラグ10a上に形成された第3のホール19aと、第3のホール19a内に形成された第3の導電性プラグ21aとを有する半導体装置による。

(もっと読む)

1 - 2 / 2

[ Back to top ]