Fターム[5F083MA02]の内容

Fターム[5F083MA02]の下位に属するFターム

ゲート側壁絶縁膜を利用 (268)

Fターム[5F083MA02]に分類される特許

1 - 20 / 115

半導体装置およびその製造方法

【課題】電流―電圧特性の向上およびオン電流を増大することが可能で、高速動作に優れた半導体装置及びその製造方法を提供する。

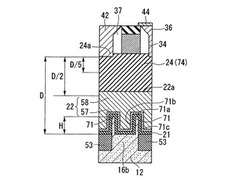

【解決手段】半導体基板12の主面に形成され、第1の方向に延在する複数の活性領域と、活性領域を区画する素子分離領域と、半導体基板12の主面に形成されたものであって、平面視して複数の活性領域に交差する方向に延在する複数のゲート溝と、ゲート溝のそれぞれに埋め込まれた複数のゲート電極22と、を備えた半導体装置であって、ゲート溝のそれぞれの底面には、第1の方向に延在すると共に、上面71aが半導体基板12の主面よりも低い位置に配置する一対の突起部71が形成されており、ゲート電極22は、ゲート絶縁膜21を介して突起部71の上面71aと内側面71bと外側面71cとを覆ってなる、ことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】埋込ワード線の高さにばらつきのない半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、複数の素子分離領域を形成すると共に、素子分離領域間に素子形成領域を形成する工程と、素子形成領域に交差する第1の方向に延在するゲート電極溝を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を介して第1導電膜を形成する工程と、ゲート電極溝内を埋め込むように第2導電膜を形成する工程と、第2導電膜上に平坦化膜を形成する工程と、第2導電膜が露出するように平坦化膜をエッチングして除去する第1のエッチング工程と、第2導電膜がゲート電極溝の下部に残留するように第2導電膜をエッチングする第2のエッチング工程と、第1導電膜が前記ゲート電極溝の下部に残留するように第1導電膜をエッチングする第3のエッチング工程と、を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極用溝18の底部に設けられた第1の不純物拡散領域27と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第2の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように半導体基板13に設けられ、第1の不純物拡散領域27と接合された第3の不純物拡散領域29と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル抵抗を減少させてオン電流を増加させることが可能で、各トランジスタを独立して安定して動作させることの可能な半導体装置を提供する。

【解決手段】ゲート電極用溝18の底部18cから突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆う第1の不純物拡散領域28と、第2の側面18bに配置されたゲート絶縁膜21の下端部以外の部分を覆う第2の不純物拡散領域29とを備え、ゲート電極用溝18の深さが半導体基板13の表層13aから150〜200nmであり、ゲート電極用溝18の底部18cからフィン部15の上部15aまでの高さが10〜40nmである。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、接合リーク電流を低減可能で、かつトランジスタの信頼性を向上させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極61よりも上方に配置されたゲート絶縁膜21、及びゲート電極61の上面61aを覆う水素含有絶縁膜62と、水素含有絶縁膜62を介して、ゲート電極用溝17の上部17Bを埋め込むフッ素含有絶縁膜63と、を備え、ゲート絶縁膜21と接触する第1及び第2の不純物拡散領域65,66の面に、半導体基板13に含まれるシリコンと水素含有絶縁膜62に含まれる水素とが結合したSi−H結合、及び半導体基板13に含まれるシリコンとフッ素含有絶縁膜63に含まれるフッ素とが結合したSi−F結合を有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】シリンダ型下部電極の剥がれ落ちを防止する、半導体装置の製造方法を提供する。

【解決手段】複数の第1の開口を有するコア絶縁膜を半導体基板上に形成し、複数の第1の開口の側面を導電膜で覆う、シリンダ状の複数の下部電極を形成し、少なくとも複数の下部電極間のコア絶縁膜の上面を覆うサポート膜を形成し、サポート膜を用いて少なくとも複数の下部電極が形成される領域の外側を除去したマスク膜を形成し、マスク膜を形成した後、複数の下部電極間の一部にコア絶縁膜が残るように、コア絶縁膜に対して等方性エッチングを行うものである。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

半導体装置及び半導体装置を用いたデータ処理システム

【課題】補償容量素子を構成する複数のクラウン型下部電極を備えた容量ブロック間を上部電極で直列接続する際、容量ブロック間に空洞が形成されることを防止する。

【解決手段】2つの隣接する、異なる共通パッド電極(22c、22d)上に形成された容量ブロック(第1ブロック及び第2ブロック)が、上部電極36cで電気的に直列に接続され、上部電極36cで直列接続される2つの隣接する容量ブロック間の間隔D1を、それぞれの容量ブロックの最外周で対向する下部電極間の距離として、2つのブロック間に埋設される上部電極膜の膜厚の2倍以下とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、トランジスタを容易にOn(オン)させることが可能で、かつ良好なデータ保持特性を実現することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板12に形成され、第1の方向に延在する第1の素子分離用51、及び第1の素子分離用溝51を埋め込む第1の素子分離用絶縁膜53よりなり、複数の素子形成領域Rを有した活性領域16を区画する第1の素子分離領域14と、半導体基板12に、第1の方向と交差する第2の方向(Y方向)に延在するように形成され、第1の素子分離領域14の一部を分断する第2の素子分離用溝54、及び第2の素子分離用溝54を埋め込む第2の素子分離用絶縁膜56よりなり、複数の素子形成領域Rを区画する第2の素子分離領域17と、を有する。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

半導体装置の製造方法

【課題】微細な配線を高アスペクト比かつ高密度で形成できる、半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜に隣り合う第1配線溝と第2配線溝を形成し、第1配線溝内に第1配線とその上の空間および第2配線溝内に第2配線とその上の空間を設け、等方性エッチングを行って、第1配線溝の幅が拡大されてなる第1マスク溝と第2配線溝の幅が拡大されてなる第2マスク溝を形成し、第1マスク溝及び第2マスク溝にマスク用絶縁材料を充填して、第1マスク溝内の第1マスク絶縁膜と第2マスク溝内の第2マスク絶縁膜を形成し、第1マスク絶縁膜及び第2マスク絶縁膜をマスクとして利用する異方性エッチングを行って、第1配線と第2配線との間を通過し上記層間絶縁膜を貫通するホールを、第1マスク絶縁膜と第2マスク絶縁膜に対して自己整合的に形成し、このホールに導電材料を充填してプラグを形成する、半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、コンタクトプラグと埋め込み型のゲート電極との間に配置される絶縁膜の厚さを十分に確保可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜16を介して、半導体基板11に形成された凹部14の凹部14の一部を埋め込むゲート電極41と、ゲート電極41の上端面41aを覆うように凹部14内を埋め込む絶縁膜18と、凹部14の一方の側面14a側に位置する半導体基板11の主面11aに形成された不純物拡散領域43と、不純物拡散領域43の上面43aを覆うシリコン層21と、半導体基板11の主面11aに形成された第1及び第2の層間絶縁膜23,31に内設され、シリコン層21の上面21aと接触し、かつ下端34bがシリコン層21の上面21aと絶縁膜18の上面18aとの間に配置されたコンタクトプラグ34と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

対向電極を有する小型電界効果トランジスタおよび製造方法

【課題】小型化の増進を可能にするとともに、実現が容易な、対向電極を備えた電界効果トランジスタの製造方法を提供する。

【解決手段】ゲート電極9ソースコンタクト12,ドレインコンタクト13、および対向電極コンタクトの輪郭描写パターンを含むエッチングマスクが、セミコンダクタ・オン・インシュレータ型の基板上に形成される。基板は、誘電体5の層およびゲート材料により覆われる。対向電極コンタクトは、ゲート電極9のパターン内に配置される。ゲート材料は、ゲート電極9、ソースコンタクト12およびドレインコンタクト13、ならびに対向電極コンタクトを画定するためにエッチングされる。支持基板2の一部分は、対向電極コンタクト領域のパターンの中を通って解放される。導電性材料22が支持基板2の自由部分上に堆積されて、対向電極コンタクトを形成する。

(もっと読む)

半導体装置の製造方法

【課題】簡易な追加工程を設けることで、基板のベベル部から膜が剥離することを抑制する。半導体装置の製造歩留まりの低下を抑制すると共に、製造コストの増加を抑制する。

【解決手段】半導体基板上の全面に、1以上の膜を有する構造を形成した後、膜構造上にパターンを有する第1のマスクを形成する。ベベル部上の第1のマスクを覆うように第2のマスクを形成する。第1のマスク及び第2のマスクを用いて、膜構造をエッチングした後、残留した第1のマスク及び第2のマスクを除去する。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離溝内に絶縁膜を埋め込んでなる素子分離膜に発生するボイドなどの埋め込み不良を防止する。

【解決手段】素子分離膜8によって区画された素子形成領域10aが、第1帯部141と第2帯部142と複数の素子形成部1aとを有し、複数の素子形成部1aは、第1帯部側の端部と第1帯部とが接続された複数の第1接続形成部10bと、第1帯部側の端部と第1帯部とが離間して配置された複数の第1離間形成部10dと、第2帯部側の端部と第2帯部とが接続された複数の第2接続形成部10cと、第2帯部側の端部と第2帯部とが離間して配置された複数の第2離間形成部10eとを含み、隣接する第1接続形成部10bの間に第1離間形成部10dが配置されているとともに、隣接する第2接続形成部10cの間に第2離間形成部10eが配置されている半導体装置とする。

(もっと読む)

1 - 20 / 115

[ Back to top ]