Fターム[5F083MA15]の内容

Fターム[5F083MA15]の下位に属するFターム

複数の配線層間 (1,403)

拡散層とキャパシタ電極間 (1,386)

配線層とキャパシタ電極間 (481)

拡散層と配線層間 (3,894)

Fターム[5F083MA15]に分類される特許

1 - 20 / 105

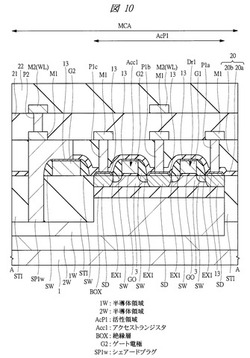

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1が配置される活性領域AcP1の下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wの底部および側部が、n型の半導体領域2Wと接するように配置し、p型の半導体領域1Wをn型の半導体領域2Wでpn分離し、アクセストランジスタAcc1のゲート電極G2とp型の半導体領域1Wを接続する。そして、この接続は、アクセストランジスタAcc1のゲート電極G2の上部からp型の半導体領域1Wの上部まで延在する一体の導電性膜であるシェアードプラグSP1wによりなされる。これにより、アクセストランジスタAcc1がオン状態の場合において、バックゲートであるp型の半導体領域1Wの電位が同時に高くなり、トランジスタのオン電流を大きくできる。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

可変抵抗絶縁層を用いたメモリ素子及びそれを有するプロセッサシステム

【課題】可変抵抗材料を用いて形成されるランダムアクセスメモリ装置を提供する。

【解決手段】可変抵抗メモリ装置301において、望ましい円錐状に形造された下部電極308は、下部電極308の頂点のところにおける絶縁材料312の厚さが最も薄く、下部電極308の頂点のところにおける電界が最大であることを確保する。電極308、310の配置およびメモリ素子の構造はメモリ装置内に安定で確実に導電路を作り出し、かつ、スイッチングとメモリ特性を再生可能にする。

(もっと読む)

固体メモリ

【課題】固体メモリの記録層として、これまで広く用いられているGe−Sb−Te系合金に代わって、希少金属であるSbフリーでありながら、Ge−Sb−Te系合金を用いた固体メモリと遜色のない性能を有する固体メモリを提供する。

【解決手段】固体メモリ10は、物質の相変化に起因して電気特性が変化する記録層11を備えた固体メモリであって、記録層11が、ゲルマニウムとテルル4とから形成されている薄膜、および、銅とテルルとから形成されている薄膜5が積層されてなる超格子によって構成されている。

(もっと読む)

不揮発性記憶素子および不揮発性記憶装置

【課題】電極と抵抗変化層の界面に小さな突起を形成することなく、低電圧での初期化が可能な不揮発性記憶素子を提供する。

【解決手段】下部電極105と上部電極107との間に介在され、両電極間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層116を備える。抵抗変化層116は、第1の抵抗変化層1161と第2の抵抗変化層1162との少なくとも2層から構成され、第1の抵抗変化層1161は第1の遷移金属酸化物116bから構成され、第2の抵抗変化層1162は、第2の遷移金属酸化物116aと第3の遷移金属酸化物116cとから構成され、第2の遷移金属酸化物116aの酸素不足度は第1の遷移金属酸化物116bの酸素不足度及び第3の遷移金属酸化物116cの酸素不足度のいずれよりも高く、第2の遷移金属酸化物116a及び第3の遷移金属酸化物116cは、第1の抵抗変化層1161と接している。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去状態におけるセル電流の値の変動を抑制可能な不揮発性半導体記憶装置の提供。

【解決手段】基板の主面に平行な第1の方向に延びるよう区画された複数の素子領域111と、前記素子領域上に形成された複数のメモリセルを含むメモリセルアレイ領域121と、前記第1の方向に延びるよう形成された複数のビット線131とを備え、前記複数のビット線の同じ側の端部に電気的に接続されたセンスアンプ回路141と、前記素子領域上に、前記素子領域と前記ビット線とを電気的に接続するよう形成された複数のビット線コンタクトCBとを備える。前記メモリセルアレイ領域は、第1から第Nの領域(N≧2)を含み、第Kの領域(2≦K≦N)は、第K−1の領域よりも前記センスアンプ回路から遠い位置に位置し、前記第Kの領域内の前記ビット線コンタクトのコンタクト抵抗は、前記第K−1の領域内の前記ビット線コンタクトのコンタクト抵抗よりも低い。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域の表面には、薄い不純物濃度の第1導電型の領域を形成した。

(もっと読む)

半導体装置およびその製造方法

【課題】相変化記録素子のまわりを伝導率の低い真空の空隙部で覆うことで、さらに高い発熱効率を得ることができ、書き換え電流を低減することができる半導体装置を提供する。

【解決手段】半導体基板と、半導体基板の上に形成されたスイッチング素子を含む素子層と、素子層上において、スイッチング素子に接続されたヒータ電極11、ヒータ電極11の熱によって相転移する相変化記録材料層12及び上部電極13が順次積層されてなる相変化記録素子10と、相変化記録素子10の上に積層された層間絶縁膜21bと、素子層と層間絶縁膜21bの間にあってヒータ電極11または相変化記録材料層12のいずれか一方又は両方の周囲に形成された真空の空隙部15と、を具備してなる。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗変化素子を半導体装置に組み込む際の必要なフォトマスクを削減しても高密度化が可能な抵抗変化素子を搭載した半導体装置及びその製造方法を提供すること。

【解決手段】配線溝を有する層間絶縁膜14と、配線溝に埋め込まれた配線16aと、配線16aを含む層間絶縁膜14上に形成されるとともに、配線16aに通ずる下穴を有する層間絶縁膜18と、少なくとも下穴が配置された領域における配線16a上に形成されるとともに、抵抗が変化する抵抗変化膜19aと、下穴が配置された領域における抵抗変化膜19a上に形成されたバリアメタル20aと、下穴が配置された領域におけるバリアメタル20a上に形成されたプラグ21aと、を備え、抵抗変化素子5は、第1電極と第2電極との間に抵抗変化膜19aが介在した構成となっており、配線16aは、第1電極を兼ね、バリアメタル20aは、第2電極を兼ねる。

(もっと読む)

半導体装置およびその製造方法

【課題】相変化材料層をヒータ電極で加熱して抵抗値を変化させ、情報の記憶を行う相変化メモリを備える半導体装置において、工程数を削減してヒータ部の電流密度を高くする製造方法並びに構造を提供する。

【解決手段】ヒータ電極10を覆う層間絶縁膜13に、ヒータ電極10上面と同形状であり、全面を露出する開口部が形成されており、開口部に絶縁材料からなるサイドウォール15が形成されており、相変化材料層16は、サイドウォール10の形成された開口部内でヒータ電極10と接触しており、相変化材料層16における相変化領域18はサイドウォール10で囲まれた開口部内に形成される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】積層体を貫いて積層体の上下をつなぐコンタクト構造の形成を容易にする半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、基板11と基板11の表面に形成された周辺回路とを有する基体10と、基体10上にそれぞれ交互に積層された複数の導電層WLと複数の絶縁層25とを有する積層体と、積層体を貫通して最下層の導電層BGに達するメモリホールの内壁に設けられた電荷蓄積膜を含むメモリ膜30と、メモリホール内におけるメモリ膜30の内側に設けられたチャネルボディ20と、積層体の下に設けられメモリ膜30及びチャネルボディ20が設けられたメモリセルアレイ領域2の外側にレイアウトされた配線領域4における最下層の導電層63と周辺回路とを電気的に接続する配線BLと、配線領域4の積層体を貫通して配線領域の最下層の導電層63に達するコンタクトプラグ67と、を備えた。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

情報処理方法、積層型集積回路メモリ

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる。

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

相変化メモリ・セル、形成方法、及び形成装置

【課題】 相変化メモリ・セル内に、ボイドがない結晶相変化材料を形成する方法を提供する。

【解決手段】 相変化メモリ・セルを形成するための技術である。例示的な方法は、基板内に下部電極を形成するステップを含む。本方法は、下部電極の上に相変化材料を形成するステップを含む。本方法は、キャッピング層及び絶縁体層を形成するステップを含む。本方法は、相変化層内の相変化材料を結晶化させて、相変化層にボイドがなくなるようにするステップを含む。本方法は、下部電極から、相変化層内の相変化材料を加熱するステップをさらに含み、結果として、相変化層が下部から上部へと結晶化する。一実施形態において、相変化材料を結晶化させるために、急速熱アニール(RTA)を適用する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域中の層間絶縁膜を湿式エッチングにより除去する際に、使用する薬液が第2の領域に浸透することを防止する。これにより、第2の領域の特性の劣化がない、高性能の半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた第2の領域と、を有する半導体装置。第1の領域は、導電性を有する第1の膜によって構成された第1の電極を有する。第1の領域中の第1の電極の表面は、第2の膜で覆われていない。ガードリングは、凹状の溝の内壁を覆う第1の膜と、凹状の溝の内部において少なくとも第1の膜の表面の一部を覆う絶縁性の第2の膜を有する。

(もっと読む)

不揮発性半導体メモリデバイス

【課題】ダイナミック放電読み出しでセンスタイミングのずれを是正する。

【解決手段】センスアンプ7Bは、メモリセル抵抗Rcellの一方の電極が接続されたビット線BLの放電電位を参照電位Vrと比較して情報を読み出す。セット容量スイッチ18S、リセット容量スイッチ18Rおよび追加容量Coffsetとその制御手段によって、センスノード(電位Vo)の負荷容量、または、センスノードと参照電位Vrを入力する参照ノードの負荷容量との両方を、メモリセル抵抗Rcellの読み出す情報の論理(通常読み出し、書き込みまたは消去のヴェリファイ読み出しの相違)に応じて変化させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造工程の簡略化および製造時間短縮を目的とする、メモリセルと周辺回路を備える半導体装置と製造方法を提供する。

【解決手段】トランジスタ形成層30上に、内部に配線10bを備え、かつ、表面に容量パッド14a,14bを有する絶縁層32を形成する工程と、絶縁層32を層間絶縁膜16で覆い、層間絶縁膜16を貫通する第一のホール16aと、第一のホール16aよりも大きい直径を有する第二のホール16bおよび第三のホール16cを、それぞれメモリセル部と周辺回路部に同時に形成する工程と、各ホール内を覆う下部電極18と容量絶縁膜19と上部電極20と容量サポート21を形成することにより第一のホール16aを充填するとともに、第二のホール16bと第三のホール16c内側に空洞を形成する工程と、空洞内に、配線10bと容量パッド14bにそれぞれ接続するコンタクト16d,16eを形成する工程と、を具備している。

(もっと読む)

半導体記憶装置及びデータ処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置においてリフレッシュ動作時におけるピーク電流を低減する。

【解決手段】予め互いに異なるチップ情報LIDが付与される複数のコアチップCC0〜CC7を備え、内部リフレッシュコマンドREFaを互いにタイミングの異なる複数のリフレッシュコマンドREFbに分割し、分割されたリフレッシュコマンドREFbのカウント値C2とチップ情報LIDの少なくとも一部とが互いに一致したコアチップにおいてリフレッシュ動作が実行される。これにより、複数のコアチップCC0〜CC7に内部リフレッシュコマンドREFbが共通に供給される場合であっても、各コアチップにおけるリフレッシュ動作のタイミングをずらすことが可能となる。これにより、リフレッシュ動作時におけるピーク電流を低減することが可能となる。

(もっと読む)

半導体記憶装置

【課題】層間接続により生ずるチップ面積の増大を抑制し、コスト削減を実現する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、前記半導体基板上に前記半導体基板と垂直方向にそれぞれ複数層形成された互いに交差する複数の第1及び第2の配線、並びにこれら第1及び第2の配線の各交差部に接続された複数のメモリセルを有するセルアレイブロックと、前記セルアレイブロックの第n層目(nは自然数)の第1の配線と前記第n層目の第1の配線以外の第1の配線、前記半導体基板、又は他の金属配線とを接続する前記セルアレイブロックの積層方向に延びる第1のビア配線とを備える。前記第1のビア配線は、前記セルアレイブロックの積層方向と直交する断面が楕円形状であり、この断面の長径方向が前記第1の配線方向に対し垂直であることを特徴とする。

(もっと読む)

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

1 - 20 / 105

[ Back to top ]