Fターム[5F083NA01]の内容

Fターム[5F083NA01]に分類される特許

2,001 - 2,020 / 3,470

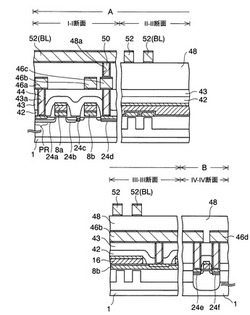

半導体装置とその製造方法

【課題】熱酸化膜の増速酸化に伴って発生する不都合を回避することが可能な半導体装置とその製造方法を提供すること。

【解決手段】フローティングゲート8a、中間絶縁膜12、及びコントロールゲート16aを備えたフラッシュメモリセルFLを形成する工程と、第1、第2不純物拡散領域24a、24bを形成する工程と、シリコン基板1とフローティングゲート8aの表面を熱酸化する工程と、レジストパターン39の窓39bを通じて一部領域PRにおけるトンネル絶縁膜5をエッチングする工程と、一部領域PRにおける第1不純物拡散領域24a上に金属シリサイド層40を形成する工程と、フラッシュメモリセルFLを覆う層間絶縁膜43を形成する工程と、層間絶縁膜43の第1ホール43a内に、金属シリサイド層40に接続された導電性プラグ44を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】浮遊ゲート電極間の制御ゲート電極の空乏化を大幅に抑制できて、読み出しエラーが起こりにくい多値型を含むNOR型のフラッシュメモリ等の不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】複数のメモリセル4を、互いに一方向に間隔をおくように配置する。制御ゲート電極2のONO膜22の側面に上記一方向に重なる部分24を、不純物がドープされた多結晶シリコンで形成する。制御ゲート電極2の上記一方向に重なる部分24において、多結晶シリコンの不純物濃度を、1020/cm3以上かつ1021/cm3以下に設定することで、浮遊ゲート電極10間の制御ゲート電極2の空乏化を大幅に抑制でき、隣接セルの浮遊ゲート電極10間の容量結合による閾値変動を急激に小さくする事ができ、隣接セルの閾値の干渉を受けないようにできる。

(もっと読む)

半導体装置及びその製造方法

【課題】 シェアードコンタクトがエクステンションに接触することによるジャンクションリークを抑制することができ、且つ面積の増大や抵抗の上昇を招くことなくコンタクトを取る。

【解決手段】 シェアードコンタクトを有する半導体装置において、半導体基板101上にゲート絶縁膜103を介して形成されたゲート電極104と、ゲート電極104の両側面に形成された側壁絶縁膜105,106と、基板101のゲート電極104の両側に隣接する表面部の少なくとも一方が側壁絶縁膜105,106の下部を越えてゲート電極104の下に達するまで除去され、且つ該除去部分に露出するゲート絶縁膜103が除去され、半導体基板101及びゲート絶縁膜103が除去された部分に形成された不純物ドープの半導体層119とを備えた。

(もっと読む)

半導体記憶装置

【課題】本発明は、NOR型のフラッシュメモリ装置において、リソグラフィによるパターン解像性/寸法制御性を改善できるとともに、より安定した動作を可能にする。

【解決手段】たとえば、ビット線BLに並設して、メインソース線MSLが設けられている。メインソース線MSLは、隣接するビット線BL間に、ビット線BL,BL間の間隔と同一の間隔を有している。隣り合うワード線WL1,WL2間において、各ビット線BLの直下には、ドレインコンタクトプラグにつながる第1のドレインヴィアプラグDV1が設けられている。一方、メインソース線MSLの直下には、ダミーコンタクトプラグにつながる第2のドレインヴィアプラグDV2が設けられている。

(もっと読む)

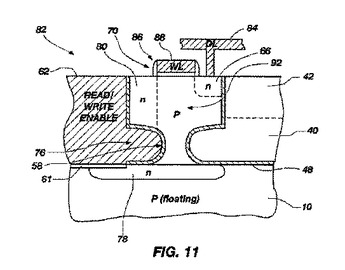

パストランジスタと、垂直読み出し/書き込み有効化トランジスタを含む、キャパシタレスフローティングボディ揮発性メモリセル、およびその製造法とプログラミング法

キャパシタレスフローティングボディメモリセル、メモリデバイス、システム、およびキャパシタレスメモリセルを形成するプロセスは、バルク半導体基板(10)の実質的に物理的に分離された部分の活性領域内にメモリセル(82)を形成することを含む。パストランジスタ(70)がワード線(88)と結合するために活性領域上に形成される。キャパシタレスメモリセルはさらに、活性領域の少なくとも一つの垂直側面に沿って垂直に構成される読み出し/書き込み有効化トランジスタ(76)を含み、これは浮遊ソース/ドレイン領域(80)をパストランジスタと共有し、論理状態の読み出し中に動作可能である。論理状態は活性領域のフローティングボディ領域内に電荷として蓄積され、パストランジスタのための異なる決定可能な閾値電圧を生じる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】自己整合的に形成され、幅の減少を抑制可能なコンタクトプラグを有する半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11にソース及びドレインとなる拡散層21がそれぞれ形成されたトランジスタ20と、下部電極32、強誘電体膜33、及び、上部電極34を順に有し、下部電極32が一方の拡散層21に接続され、上部電極34が配線部55に接続された強誘電体キャパシタ30と、強誘電体キャパシタ30の上面から下面に連なる側面に配設され、下端が下面より上面側に位置されたサイドウォール41と、サイドウォール41に接触して、一端を他方の拡散層21及び他端を配線部55とそれぞれ接続された第3のコンタクトプラグ51とを備えている。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】微細に並べられたコンタクトのリソグラフィーマージンを確保し、更に配線とのあわせずれを解決する。

【解決手段】第一の方向に第一のピッチで交互に繰り返し配置されたストライプ状の素子領域および素子分離領域と、素子領域に接続され、第一の方向に第一のピッチで配置された導電材料からなるコンタクトプラグおよびコンタクトプラグに接続された配線とを備え、コンタクトプラグを第一の方向と直交する平面で切断した断面における幅が、配線に接続される場所での幅で定義されるコンタクト上端幅よりも、素子領域に接続される場所で定義されるコンタクト下端幅が大きく、かつ、コンタクト下端幅が、素子領域の幅よりも大きいことを特徴とする不揮発性半導体記憶装置の製造方法。ゲート間を導電材料で埋め込んだ後に、コンタクトを形成する際に、エッチング時のパターンをライン状にしてコンタクトの導電材料で同時に配線層を形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体ウエハ構造

【課題】コンタクト不良を防止して半導体装置の歩留まりを向上させることが可能な半導体装置の製造方法、半導体装置、及び半導体ウエハ構造を提供すること。

【解決手段】シリコン基板10の上方に第1絶縁膜25を形成する工程と、第1絶縁膜25のうち、膜厚が基準値ΔT1よりも厚い肉厚部25xを選択的に薄くする工程と、薄くされた部分の第1絶縁膜25にコンタクトホール38c、38dを形成する工程と、コンタクトホール38c、38d内に導電性プラグ40c、40dを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】ビットラインコンタクトとゲートパターンの上部との電気的短絡を防止することができる不揮発性メモリ装置及びその製造方法を提供する。

【解決手段】半導体基板上に素子分離膜を形成するステップと、半導体基板上に、浮遊ゲート電極と、浮遊ゲート電極と素子分離膜上に延長された制御ゲートラインとを含む不揮発性メモリセルトランジスタのゲートパターンを形成するステップと、マスクパターンを用いて少なくともゲートパターンの第1側壁の第1部分を覆い、制御ゲートラインの上部角部を露出させるステップと、マスクパターンをエッチングマスクとして用い、素子分離膜を第1エッチング率で選択的にエッチングして素子分離膜内に少なくとも部分的な開口部を規定し、同時に制御ゲートラインの上部角部を第1エッチング速度よりエッチング速度が低い第2エッチング率でエッチバックするステップとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化と高速化を図れる半導体装置及びその製造方法を提供することを目的としている。

【解決手段】半導体装置は、半導体基板11上に第1の絶縁膜12、電荷蓄積層13、第2の絶縁膜14及びコントロールゲート15が積層された積層ゲート構造をそれぞれ有し、隣接して配置された第1,第2のゲート電極MC,MCと、前記第1,第2のゲート電極間に形成され、最上面が前記コントロールゲートの最上面よりも高い酸化膜18と、前記コントロールゲート上、前記酸化膜の上面及び前記酸化膜の側壁に延設された窒化膜21とを具備する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されたSRAMのロードトランジスタを構成するMOSトランジスタにおいて、ビアコンタクトがずれてもソース抵抗の増大を回避できる構成を提供する。

【解決手段】二組のCMOSインバータと、一対のトランスファトランジスタと、ポリシリコン抵抗素子よりなり、前記CMOSインバータの各々の第1と第3のMOSトランジスタは素子分離領域211により画成された第1導電型の素子領域21A1に形成され、ポリシリコンゲート電極G1の第1の側に一端が前記ゲート電極G1直下に侵入する第2導電型ソース領域21aと、第2の側に第2導電型ドレインエクステンション領域21bと、それよりも深い第2導電型ドレイン領域よりなり、前記ソース領域21aは前記エクステンション領域21bよりも深く、前記ゲート電極G1は前記ポリシリコン抵抗素子Rと同一の膜厚で、同じ元素により、ドーピングされている。

(もっと読む)

半導体記憶装置の製造方法、及び半導体記憶装置

【課題】信頼性に優れた半導体記憶装置、及びその製造方法を提供する。

【解決手段】凹凸部を有する半導体基板10の凹部に素子分離領域12を形成する工程と、素子分離領域12の、凹凸部を有する半導体基板10の凸部である能動領域18の長手方向と直行する方向にゲート電極配線溝22を設ける工程と、ゲート電極配線溝22を埋めるようにゲート電極材からなる層36を形成する工程と、ゲート電極材からなる層36をパターニングしてゲート電極14を形成する工程と、素子分離領域12をエッチングすることにより能動領域18を形成する工程と、ゲート電極14の側面であり、凹凸部を有する半導体基板10の凸部と接する面の少なくとも一方に電荷蓄積層16を形成する工程と、電荷蓄積層16の少なくとも一部にサイドウォール34を形成する工程と、を含む。

(もっと読む)

半導体集積回路

【課題】動作モードに応じて速度、電力消費をコントロール可能とし、さらにリテンション特性を改善する。

【解決手段】半導体集積回路(1)は、シリコン基板(2)上に混載されたメモリ(4)と論理回路(5)を有する。メモリは、UTB(3)上に形成されたSOI構造を有する部分空乏型のnMOS(6)を含む。部分空乏型のnMOSは、UTBの下に、ゲート端子とは独立に電圧が印加可能にされたバックゲート領域(14)を有する。論理回路は、UTB上に形成されたSOI構造を有する完全空乏型のnMOS(7)とpMOS(8)を含む。完全空乏型のnMOSとpMOSは、UTBの下に、ゲート端子とは独立に電圧が印加可能にされたバックゲート領域(14,22)を有する。

(もっと読む)

不揮発性RAM

【課題】アプリケーションに頻繁にアクセスされるワーク領域と、プログラムコードを記憶させる領域とを、従来に比較して小型なチップサイズにて、1チップで構成することができる不揮発性RAMを提供する。

【解決手段】本発明の不揮発性RAMは、ランダムにデータの読み書きを行う不揮発性メモリであり、電源を切っても記憶内容が失われない不揮発性モード、及び電源を切ると記憶内容が失われる揮発性モードのデータ保持状態に、データ保持の状態を制御可能なメモリ素子からなるメモリ領域と、該メモリ領域において、不揮発性モード書込及び揮発性モード書込各々の対象となるアドレス範囲の領域が設定されるアドレス設定レジスタと、該アドレス設定レジスタを参照して、それぞれのアドレス範囲に対応したデータの書き込みを行うメモリ制御回路とを有する。

(もっと読む)

不揮発性半導体メモリ

【課題】高耐圧系MISトランジスタの特性を改善でき、且つ、高耐圧系MISトランジスタを含む回路の面積を縮小できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、表面に第1のエピタキシャル層22を有する単結晶半導体基板21と、単結晶半導体基板21上に配置される複数のメモリセルMC及び高耐圧系トランジスタHVTrとを具備し、単結晶半導体基板21の不純物濃度は、第1のエピタキシャル層22の不純物濃度よりも低いことを備える。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】チャンネル長を効果的に延ばしつつも高集積化の可能な不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】不揮発性メモリ素子において、半導体基板105は、素子分離膜110により限定された活性領域112を備える。活性領域112は、少なくとも一つの突出部115を備える。1対の制御ゲート電極155aは、少なくとも一つの突出部115の両側面を覆って互いに離隔される。そして、1対の電荷保存層135aは、少なくとも一つの突出部115の両側面及び制御ゲート電極155aの間に介在される。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタを覆う絶縁膜内に形成されて、その強誘電体キャパシタの電極に接続される導電性プラグをコンタクトホール内に埋め込む際に、工程増を抑制しながら、コンタクトホールの下への水素の浸入を防止する構造を備えた半導体装置を提供する。

【解決手段】絶縁膜20内であってキャパシタ上部電極18の上に形成されたコンタクトホール20e内に埋め込まれる導電性プラグ21eとして、アルミニウム膜32を有する複数層31〜34の構造を採用し、これにより、タングステン膜34をコンタクトホール20e内に充填する際に、水素がコンタクトホール20eの下の強誘電体キャパシタ17aに侵入することをアルミニウム膜32によって防止する。

(もっと読む)

半導体素子の素子分離膜形成方法

【課題】サイクリングしきい電圧シフトを改善し、且つトレンチの上部領域に形成されたオーバーハングを防止することが可能な、半導体素子の素子分離膜形成方法の提供。

【解決手段】半導体基板のアクティブ領域上にトンネル絶縁膜、および下部より上部幅が狭い導電膜を形成する段階と、前記導電膜間の前記半導体基板にトレンチを形成する段階と、前記トレンチの一部が充填されるように絶縁膜を形成する段階と、前記導電膜の上部コーナーに形成された前記絶縁膜のオーバーハングが除去されるようにエッチング工程を行う段階とを含み、前記導電膜間の空間と前記トレンチが前記絶縁膜で充填されるまで、前記絶縁膜形成段階、および前記エッチング工程段階を繰り返し行う、半導体素子の素子分離膜形成方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】強誘電体キャパシタを埋める層間絶縁膜上に配線層を形成する際に、層間絶縁膜上のAl2O3膜等の水素バリアを超えて生じる水素の侵入を抑制する半導体装置を提供する。

【解決手段】基板11上に第1の層間絶縁膜20を、テトラエトキシシランを原料とするプラズマCVD法により強誘電体キャパシタ18A,18B,18C,18Dを覆うように形成し、その上に水素バリア膜21を形成し、その上に配線パターン22A、22B、22Cを形成し、第2の層間絶縁膜22HDを高密度プラズマCVD法により堆積し、その上にシリコン酸化膜よりなる犠牲膜22PTをテトラエトキシシランを原料としたプラズマCVD法により堆積し、犠牲膜22HDを化学機械研磨法により第2の層間絶縁膜22HDが露出するまで研磨し、その際、犠牲膜22PTの第2の水分量が第2の層間絶縁膜22HDの第1の水分量よりも少ないようにする。

(もっと読む)

フラッシュメモリ素子及びその製造方法

【課題】高額な露光装備を要せずとも、既存の露光設備を利用することによって誘電体膜コンタクトホールを微細化して形成することができるフラッシュメモリ素子とその製造方法を提供する。

【解決手段】半導体基板100上に第1導電膜104のパターンと素子分離膜106を形成し、誘電体膜108を形成する。誘電体膜108上には第1開口部を有するフォトレジストパターン110を形成し、第1開口部よりもサイズが小さい第2開口部となるように、フォトレジストパターン110を溶解し、開口部110a方向にフォトレジストの一部が流れるようにする原理を活用することで、開口部110aのサイズを小さくするようにする。フォトレジストパターン110に沿って誘電体膜108をパターニングして誘電体膜コンタクトホールを形成し、フォトレジストパターンを除去する。誘電体膜108と第1導電膜104上に第2導電膜を形成する。

(もっと読む)

2,001 - 2,020 / 3,470

[ Back to top ]