Fターム[5F083PR03]の内容

Fターム[5F083PR03]に分類される特許

1 - 20 / 1,171

半導体装置及びその製造方法

半導体装置の製造方法

半導体装置の製造方法

半導体装置の製造方法

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

分子メモリ装置の製造方法

【課題】メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に第2方向に延びる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって前記第2配線間に複数本の第2絶縁部材を前記配線層に接するように形成する工程と、前記犠牲膜を除去することによりギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し他方には結合しない分子材料を形成する工程と、を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の領域に容易に第1の膜を形成して半導体装置の不良を低減する。また、スループットが向上して、製造コストの低減を図る。

【解決手段】半導体装置の製造方法では、半導体基板の第1及び第2の領域上に第1の膜を形成した後、第1の膜上にフォトレジストパターンを形成する。フォトレジストパターンをマスクに用いた第1の膜のエッチングにより、第2の領域上の第1の膜を除去すると共に第2の領域上を覆うように被覆膜を形成する。半導体基板に熱処理を行うことにより、被覆膜を除去すると共にフォトレジストパターンに焼き締め処理を行う。この後、フォトレジストパターンを除去する。

(もっと読む)

半導体装置の製造方法

【課題】微細化に対応した半導体装置を提供する。

【解決手段】半導体基板の第1の領域内に第1の方向に沿って交互に配置されるように第1及び第2の素子分離領域を形成する。この際、第1及び第2の素子分離領域のうち少なくとも一方の素子分離領域の側面は半導体基板の主面に対して垂直とならないように第1及び第2の素子分離領域を形成する。この後、第1及び第2の素子分離領域の上部を除去して、第1の素子分離領域と第2の素子分離領域の間の半導体基板をフィンとして形成する。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】ソース電極層及びドレイン電極層上を覆うように酸化物半導体層を成膜した後、ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を研磨により除去する。ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

機能性デバイスの製造方法及び機能性デバイスの製造装置

【課題】機能性デバイスの高性能化、又はそのような機能性デバイスの製造プロセスの簡素化と省エネルギー化を提供する。

【解決手段】機能性デバイスの製造方法は、型押し工程と、機能性固体材料層形成工程を含む。型押し工程では、機能性固体材料前駆体溶液を出発材とする機能性固体材料前駆体層に対して型押し構造を形成する型を押圧している間の少なくとも一部の時間においてその機能性固体材料前駆体層に対して熱を供給する熱源の第1温度がその機能性固体材料前駆体層の第2温度よりも高くなるように、その機能性固体材料前駆体層に対して型押し加工を施す。また、機能性固体材料層形成工程では、型押し工程の後、酸素含有雰囲気中において、機能性固体材料前駆体層を前述の第1温度よりも高い第3温度で熱処理することにより、機能性固体材料前駆体層から機能性固体材料層を形成する。

(もっと読む)

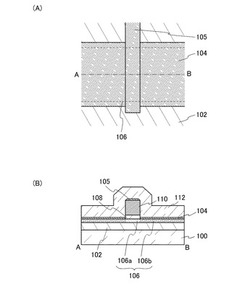

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】本発明は、第1の不純物拡散領域と第2の不純物拡散領域との間に位置するピラーを流れるドレイン電流が、隣接するピラーにリーク電流として流れることを防止可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13に立設されたピラー28と、Y方向に延在するように半導体基板13に設けられ、Y方向と交差するX方向において対向するピラー28の第2の側壁を露出する第1の溝16と、ピラー28の第2の側壁の下部に設けられた第1の不純物拡散領域と、ピラー28の上端に設けられた第2の不純物拡散領域と、半導体基板13に内設され、第1の溝16の底16Aに配置された絶縁層14と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホールの側壁に制御性良く傾斜を形成することで、コンタクトプラグにボイドが形成されることを抑制する。

【解決手段】絶縁膜10に第1のコンタクトホール(破線部)を形成する工程と、第1のコンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施して内壁が傾斜した第2のコンタクトホール13を形成する工程と、第2のコンタクトホール内にコンタクトプラグを形成する工程とを有する。

(もっと読む)

1 - 20 / 1,171

[ Back to top ]