Fターム[5F083ZA04]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090)

Fターム[5F083ZA04]の下位に属するFターム

ゲート構造が異なるもの (317)

ソース/ドレイン構造が異なるもの (250)

ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA04]に分類される特許

1 - 20 / 120

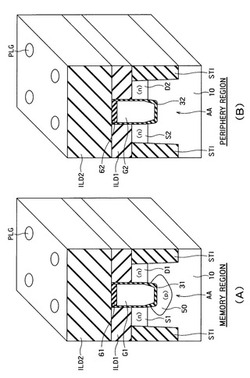

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、Fin型FETおよび従来型トランジスタを混載した半導体記憶装置を提供することである。

【解決手段】半導体記憶装置は第1の領域および第2の領域を備える。メモリ部のトランジスタは第1導電型のFin型半導体層を備える。第1導電型の第1のソース層および第1のドレイン層はFin型半導体層の両端に設けられる。第1のゲート電極はFin型半導体層の両側面に設けられる。第2導電型のパンチスルーストッパ層は第1のゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は第1のソース層および第1のドレイン層の下の不純物濃度よりも高い。周辺回路部のトランジスタは、第2のゲートトレンチを備える。第1導電型の第2のソース層および第1導電型の第2のドレイン層は、第2のゲートトレンチの両側に設けられる。第2のゲート電極は、第2のゲートトレンチ内に充填される。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

(もっと読む)

半導体装置

【課題】素子分離すべき領域にダミーの補助ゲートを配置することで、電気的に分離する方法(FS方式)を採用しつつ、補助ゲートに給電するための新たな専用の配線を設けることによるチップの縮小化の弊害を解消する半導体装置を提供する。

【解決手段】半導体基板2に埋め込み形成された素子分離膜によって、複数のセル部活性領域が区画された半導体装置1であって、半導体基板2に設けられたゲート溝内に、ゲート絶縁膜を介して形成された補助セルゲート28aが、半導体基板2と電気的に接続されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】低いビットコストで積層化可能な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、平行に配列された所定方向に延びる複数の半導体層と、半導体層の上に形成されたゲート絶縁層と、ゲート絶縁層の上に形成され所定方向に配列された複数の浮遊ゲートと、浮遊ゲートに隣接するゲート間絶縁層と、ゲート間絶縁層を介して所定方向の両側から浮遊ゲートに対向し複数の半導体層と交差する方向に延びる複数の制御ゲートとを有するセルアレイ層を複数層積層した不揮発性半導体記憶装置であって、積層方向に隣接するセルアレイ層において、下層のセルアレイ層の制御ゲートと、その上層のセルアレイ層の制御ゲートとが直交し、下層のセルアレイ層の浮遊ゲートと、その上層の半導体層との位置が整合している。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】小型化が可能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、基板と、メモリ部と、非メモリ部と、を備える。メモリ部は、基板上に設けられる。非メモリ部は、基板上に設けられ基板の主面に対して平行な面内でメモリ部と並ぶ。メモリ部は、積層体と、半導体層と、メモリ膜と、導電膜と、を含む。積層体は、主面に対して垂直な第1軸に沿って積層された複数の電極膜と、第1軸に沿って隣り合う2つの電極膜の間に設けられた電極間絶縁膜と、を含む。半導体層は、複数の電極膜の側面に対向する。メモリ膜は、複数の電極膜と半導体層との間に設けられる。導電膜は、積層体の上に設けられ、積層体と離間している。非メモリ部は、導電膜と同層の抵抗素子部を含む。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

情報格納装置

【課題】より容易な方法で集積度を向上させた情報格納装置を提供する。

【解決手段】本発明の情報格納装置は、基板と、基板上のゲートライン構造体を含むトランジスターと、少なくとも一部が基板内に埋め込まれてトランジスターの活性領域を定義する導電性分離パターン(conductive isolation patterns)と、を有し、導電性分離パターンは、互いに電気的に連結される。

(もっと読む)

半導体メモリ装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線の一端にバックゲートを有するトランジスタ(バックゲートトランジスタ)を直列に挿入し、そのバックゲートの電位は常に十分な負の値となるようにする。また、ビット線の最低電位はワード線の最低電位よりも高くなるようにする。電源が切れた際には、ビット線はバックゲートトランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

1 - 20 / 120

[ Back to top ]