Fターム[5F083ZA05]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090) | ゲート構造が異なるもの (317)

Fターム[5F083ZA05]に分類される特許

1 - 20 / 317

半導体装置の製造方法及び半導体装置

半導体装置及びその製造方法

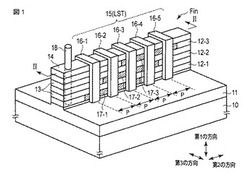

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】互いに異なる特性を備える複数の電界効果トランジスタを同一基板上に有する半導体装置の製造歩留まりを向上させる。

【解決手段】異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとを組み合わせることにより、互いにサイドウォール長の異なる3種類のサイドウォールSWL,SWM,SWHを形成する。異方性のドライエッチングの回数を減らすことにより、配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の削れを防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1のメモリセル領域に形成された選択ゲート電極CGの上部に酸化シリコン膜24および窒化シリコン膜25を形成した後、メモリマットのゲート長方向の最も外側(ダミーセル領域)に位置する選択ゲート電極CGの上部の酸化シリコン膜24および窒化シリコン膜25を除去することにより、メモリマットの端部を覆う下層レジスト膜12の段差をなだらかにし、下層レジスト膜12の上に形成されるレジスト中間層13の厚さの均一性を向上させ、局所的な薄膜化または消失を防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイおよび周辺回路の両方において、ワード線またはゲート電極を適切にシリサイド化することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む複数のメモリセル、および、互いに電気的に接続されたフローティングゲートおよびコントロールゲートを含むゲート電極と、ゲート電極のうちフローティングゲートの側面を被覆する側壁膜と、ゲート電極のうちコントロールゲートの側面を被覆し側壁膜上に設けられたスペーサとを備えたトランジスタを含む周辺回路、を備え、メモリセルおよび周辺回路において、コントロールゲートの上部はシリサイド化されている。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

半導体装置の製造方法

【課題】周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に、第2絶縁膜26から離間する第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】論理素子のnチャネルMOSトランジスタに十分な膜厚の引張応力膜を形成し、メモリ素子がゲート電極間の層間絶縁膜の埋込不良を生じない製造方法の提供。

【解決手段】論理素子は、第1及び第2のnチャネルMOSトランジスタを含み、第1のゲート高さGH1及び第1のゲート長を有するゲート電極を有し、ゲート電極は第1の間隔Dを有し、メモリ素子は、第3および第4のnチャネルMOSトランジスタを含み、ゲート高さGH2および第2のゲート長を有するゲート電極を含み、論理素子及びメモリ素子は第1の引張応力膜64で覆われ、論理素子は、さらに第2の引張応力膜65で覆われ、論理素子及びメモリ素子のゲート間に形成された引張応力膜の最小距離は各々第1の距離LL及び第1の距離LMで隔てられ、第1のアスペクト比(GH1/LL)と、第2のアスペクト比(GH2/LM)とは略等しい。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル特性の向上、およびトランジスタ特性の劣化の抑制を図る。

【解決手段】半導体層10上に、第1絶縁膜11を形成する。第1領域における第1絶縁膜上に、表面に酸化膜15が形成された第1導電膜18を形成する。第1領域における第1導電膜上および第2領域における第1絶縁膜上に、第2導電膜19を形成する。第2導電膜上に、第2絶縁膜21を形成する。第2絶縁膜上に、第3導電膜25を形成する。第1領域における第3導電膜および第2絶縁膜の一部を貫通させて第2導電膜を露出させる。第2導電膜および第3導電膜の表面に形成された第1自然酸化膜23を除去する。第3導電膜上および第1領域における第2導電膜上に、第4導電膜27を形成する。第4導電膜上に金属層30a,30bを形成して、第4導電膜、第3導電膜、および第1領域における第2導電膜をシリサイド化する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

OTPメモリ

【課題】より秘匿性の高いOTPメモリを提供する。

【解決手段】メモリセルは、第1ノードと第2ノードとの間に電流経路を形成するメモリトランジスタと、第3ノードと第4ノードとの間に電流経路を形成し、第3ノードがメモリトランジスタのゲートと配線により接続された選択トランジスタと、第1ノードに接続されたキャパシタとを備える。メモリトランジスタに対して、ゲート酸化膜が破壊されず劣化してゲートリーク電流が増大する程度の高電圧を印加することによりデータが書き込まれる。キャパシタの蓄積電荷のリークの有無によりデータを読み出すことが可能となる。ゲート酸化膜の劣化箇所は物理解析で識別できないため、秘匿性が高い。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコン膜との接触に起因するショットキー抵抗を低減する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタは、第1の活性領域の表面の一部を覆い二酸化シリコンよりも高い誘電率を有する第1の絶縁材料からなる第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第1の金属材料からなる第1の金属ゲート電極と、第1の金属ゲート電極上に形成されたp型導電型の第1の多結晶シリコン膜を有する。

(もっと読む)

半導体素子及びその製造方法

【課題】フラッシュメモリ素子の安全性及び信頼性を改善することができる半導体素子及びその製造方法を提供する。

【解決手段】第1方向に沿って延長された活性領域を含む半導体基板と、半導体基板の上部に第1方向に交差する第2方向に沿って形成されたセレクトラインと、セレクトラインの間の前記活性領域それぞれに形成されて第1不純物を含む接合領域と、セレクトラインの間の空間を埋め込む多層の酸化膜と、接合領域の下部に繋がれて半導体基板の活性領域に形成されて第2不純物を含む接合領域延長部と、多層の酸化膜のうち少なくともいずれか一層を貫通して接合領域及び接合領域延長部に接触されたコンタクトプラグと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ上の絶縁膜とキャパシタの形成されていない領域上の絶縁膜と平坦化する際に、キャパシタ上の絶縁膜を一部エッチング除去した後平坦化すると、両者の境界部に残る絶縁膜隆起部が剥がれてくぼみ等の欠陥が発生する。

【解決手段】境界部に残す絶縁膜の隆起部立ち上がり点から水平方向の距離をLr、エッチング量をHdとしたとき、アスペクト比Hd/Lrを0.6以下、好ましくは0.25以下とする。通常、Hdはキャパシタの形成されていない領域上の絶縁膜表面高さまでとし、Lrはキャパシタ高さの少なくとも4倍とする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

1 - 20 / 317

[ Back to top ]