Fターム[5F083ZA07]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090) | ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA07]に分類される特許

201 - 220 / 403

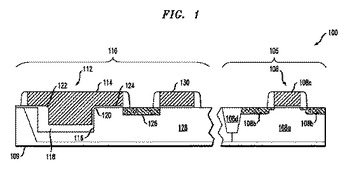

半導体記憶装置およびその製造方法

【課題】デバイス間バラツキや誤動作が起こりにくく信頼性の高い、かつ消費電力が抑えられた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、絶縁体上に形成された第1導電型の半導体層100と、半導体層100上に形成された電荷蓄積機能を有する電荷蓄積膜103及び電荷蓄積膜103上に形成されたゲート電極105aと、ゲート電極105aの下方の半導体層100に形成されたチャネル領域108と、チャネル領域108の両側に、半導体層100内に形成された第2導電型の拡散領域106,107と、半導体層100を延長して形成した第1導電型のボディコンタクト領域109と、延長した半導体層100上にゲート電極105aを延長し、ボディコンタクト領域109と、チャネル領域108の両側の拡散領域106,107を分離するゲート電極引き出し部105bとを備える。

(もっと読む)

電気光学装置、電子機器、電気光学装置の製造方法

【課題】不揮発性メモリと画素TFTが同一基板上に併設されており、かつ高信頼性とされた液晶装置を提供する。

【解決手段】本発明の電気光学装置は、画素部と、これを駆動させる駆動回路と、不揮発性メモリと、を備えた電気光学装置である。画素部及び前記駆動回路の少なくとも一方におけるスイッチング素子は、不揮発性メモリとともに基板10A上に形成されている。スイッチング素子のゲート絶縁膜は、第1絶縁膜35と第2絶縁膜36と第3絶縁膜38との積層構造からなっており、不揮発性メモリは、第2絶縁膜36を介して半導体層33上に設けられたフローティングゲート電極37と、第3絶縁膜38を介してフローティングゲート電極37上に設けられたコントロールゲート電極39Aと、を有するメモリセル110aを備えている。

(もっと読む)

集積回路の製造方法

【課題】異なる基材領域又はいくつかのトレンチの底部及び各側壁部を覆う異なる酸化被膜の形成に異なる酸化処理を備える、集積回路を製造する方法を提供する。

【解決手段】表面を有する半導体基板10を準備するステップと、少なくとも一つの注入種が、前記表面の第二の部分区域14と比較すると前記表面の第一の部分区域12に近接して特に注入されるようなイオン注入処理を実行するステップと、前記表面の前記第一の部分区域を覆う第一の膜厚を有する第一の酸化被膜32と前記表面の前記第二の部分区域を覆う第二の膜厚を有する第二の酸化被膜36とを形成するように、単一の酸化処理を実行するステップであって、前記第一の膜厚が前記第二の膜厚と異なるステップと、を備える。

(もっと読む)

垂直型半導体素子及びその製造方法

【課題】垂直型半導体素子及びその製造方法を提供する。

【解決手段】半導体素子及びその製造方法において、半導体素子は単結晶半導体物質からなり、水平方向に延長される基板100と前記基板上に複数の層間絶縁膜105a〜105eを含む。複数のゲートパターン132〜132dは隣接する下部層間絶縁膜と隣接する上部層間絶縁膜の間に各々提供される。単結晶半導体物質の垂直チャンネル116は前記複数の層間絶縁膜とゲートパターンを貫通して垂直方向に延長される。そして、前記各々のゲートパターンと垂直チャンネルの間には前記垂直チャンネルから前記ゲートパターンを絶縁させるゲート絶縁膜が具備される。

(もっと読む)

DRAM素子

【課題】DRAM周辺回路の低電圧P+ゲートMOSトランジスタ素子の性能と、高電圧N+ゲートMOSトランジスタ素子のゲート酸化膜の信頼性とを兼ね備えたNMOSトランジスタ素子を提供する。

【解決手段】DRAM素子は、第一リセスゲートが設けられたメモリアレイ領域、及び第二リセスゲートが設けられた周辺回路領域を有しており、前記第一リセスゲート及び第二リセスゲートがはめ込まれている半導体基板と、前記第一リセスゲートと前記半導体基板との間に設けられた、均一な厚さの第一ゲート酸化膜と、前記第二リセスゲートと前記半導体基板との間に設けられた、不均一な厚さの第二ゲート酸化膜とを含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAM等の半導体集積回路装置の微細化を図り、また、高性能化を図る。

【解決手段】周辺回路領域に横型のnチャネル型MISFETを形成した後、その上部に酸化シリコン膜23を形成し、さらにその上部であって、メモリセル領域MAに、縦型の情報転送用MISFETQsであって、下層からn型多結晶シリコン膜41、ノンドープの多結晶シリコン膜43およびn型多結晶シリコン膜47よりなる半導体柱を有し、ノンドープの多結晶シリコン膜43の上下には、窒化シリコン膜42、46が形成され、半導体柱の側壁に形成された酸化シリコン膜53をゲート絶縁膜とし、また、n型多結晶シリコン膜55、57をゲート電極とする情報転送用MISFETQsを形成し、さらに、n型多結晶シリコン膜47の上部に、情報蓄積用容量素子Cを形成する。

(もっと読む)

NAND型不揮発性半導体記憶装置の製造方法及びNAND型不揮発性半導体記憶装置

【課題】NAND型不揮発性半導体記憶装置のリーク不良を低減し且つ未開口部分を低減する。

【解決手段】半導体基板上にゲート絶縁膜102、第1の電極103、第2の電極107及び第1のストッパ絶縁膜108を形成し且つ前記半導体基板101の表面に拡散層領域106を形成する工程と、前記拡散層領域106上の前記第1のストッパ絶縁膜108、前記第2の電極107及び前記第1の電極103をエッチングして開口部111及びコンタクト用ゲート110を形成する工程と、メモリセルゲート形成領域にインターポリ絶縁膜119及びコントロールゲート120を形成する工程と、前記コンタクト用ゲートを繋ぐようなソース線121及び個々の選択ゲートを繋ぐ配線層122を形成する工程と、を具備したことを特徴とするNAND型不揮発性半導体記憶装置の製造方法。

(もっと読む)

半導体デバイス、半導体デバイスを形成する方法、および集積回路

【課題】 相互に異なるしきい値電圧要件を有する複数のトランジスタを結合するための技法を提供する。

【解決手段】 一態様では、半導体デバイスは、第1および第2のnFET領域と第1および第2のpFET領域とを有する基板と、第1のnFET領域の上の基板上のロジックnFETと、第1のpFET領域の上の基板上のロジックpFETと、第2のnFET領域の上の基板上のSRAM nFETと、第2のpFET領域の上の基板上のSRAM pFETとを含み、そのそれぞれが、高K層の上の金属層を有するゲート・スタックを含む。ロジックnFETゲート・スタックは、高K層から金属層を分離するキャッピング層をさらに含み、キャッピング層は、ロジックpFET、SRAM nFET、およびSRAM pFETのうちの1つまたは複数のしきい値電圧に対してロジックnFETのしきい値電圧をシフトするようにさらに構成される。

(もっと読む)

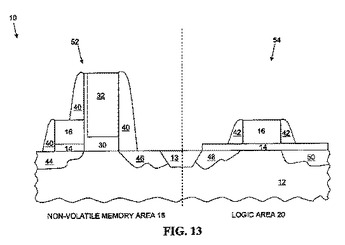

NVM回路をロジック回路と集積する方法

不揮発性メモリ(NVM)回路18を論理回路20とともに集積する方法が提供される。この方法は、基板12のNVM領域及びロジック領域の上に第1のゲート材料層16を堆積することを含む。この方法は更に、窒化膜、酸化膜及び窒化膜(ARC層)を有する複数の接し合う犠牲層22、24、26を互いに重ねて堆積することを含む。これら複数の接し合う犠牲層22、24、26は、NVM領域内のメモリトランジスタの選択ゲート16及び制御ゲート32をパターニングするために使用され、複数の接し合う犠牲層22、24、26のうちのARC層22はまた、ロジック領域20内のロジックトランジスタのゲート16をパターニングするために使用される。  (もっと読む)

(もっと読む)

ランダム・アクセス・メモリ・デバイスのトレンチ・キャパシタ漏洩電流を低減する方法

本発明は、一態様では、半導体デバイスを製造する方法を提供する。この方法は、半導体基板(109)のダイナミック・ランダム・メモリ領域(DRAM)(110)内にトレンチ分離構造(118)を形成すること、ならびにトレンチ分離構造(118)の上に、トレンチ分離構造(118)の一部分を露出するようにエッチング・マスクをパターニングすることを含む。露出したトレンチ分離構造(118)の一部分を除去してその中に、半導体基板によって形成された第1の角部と、トレンチ分離構造によって形成された第2の角部とを含むゲート・トレンチ(116)を形成する。エッチング・マスクをDRAM領域(110)から除去し、ゲート・トレンチの少なくとも第1の角部に丸みをつけて、丸みをつけた角部(120)を形成する。この後に、ゲート・トレンチ(116)の側壁の上、第1の丸みをつけた角部(120)の上、およびゲート・トレンチ(116)に隣接する半導体基板(109)の上の酸化物層(124)の形成を続ける。トレンチ(116)をゲート材料で充填する。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】設計、製造および検査の各工程において作業効率を向上し得る不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性メモリでは、第1配線層LY2に形成されるビット線BL1によりコンタクトホールCH1,CH3,CH5を介してセルトランジスタ21〜25の各ドレインD21〜D25を共通に接続し、このビット線BL1にバイアホールVH1,VH3,VH5を介して接続可能に配置したビット線BL2を第2配線層LY4に形成する。また、第1配線層LY2に形成されるソース線SL1によりコンタクトホールCH2,CH4,CH6を介してセルトランジスタ21〜25の各ソースS21〜S25を共通に接続し、このソース線SL1にバイアホールVH2,VH4,VH6を介して接続可能に配置したソース線SL2を第2配線層LY4に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】性能を損なうことなく、さらに余分な製造工程を追加することなく、容量素子の面積を縮小した半導体装置の技術を提供する。

【解決手段】第1容量絶縁膜を介して設けられた半導体基板の活性領域と、選択用nMISの選択ゲート電極と同一層の導体膜からなる下部電極CGcbとの間で第1容量部を構成し、電荷蓄積層を含む多層構造の絶縁膜と同一層の第2容量絶縁膜を介して設けられた下部電極CGcbと、メモリ用nMISのゲート電極と同一層の導体膜からなる上部電極MGctとの間で第2容量部を構成し、第1容量部と第2容量部とから積層型容量素子C1を構成し、下部電極CGcbの平面形状を、第1の間隔S1を設けて第1の幅W1の線状の導体膜が第1の方向に沿って複数本形成され、第2の間隔S2を設けて第2の幅W2の線状の導体膜が第1の方向と交差する第2の方向に沿って複数本形成された格子形状とする。

(もっと読む)

半導体装置

【課題】不揮発性メモリを備えた半導体装置のチップ面積を縮小する。

【解決手段】基板1Sの主面に形成され、隣り合って配置されたメモリセルMC1およびメモリセルMC2を含む。基板1Sの主面には、互いに電気的に分離された活性領域L1〜L4を配置する。活性領域L1にはメモリセルMC1の容量素子Cを配置し、活性領域L4にはメモリセルMC2の容量素子Cを配置する。また、活性領域L2には、メモリセルMC1の書込み/消去用素子CWEおよびメモリセルMC2の書込み/消去用素子CWEを共に配置する。さらに、活性領域L3には、メモリセルMC1の読出し用素子QRおよびメモリセルMC2の読出し用素子QRを共に配置する。

(もっと読む)

厚さが減少した半導体素子、これを採用する電子製品及びその製造方法

【課題】厚さが減少した半導体素子、これを採用する電子製品及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は第1及び第2活性領域を有する半導体基板を準備する工程を含む。前記第1活性領域に第1ゲートパターン及び第1不純物領域を含む第1トランジスタを形成する。前記第2活性領域に第2ゲートパターン及び第2不純物領域を含む第2トランジスタを形成する。前記第1トランジスタ上に第1導電性パターンを形成する。前記第1導電性パターンの少なくとも一部と前記第2ゲートパターンの少なくとも一部は前記半導体基板の上部表面から同一距離に配置される。前記第1導電性パターンは前記第2ゲートパターンを形成する間に形成される。

(もっと読む)

半導体装置およびその作製方法

【課題】不揮発性メモリトランジスタの電荷保持特性を向上させる。

【解決手段】半導体基板と導電膜の間には、第1絶縁膜、電荷トラップ膜、第2絶縁膜が形成されている。電荷トラップ膜は水素濃度が低い上部領域と、水素濃度が高い下部領域を有する窒化シリコン膜でなる。このような窒化シリコン膜は、化学気相成長法により、水素を15atomic%以上含む窒化シリコン膜を形成し、その上部を窒化することで形成される。この窒化処理は、窒素ガスのプラズマ中に生成された窒素ラジカルで窒化シリコン膜を窒化することで行われる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 STI起因の応力が印加されることによる結晶欠陥発生を抑制することができ、微細化及び信頼性の向上をはかる。

【解決手段】 基板101上に、不揮発性メモリセル部,周辺回路領域の低電圧動作回路部,及び周辺回路領域の高電圧動作回路部を有し、各部の素子間がSTIで分離された不揮発性半導体記憶装置であって、高電圧動作回路部のSTI埋め込み絶縁膜の上面は基板表面より上方に位置し、低電圧動作回路部のSTI埋め込み絶縁膜の少なくとも一部の上面は基板表面より下まで後退した形状になっている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】単位面積当たりのキャパシタ容量の向上を可能とする技術、およびそれに伴う製造工程を簡略化できる技術を提供する。

【解決手段】キャパシタ形成領域の表面に、少なくとも1つ以上の凸凹なキャパシタ形成溝4aを形成することでキャパシタの表面積を増加し、単位面積当たりのキャパシタの容量の向上を可能とする。また、前記キャパシタ形成溝4aと半導体基板1の表面に形成された素子分離溝4とを同一の工程で形成することで製造工程を簡略化することができる。また、キャパシタ形成領域におけるキャパシタの誘電体膜16aと、MISFET形成領域における高耐圧用ゲート絶縁膜16とを同一の工程で形成する。または、キャパシタ形成領域におけるキャパシタの誘電体膜16aおよびメモリセル形成領域における多結晶シリコン層10aと多結晶シリコン層17との間のメモリゲート層間膜11を同一の工程で形成する。

(もっと読む)

不揮発性メモリのためのプログラム及び消去方法

【課題】本発明は、絶縁膜を電荷保存層として利用するフラッシュメモリ装置、そのプログラム及び消去方法、それを含むメモリシステム及びコンピュータシステムを提供する。

【解決手段】電荷保存層を有する不揮発性メモリ装置のプログラム又は消去方法であって、少なくとも一つの単位プログラム又は消去ループを行うステップを含み、各単位プログラム又は消去ループは、不揮発性メモリ装置の位置(例えば、ワードライン又は基板)に正又は負の電圧のような少なくとも一つのプログラムパルス、少なくとも一つの消去パルス、少なくとも一つの時間遅延、少なくとも一つのソフト消去パルス、少なくとも一つのソフトプログラムパルス及び/又は少なくとも一つの検証パルスを印加することを特徴とする。

(もっと読む)

半導体メモリ

【課題】メモリセルの微細化と信頼性の向上とを図る。

【解決手段】本発明の例に係る半導体メモリは、アクティブエリアAA1,AA2,・・・と素子分離エリアとが第1方向に交互に配置される周期構造を備え、第1方向の最端部からn(nは奇数)番目のアクティブエリアAAnとn+1番目のアクティブエリアAAn+1とは、第1方向に直交する第2方向の最端部において互いに結合され、閉ループ構造を構成している。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】スプリットゲート型MONOSメモリセルにおいて、SSI方式による書込み時のディスターブ耐性を向上させることのできる技術を提供する。

【解決手段】選択用nMISQncと、選択用nMISQncの側面に絶縁膜6b、6tおよび電荷蓄積層CSLを介して形成されたメモリ用nMISQnmとを含むメモリセルMC1において、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さが、ゲート長方向中央部下のゲート絶縁膜4の厚さよりも厚く形成され、選択ゲート電極CGと電荷蓄積層CSLとの間に位置し、かつ半導体基板1に最も近い下層の絶縁膜6bの厚さが、半導体基板1と電荷蓄積層CSLとの間に位置する下層の絶縁膜6bの厚さの1.5倍以下に形成される。

(もっと読む)

201 - 220 / 403

[ Back to top ]