Fターム[5F083ZA07]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090) | ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA07]に分類される特許

21 - 40 / 403

半導体装置および半導体装置の製造方法

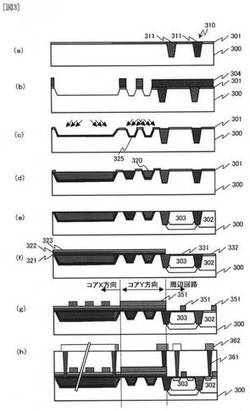

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】クラックや結晶欠陥の発生なしに高電圧トランジスタの素子領域間の耐圧を向上できるようにした不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域の第1素子分離絶縁層が当該メモリセル領域の第1素子分離溝内に第1の酸化膜を埋め込んで構成され、第1の酸化膜の上面が半導体基板の上面と第1ゲート電極の上面との間に存在するように構成されている。

周辺領域の第2素子分離絶縁層は、周辺領域の第2素子分離溝内の全体に埋込まれると共にその上面が半導体基板の上面の上方に突出した第1の酸化膜と、当該第1の酸化膜上に積層され、その上面が第1導電膜の上面より上方に突出している第2の酸化膜とで構成されている。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグと半導体基板の活性領域との間の重ねマージンを十分に確保して、低抵抗且つ接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極19A及びキャップ絶縁膜20Aと、活性領域1Aの上面に設けられたビットコンタクト27A及びビット線27と、半導体基板1上に設けられた絶縁層32,40と、第1容量コンタクトプラグ39Aと、を備え、第1容量コンタクトプラグ39Aは、柱状部39aとこの柱状部39aの下方に設けられた板状部39bとを有し、板状部39bの底面と、素子分離領域及びキャップ絶縁膜20Aによって区画された活性領域1Aの表面1a,1cとが全面で接触するように設けられていることを特徴とする半導体装置を選択する。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み時間の短縮及び読み出し電圧の上昇の抑制を図る不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリ部と、制御部と、を備える。メモリ部は、積層構造体と、半導体ピラーと、記憶層と、内側絶縁膜と、外側絶縁膜と、メモリセルトランジスタと、を有する。制御部は、メモリセルトランジスタの各閾値を正または負の一方に設定する制御、及び各閾値のうち0ボルトから最も離れた第n閾値の分布の幅よりも、第n閾値と同じ符号の第m(mはnよりも小さい1以上の整数)閾値の分布の幅を狭く設定する制御を行う。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】支持基板上に絶縁層を形成し、当該絶縁層上に高純度化された酸化物半導体と、SOI(Silicon On Insulator)基板である単結晶シリコンを用いて半導体装置を構成する。高純度化された酸化物半導体を用いて構成したトランジスタは、リーク電流が極めて小さいため、長期間にわたって情報を保持することが可能である。また、SOI基板を用いることにより、絶縁層上に形成された薄い単結晶シリコンの特長を生かすことで、トランジスタを完全空乏型とすることができるため、高集積、高速駆動、低消費電力など付加価値の高い半導体集積回路が実現できる。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置及びその製造方法

【課題】スタック構造のゲート電極を有する不揮発性メモリの低電圧動作化・低消費電力化を実現しうる半導体装置の製造方法を提供する。

【解決手段】素子分離絶縁膜上に第1の導電膜を形成し、素子領域上に第1の絶縁膜を形成し、第1の絶縁膜上及び第1の導電膜が形成された素子分離絶縁膜上に第2の導電膜を形成し、第2の導電膜及び第1の導電膜をパターニングし、第2の導電膜により形成された第1の部分が素子領域上に位置し、第1の導電膜と第2の導電膜の積層膜により形成された第2の部分が素子分離絶縁膜上に位置するフローティングゲートを形成し、フローティングゲート上に第2の絶縁膜を形成し、第2の絶縁膜上にコントロールゲートを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置およびその製造方法

【課題】下部電極、上部電極およびそれらの間の絶縁膜により構成される容量素子の下部電極および上部電極間の耐圧を向上させる。

【解決手段】上部電極TEならびに上部電極TEのそれぞれの側壁の側壁酸化膜9およびサイドウォール10と下部電極BEとの間にONO膜IFを連続的に形成し、また、上部電極TEの側壁に、側壁酸化膜9を介して真性半導体膜からなるサイドウォール10を形成することにより、下部電極BEおよび上部電極TE間にリーク電流が発生することを防ぐ。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

21 - 40 / 403

[ Back to top ]