Fターム[5F083ZA07]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090) | ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA07]に分類される特許

41 - 60 / 403

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の歩留まりを向上させること。

【解決手段】シリコン基板20に溝20aを形成する工程と、溝20aに充填材30を充填する工程と、溝20aに充填材30が充填された状態で、シリコン基板20に対してウエット処理を行う工程と、ウエット処理の後、充填材30を除去する工程と、充填材30を除去した後、溝20a内に、キャパシタ誘電体膜45aを介してキャパシタの対向電極50pを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】素子特性の安定性を向上できる半導体集積回路装置の製造方法を提供する。

【解決手段】半導体集積回路装置の製造方法は、シリコン基板101の表面に第1の酸化膜103を形成する工程と、周辺回路領域A2内にあるシリコン基板101の所定箇所に不純物を注入し、この所定箇所上の第1の酸化膜103を除去し、この所定箇所上に第2の酸化膜112を形成する工程と、メモリセル領域A1内の第1の酸化膜103にトンネルウィンドウを形成し、このトンネルウィンドウ内で露出したシリコン基板101上にトンネル酸化膜116を形成し、トンネル酸化膜116を覆うメモリセル用ポリシリコン膜118を形成する工程と、第2の酸化膜112を形成する前記工程の後にメモリセル用ポリシリコン膜118上にONO膜119を形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜9a,9bと酸化シリコン膜9a,9bに挟まれた窒化シリコン膜10aとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6aからなり、窒化シリコン膜10aを有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた窒化シリコン膜6bとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた空洞CAVとを有し、窒化シリコン膜6bを有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成されたFETのソース側のエクステンション領域の抵抗値を低減し、半導体装置の動作速度を向上することができる技術を提供する。

【解決手段】ゲート電極4dの側壁に、ゲート電極4dのゲート長方向の幅が異なる第1サイドウォール6wおよび第2サイドウォール6nをそれぞれ形成する。これにより、第1サイドウォール6wおよび第2サイドウォール6nの形状によって第1サイドウォール6wおよび第2サイドウォール6nの下部に自己整合的に形成されるエクステンション領域37、38の半導体基板SBの上面の幅をそれぞれ異なる長さで形成する。

(もっと読む)

不揮発性プログラマブルロジックスイッチおよび半導体集積回路

【課題】回路サイズを減少させることを可能にする。

【解決手段】素子分離領域102によって分離された、隣接する第1導電型の第1半導体領域101aおよび第2導電型の第2半導体領域101cと、第1半導体領域101a上に設けられた不揮発性メモリセルトランジスタ10と、第2半導体領域101c上に設けられ、第1半導体領域101aに設けられた第1ドレイン領域10bと電気的に接続されたゲート電極20C2とを有するパストランジスタ20と、第1半導体領域101aに設けられ第1半導体領域に基板バイアスを印加する第1電極8と、第2半導体領域101cに設けられ第2半導体領域に基板バイアスを印加する第2電極9と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく、高耐圧トランジスタへのイオン注入を的確に実行することを可能にする。

【解決手段】

第1素子形成領域(AA1)のうち、第1トランジスタ(Tr1)のゲート電極が形成されるべき第1領域(R1’)の直上に位置するマスク材(M1)の第1部分(H1’)を除去する一方、第1部分(H1’)以外の第1素子形成領域(AA1)にはマスク材(M1)を残存させる。一方、第2素子形成領域(AA2)のうち、第2トランジスタ(Tr2)のゲート電極が形成されるべき第2領域(R1)の直上に位置するマスク材の少なくとも第2部分(H1)と、第2トランジスタ(Tr1)のソース/ドレイン拡散領域が形成されるべき第3領域(R2、R3)の直上に位置するマスク材の少なくとも第3部分(H2,H3)とを除去してマスク材の開口を形成する。

(もっと読む)

半導体記憶装置

【課題】書き込み特性及び電荷保持特性に優れたメモリセル(セルトランジスタ)を具備する半導体記憶装置、或いは、メモリセルと共に製造するのに適した選択又は周辺トランジスタの提供。

【解決手段】セルトランジスタ201は、基板101上に、FNトンネル膜として機能するゲート絶縁膜111、最下層の浮遊ゲートに相当する第1の浮遊ゲート112を備える。更に、FNトンネル膜として機能する第1の浮遊ゲート間絶縁膜113を介して形成され、前記セルトランジスタ内の最下層の浮遊ゲートと最上層の浮遊ゲートとの間に介在する第2の浮遊ゲート114を備える。更に、FNトンネル膜として機能する第2の浮遊ゲート間絶縁膜115を介して形成され、前記セルトランジスタ内の最上層の浮遊ゲートに相当する第3の浮遊ゲート116を備える。更に、電荷ブロック膜として機能するゲート間絶縁膜117を介して形成された制御ゲート118を備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及びその製造方法

【課題】フローティングゲートとコントロールゲートとが積層されたスタック構造のゲート電極を有する半導体装置に関し、隣接メモリセル間やメモリセルとビット線との間における短絡不良を防止しうる半導体装置及びその製造方法を提供する。

【解決手段】トンネルゲート絶縁膜22上に、第1の幅を有する導電膜24、ONO膜28、コントロールゲート40を形成する。コントロールゲート40をマスクとして導電膜24をエッチングしてフローティングゲート26を形成した後、層間絶縁膜80を形成し、第1の方向の幅が第1の幅よりも広いコンタクトホール84を形成する。その後、コンタクトホール84の内壁に、サイドウォールスペーサ88を形成する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】選択ゲート電極の側壁にメモリゲート電極を有する不揮発性記憶装置を微細化することができる技術を提供する。

【解決手段】選択ゲート電極CGをダミーパターンの側壁にサイドウォール形状で形成することで、メモリゲート電極MGが選択ゲート電極CGの両壁に形成されなくなり、フォトマスクの位置ずれを考慮する必要がなくなる。また、選択ゲート電極CGをサイドウォール状に形成することで、選択ゲート電極CGのゲート長が縮小しても、選択ゲート電極CGを構成する導電膜の膜厚により精度よく制御することを可能とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、コンタクトプラグと埋め込み型のゲート電極との間に配置される絶縁膜の厚さを十分に確保可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜16を介して、半導体基板11に形成された凹部14の凹部14の一部を埋め込むゲート電極41と、ゲート電極41の上端面41aを覆うように凹部14内を埋め込む絶縁膜18と、凹部14の一方の側面14a側に位置する半導体基板11の主面11aに形成された不純物拡散領域43と、不純物拡散領域43の上面43aを覆うシリコン層21と、半導体基板11の主面11aに形成された第1及び第2の層間絶縁膜23,31に内設され、シリコン層21の上面21aと接触し、かつ下端34bがシリコン層21の上面21aと絶縁膜18の上面18aとの間に配置されたコンタクトプラグ34と、を備える。

(もっと読む)

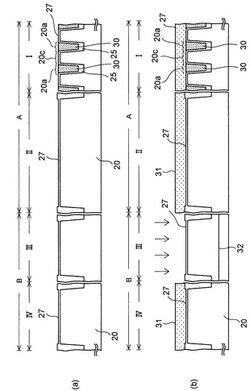

半導体装置およびその製造方法

【課題】トレンチ内に埋め込まれたシリコン層と複数のトレンチ間の半導体基板上に形成されたシリコン層とを同じイオン注入を行ない導電層とすること。

【解決手段】半導体基板10に複数のトレンチ30と、前記複数のトレンチ間の前記半導体基板上に第1キャパシタ絶縁膜22を介し第1シリコン層24と、を形成する工程と、前記複数のトレンチ内に埋め込み絶縁膜36を埋め込む工程と、前記埋め込み絶縁膜を前記複数のトレンチの側面に第2キャパシタ絶縁膜33が残存するように除去し、前記埋め込み酸化膜内に凹部を形成する工程と、前記凹部内の前記第2キャパシタ絶縁膜上と前記複数のトレンチ間の前記第1シリコン層上とに第2シリコン層40を直接形成する工程と、前記凹部内および前記第1キャパシタ絶縁膜上に形成された前記第2シリコン層内に不純物を同時にイオン注入する工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化された不揮発性半導体記憶装置で、隣接セル間の寄生容量によるセル間干渉とトランジスタ特性の劣化を従来に比して抑制する。

【解決手段】チャネル半導体上にゲート誘電体膜21、フローティングゲート電極22、トンネル誘電体膜23および制御ゲート電極24が順に積層され、フローティングゲート電極22と制御ゲート電極24は、トンネル誘電体膜23側に曲率を有する尖端部25,26を有する。また、トンネル誘電体膜23のキャパシタンスがゲート誘電体膜21のキャパシタンスと同等以下となるようにトンネル誘電体膜23とゲート誘電体膜21の厚さが調整される。さらに、制御ゲート電極24の尖端部26からフローティングゲート電極22に電子を注入する処理と、フローティングゲート電極22の尖端部26から制御ゲート電極24に電子を抜き取る処理とを、チャネル半導体と制御ゲート電極24との間に印加される電圧によって制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】基板1Cは、半導体基板2と絶縁層3と半導体層4とが積層されたSOI領域1Aと、半導体基板2で構成されたバルク領域1Bとを有しており、SOI領域1Aの半導体層4に形成されたMISFETは、チャネル領域に不純物が導入されておらず、バルク領域1Bの半導体基板2に形成されたMISFETは、チャネル領域に不純物が導入されている。SOI領域1AのMISFETを形成する際には、MISFETのチャネル領域に不純物が導入されないようにし、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とは行なわない。バルク領域1BのMISFETを形成する際には、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

半導体装置の製造方法

【課題】FEOLにおいても半導体装置のチャージングを効果的に抑制できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に、被保護素子のゲート絶縁膜となる第1の絶縁膜122を形成する工程(a)と、保護素子部302において第1の絶縁膜122の少なくとも一部を除去する工程(b)と、工程(b)よりも後に、被保護素子部301において第1の絶縁膜122の表面を窒化する工程(c)と、工程(c)よりも後に、被保護素子部301及び保護素子部302の上に跨るように導電膜を選択的に形成することにより、互いに接続された被保護素子のゲート電極141及び保護素子の電極142を形成する工程(d)とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

41 - 60 / 403

[ Back to top ]