Fターム[5F083ZA07]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090) | ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA07]に分類される特許

161 - 180 / 403

半導体装置および半導体装置の製造方法

【課題】CMP(Chemical Mechanical Polishing)ストッパ膜を終点検出膜として利用しつつ、CMPによる平坦化精度を向上させる半導体装置及びその製造方法の提供。

【解決手段】ゲート電極3a上にはシリサイド層7aを形成するとともに、ゲート電極3b上にはシリサイド防止膜4bを形成し、半導体基板1上の第1の領域においては、シリサイド防止膜4bが露出するように、犠牲膜10、CMPストッパ膜9および層間絶縁膜8のCMPを行い、第2の領域においては、CMPストッパ膜9が露出するように、犠牲膜10のCMPを行うことで、第1の領域R1および第2の領域R2を平坦化する。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路部のLV系トランジスタでの結晶欠陥の発生を抑制しつつ、HV系トランジスタでの反転リークなどの増加を抑制できるようにするNAND型フラッシュメモリの半導体装置と製造方法を提供する。

【解決手段】LV系トランジスタ領域103のSTI304の上面を、EB加工により、セル領域104のSTI404の上面と同時にエッチングする。こうして、HV系トランジスタ領域102のSTI204の上面の高さはそのままに、LV系トランジスタ領域103のSTI304の上面のみを、第1の電極膜12の上面の高さよりも下げる。上面の高さを下げた分だけ、LV系トランジスタ領域103のSTI304での素子分離用絶縁膜の膜厚を削減して、塗布膜の収縮応力を緩和させる。

(もっと読む)

半導体装置の作製方法

【課題】薄型化及び小型化を達成しながら、外部ストレス、及び静電気放電に耐性を有する信頼性の高い半導体装置を提供することを目的の一とする。また、作製工程においても外部ストレス、又は静電気放電に起因する形状や特性の不良を防ぎ、歩留まり良く半導体装置を作製することを目的の一とする。さらに低コストで生産性高く半導体装置を作製することを目的の一とする。

【解決手段】半導体集積回路を囲いこむように覆う導電性遮蔽体により、半導体集積回路の静電気放電による静電気破壊(回路の誤動作や半導体素子の損傷)を防止する。導電性遮蔽体はめっき法により電気的に接続するように形成する。また、導電性遮蔽体の形成にめっき法を用いるために、低コストで生産性高く半導体装置を作製することができる。

(もっと読む)

チャージトラップ型フラッシュメモリ装置及びその製造方法

【課題】通常のロジックLSI製造プロセスに最小限の変更により、ロジックLSIに組み込むのに適した構成にしたチャージトラップ型のメモリセルを提供する。

【解決手段】本発明は、ゲート絶縁膜としての高誘電率絶縁膜及びゲート電極を有するロジックFETと共に、1チップ内に混載することによりロジックLSIを半導体基板上に構成する。半導体基板上にトンネル絶縁膜として機能する絶縁膜を形成する。この絶縁膜の上に、ロジックFETの高誘電率絶縁膜と同じプロセスフローで実現される高誘電率絶縁膜をチャージトラップ層として形成する。このチャージトラップ層の上に絶縁膜を、かつその上にゲート電極を形成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線コンタクト部のトラップ膜の完全な除去とメモリセル部のゲート電極間の埋め込み充填絶縁膜の十分な残存量確保とを両立する。

【解決手段】複数のビット線拡散層と、複数のワード線と、一対のビット線拡散層、ゲート絶縁膜、及びゲート電極によって構成された複数のメモリ素子と、を含むメモリ領域を有する半導体記憶装置であって、各列における複数に分割された複数のビット線拡散層同士は、ビット線コンタクト拡散層を介して電気的に接続されており、ビット線コンタクト拡散層に隣り合って配置されたワード線に形成されたビット線コンタクト拡散層側の側壁絶縁膜の幅は、ビット線コンタクト拡散層側と反対側に形成された側壁絶縁膜の幅よりも狭い。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】不揮発性メモリを有する半導体装置の特性を向上させる。

【解決手段】シリコン基板1上のメモリ領域Rmに不揮発性メモリを形成する工程であって、シリコン基板1の主面に選択ゲート電極CGを形成し、いずれか一方の側壁面に隣り合うダミーゲートDGを形成する。その後、ダミーゲートDGをイオン注入マスクとしたイオン注入D01によって、メモリソース・ドレイン領域SDmを形成する。その後ダミーゲートDGを除去し、ダミーゲートDGが配置されていた箇所に、電荷蓄積膜とメモリゲート電極とを順に形成することで、メモリゲート電極の側方下部にメモリソース・ドレイン領域SDmが配置された構造を形成する。本工程では、メモリソース・ドレイン領域SDmを形成するためのイオン注入D01を施した後に、電荷蓄積膜とメモリゲート電極とを形成する。

(もっと読む)

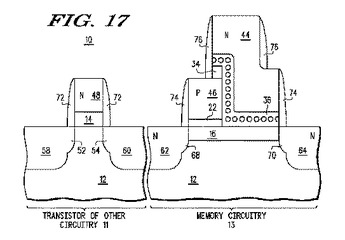

スプリット・ゲート・メモリ・デバイスの形成方法および装置

スプリット・ゲート・メモリ・デバイス(10)は、第1の仕事関数を有する選択ゲート(46)を基板(12)の第1の部分の上に有する。第2の仕事関数を有する制御ゲート(44)は、第1の部分に隣接する基板の第2の部分の上にある。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアが電子であるとき、第1の仕事関数は第2の仕事関数よりも大きい。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアがホールであるとき、第1の仕事関数は第2の仕事関数よりも小さい。基板(12)内の第1の電流電極(62)および第2の電流電極(64)は、制御ゲートおよび選択ゲートの下にあるチャネルによって分離される。制御ゲートおよび選択ゲートの異なる仕事関数は、デバイス性能を最適化するために各ゲートに対して異なる閾値電圧をもたらす。nチャネルデバイスでは、選択ゲートはp導電型であり、制御ゲートはn導電型である。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】微細化の制約が少なく、製造が容易で、周辺回路の大幅な変更を必要としない、NAND型不揮発性半導体記憶装置、及び、その製造方法を提供する。

【解決手段】半導体記憶装置は、基板40の主面41上に並設され、主面41に対して平行な第1方向に延在した複数の積層体58と、主面41に平行で、第1の方向と非平行な第2方向に延在したゲート電極70と、を備え、複数の積層体58のそれぞれは、絶縁層55を介して積層された複数の半導体層50を有し、複数の積層体58は、隣接する積層体58の間隔が、第1間隔51と、第1間隔51よりも広い第2間隔52と、が交互に設けられるように並設され、第2間隔52の周期は、デザインルールFの4倍であり、ゲート電極70は、第2間隔52を有する積層体58同士の間隙に侵入した突出部78を有し、半導体層50の側面と突出部78との間に、第1絶縁膜、電荷蓄積層60及び第2絶縁膜を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作特性を向上させる半導体記憶装置及びその製造方法を提供すること。

【解決手段】基板10中に形成された第1及び第2活性領域AAと、分離する素子分離領域32と、積層ゲートと、ソース及びドレインとして機能する第1不純物拡散層とを備えたメモリセルとを具備し、前記積層ゲートは、前記基板10上に形成され且つ電荷を蓄積する第1絶縁膜15と、前記第1絶縁膜15上に該第1絶縁膜15よりも誘電率の高い材料を用いて形成された第2絶縁膜16と、前記第2絶縁膜16上に形成された制御ゲート電極17とを備え、前記第2絶縁膜16は、前記素子分離領域32を跨ぐようにして複数の前記メモリセル間で共通に接続され、且つ前記素子分離領域32の上面に接し、前記素子分離領域32の上面は、前記第1絶縁膜15の底面よりも高く、且つ該第1絶縁膜15の上面以下に位置する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】電界集中を避けるためのフローティングゲート電極の上面の丸め加工で、ゲート高さのバラツキを低減する、積層ゲート構造を有する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】シリコン基板1にゲート絶縁膜5、多結晶シリコン膜6、加工用絶縁膜を積層して、RIE法によりエッチングをして溝1a、1bを形成し、溝内にシリコン酸化膜を埋め込んでCMP処理をする。メモリセル領域のみシリコン酸化膜をエッチングして落とし込み、この後、下層レジストを塗布してメモリセル領域のエッチングをする。下層レジストがエッチングされて多結晶シリコン膜6が露出すると上面端部6aが丸み加工される。これにより、多結晶シリコン膜6の上部のみを露出させて丸み加工ができ、高さのバラツキを低減できる。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】動作信頼性を向上させるNAND型フラッシュメモリ等の半導体記憶装置、及びその製造方法を提供する。

【解決手段】半導体基板中10の第1活性領域上に第1ゲート絶縁膜14を介在して形成され、電荷を蓄積する第1絶縁膜15と、第1絶縁膜15上に、第1絶縁膜15よりも誘電率の高い材料を用いて形成された第2絶縁膜16と、第2絶縁膜16上に形成された第1金属膜18と、第1金属膜18上にシリサイド膜で形成された制御ゲート電極17と、ソース及びドレインとして機能する不純物拡散層13とを備えたメモリセルトランジスタMTと、半導体基板中10の第2活性領域上に第2ゲート絶縁膜33を介在して形成された第1導電膜35と、第1導電膜35上に形成された第2金属膜19と、第2金属膜19上にシリサイド膜で形成された第2導電膜17とを含む積層ゲートを備えたMOSトランジスタとを具備する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】占有面積を縮小した不揮発性半導体記憶装置、製造方法を提供する。

【解決手段】不揮発性半導体記憶装置100は、メモリセルトランジスタ層30、第2CMP用ダミー層70を備える。メモリセルトランジスタ層30は、半導体基板Baに平行で且つ積層された第1〜第4ワード線導電層と32a〜32d、メモリ保護絶縁層34を備える。第1〜第4ワード線導電層32a〜32dの端部は、ロウ方向にて階段状に形成されている。第2CMP用ダミー層70は、半導体基板Baに平行で且つ積層されて第1〜第4ワード線導電層32a〜32dと同層に形成されたダミー第1〜第4ワード線導電層72a〜72d、ダミーメモリ保護絶縁層74を備える。ダミー第1〜第4ワード線導電層72a〜72dの端部は、配線領域Arにて半導体基板Baに対して略垂直方向に延びる直線に沿って揃うように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接セル間のキャパシタ容量を小さくし、隣接セル間干渉を抑制する。

【解決手段】本発明の半導体装置は、半導体基板2と、半導体基板2の上に形成されたゲート絶縁膜8と、ゲート絶縁膜8上に形成された浮遊ゲート電極9と、半導体基板2の表面に形成された素子分離溝3と、素子分離溝3内に埋め込まれた下部と、半導体基板2の表面から上方に突出した上部とからなる素子分離絶縁膜5とを有し、素子分離絶縁膜5内には上部から下部にわたり空洞部が形成されたものである。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】プロセス中における高誘電体膜の構成原子の飛散を防止することでデバイス特性の劣化を回避する。

【解決手段】メモリセル110とトランジスタ120とがシリコン基板101に形成された不揮発性半導体記憶装置100において、トランジスタ120を構成する積層膜120Tの側面に、少なくとも高誘電体膜124の側面を覆うサイドウォール127を下部ゲート122からシリコンゲート126にかけて形成する。サイドウォール127の材料としては、例えばSiGeなどのような高誘電体膜124の構成原子が飛散することを防止可能な導電体を用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルにおける下層電極と上層電極との界面及び保護ダイオードにおける基板とダイオード電極との界面に、均一で且つ最適な膜厚の酸化膜が形成された半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1の界面膜53Aを介在させて、第1の導電膜からなる第1の下層電極51Aと、第2の導電膜からなる第1の上層電極52Aとが積層された第1の積層電極22を有するメモリセル12と、第2の導電膜からなるダイオード電極52Bと、ダイオード電極32と基板15との界面に形成されたシリコン酸化膜である第2の界面膜53Bとを有するダイオード13とを備えている。第1の界面膜53Aは、下層電極51Aと上層電極52Aとの電気的接続を維持する膜厚であり、第2の界面膜53Bは、基板15とダイオード電極52Bとの間におけるエピタキシャル成長を阻害する膜厚である。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離領域の深さを抑制しながら耐圧の低下を抑制できるNAND型フラッシュメモリ等の半導体装置を提供する。

【解決手段】ゲート電極PGが、隣り合う素子分離膜間のアクティブエリアAA上にゲート絶縁膜11を介してゲート長方向に離間して並設されている。ゲート電極PGを構成する多結晶シリコン層14は、アクティブエリアAAの片脇に位置する素子分離膜の上面上に張り出す一端部14aと、アクティブエリアAAの逆脇に位置する素子分離膜の上面上に張り出す他端部14bとを備えており、一端部14aの長さL1と一端部14bの長さL2が互いに異なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】 周辺回路領域の電荷蓄積層へのホットキャリア注入の影響を少なくする半導体装置等を提供する。

【解決手段】 半導体装置であって、少なくとも1つの不揮発性記憶セルの少なくとも1つの第1のトランジスタと、前記少なくとも1つの不揮発性記憶セルを駆動するための少なくとも1つの第2のトランジスタと、を含む。第1のトランジスタは、第1のゲート絶縁層と、第1のゲート電荷蓄積層と、第2のゲート絶縁層とを有する。第2のトランジスタは、第3のゲート絶縁層と、第2のゲート電荷蓄積層と、第4のゲート絶縁層とを有する。フッ素系ガスおよび/または水素系ガスを用いるイオン注入が実施された前記第2のゲート電荷蓄積層(22b’)の全部または一部の第1の電荷蓄積能力は、フッ素系ガスおよび/または水素系ガスを用いるイオン注入が実施される前の前記第2のゲート電荷蓄積層(22b’)の前記全部または前記一部の第2の電荷蓄積能力より低い。

(もっと読む)

半導体装置およびその製造方法

【課題】MONOS型不揮発性記憶装置を含む、高い性能を有する半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、MONOS型不揮発性記憶セルの第1のトランジスタと、記憶セルを制御または駆動するための第2のトランジスタを含む。第1のトランジスタは、ソースドレイン領域12,13,18,19と,ゲート絶縁層22a’と、ゲート電荷蓄積層22b’と、第2のゲート絶縁層22c’と、ゲート導電層14’と、絶縁層16,17、とを有する。ゲート絶縁層22a’は、ソースドレイン領域の一部12,13の上に形成された下層60と、下層60の一部である中心部の上に形成された上層61とを有する。第2のトランジスタの第2のソースドレイン領域12,13,18,19を形成するために用いられたレジストを洗浄除去するときに、下層60と上層61とに区別された。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】耐圧が改善され、信頼性が向上した不揮発性半導体メモリ及びその製造方法を与える。

【解決手段】半導体記憶装置は、半導体基板11上に形成され、オキシナイトライド化された第1ゲート絶縁膜14aを含む第1トランジスタと、半導体基板11上に形成された第2ゲート絶縁膜14bと、第2ゲート絶縁膜14b上の少なくとも一部に形成されたバリア膜20を含む第2トランジスタとを備え、前記第2ゲート絶縁膜は、前記第1ゲート絶縁膜より窒素原子濃度が低いことを特徴とする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】2つの異なったゲート電極を有するトランジスタを備えた不揮発性半導体記憶装置およびその製造方を提供する。

【解決手段】半導体基板11の第1領域11aに第1ゲート絶縁膜14を介して形成された第1ゲート電極15、第2ゲート絶縁膜16、第2ゲート電極17を有するセルトランジスタと、第1ゲート電極15側へ突出した状態に埋め込まれた第1絶縁分離層12とを備えたメモリセルを形成する工程と、第2領域11bに第1ゲート絶縁膜14を介して形成され、高さL2が第1ゲート電極15の高さL3より大きい第1導電膜20と、高さL4が第2ゲート電極17の高さL5と等しい第2導電膜21とを有するゲート電極を備えたトランジスタと、高さL6が第1絶縁分離層12の高さL1より大きく第1導電膜20側へ突出した状態に埋め込まれた第2絶縁分離層13を形成する工程と、を具備する。

(もっと読む)

161 - 180 / 403

[ Back to top ]