Fターム[5F083ZA30]の内容

Fターム[5F083ZA30]に分類される特許

1 - 20 / 136

半導体装置

半導体装置

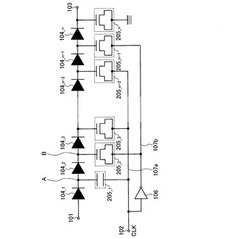

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置のスイッチング耐久性の向上を図る。

【解決手段】実施形態によれば、半導体記憶装置は、複数のセルアレイブロックと、制御回路とを備えている。制御回路は、選択ビット線を0ボルトにし、選択ワード線に0ボルトよりも高い第1の電位を与え、非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、選択セルアレイブロックに第1の方向で隣接し選択ビット線を選択セルアレイブロックと共有する隣接セルアレイブロックにおける、選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、選択メモリセルの抵抗変化膜の抵抗状態を変化させる。

(もっと読む)

半導体装置

【課題】不要にリフレッシュ周期が変更されることによる無駄な消費電流を削減する。

【解決手段】複数の半導体チップを備え、複数の半導体チップのうちの第1の半導体チップは第1の温度センサを有し、第1の半導体チップとは異なる第2の半導体チップはリフレッシュ動作を必要とする半導体チップであって、第1の半導体チップの第1の温度センサの出力結果に応じて第2の半導体チップのリフレッシュ周期が変更される。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

可変抵抗絶縁層を用いたメモリ素子及びそれを有するプロセッサシステム

【課題】可変抵抗材料を用いて形成されるランダムアクセスメモリ装置を提供する。

【解決手段】可変抵抗メモリ装置301において、望ましい円錐状に形造された下部電極308は、下部電極308の頂点のところにおける絶縁材料312の厚さが最も薄く、下部電極308の頂点のところにおける電界が最大であることを確保する。電極308、310の配置およびメモリ素子の構造はメモリ装置内に安定で確実に導電路を作り出し、かつ、スイッチングとメモリ特性を再生可能にする。

(もっと読む)

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

半導体装置

【課題】配線基板上にメモリチップとマイコンチップとを搭載してシステムを構成するシステム・イン・パッケージ(SIP)型半導体装置の小型化、高速化を推進する。

【解決手段】配線基板10の上面にマイコンチップ20とメモリチップ30を搭載する際、メモリチップ30の第1チップ辺31a(データ系電極パッド33Dが配置された辺)に沿って配置された配線基板10の第2導電パッド15が、平面視において、マイコンチップ20の第3チップ辺21cの延長線と第4チップ辺21dの延長線との間の領域に位置するようにメモリチップ30を配置することで、マイコンチップ20のデータ系電極パッド23Dとメモリチップ30のデータ系電極パッド33Dとを接続するデータ系配線16Dの長さを最短化する。

(もっと読む)

半導体装置

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶装置及びそれを有する半導体装置を提供することを課題とする。また、信頼性が高く、安価な不揮発の記憶装置及び半導体装置の提供を課題とする。

【解決手段】絶縁表面上に形成される第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層に挟持される第1の絶縁層と、第1の導電層の一部を覆う第2の絶縁層とを有し、第1の絶縁層は第1の導電層の端部、絶縁表面、及び第2の絶縁層を覆うことを特徴とする記憶装置である。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

集積回路装置の製造方法

【課題】金属部材の劣化を抑えた集積回路装置の製造方法を提供する。

【解決手段】実施形態に係る集積回路装置の製造方法は、ハロゲンを含むガスを用いて金属部材をエッチングする工程と、エッチングされた前記金属部材を大気に曝すことなく、前記金属部材のエッチング面を覆うようにシリコン酸化膜を形成する工程と、前記シリコン酸化膜を除去する工程と、を備える。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ReRAM用のダイオードを形成するために、アモルファス半導体膜の表面に酸化膜が形成された場合であっても、アモルファス半導体膜を結晶化することが可能な半導体装置の製造方法を提供する。

【解決手段】基板101上に、下部電極層111とアモルファス半導体膜112を形成し、アモルファス半導体膜112上の自然酸化膜121を介して、還元性のある金属層113Aを含む上部電極層113を形成し、マイクロ波を用いたアニールにより、金属層113Aと酸化膜121を反応させて、酸化膜121を半導体へと還元する。また、アニールにより更に、金属層113Aと半導体112を反応させて、金属層113Aの構成元素と半導体112の構成元素とを含む反応生成物113Cを生成する。また、反応生成物113Cを結晶成長のためのシードとして、アモルファス半導体膜112を結晶成長させる。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】バイポーラ駆動でセット動作、リセット動作を確実に行うことができる不揮発性記憶装置及びその製造方法を提供する。

【解決手段】第1電極であるワード線WLと、第2電極であるビット線BLと、ワード線WLとビット線BLとの間に設けられ、第1抵抗状態と第2抵抗状態とのあいだを遷移する抵抗変化部25と、抵抗変化部25とワード線WLとの間に設けられ、p形半導体を含むp層22pと真性半導体を含むi層22iとn形半導体を含むn層22nとを有し、真性半導体よりもバンドギャップエネルギーの小さい不純物220であって、i層22iにおける濃度のピークがi層22iの層厚における中央部にある不純物220を含む選択素子22と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】相変化材料層をヒータ電極で加熱して抵抗値を変化させ、情報の記憶を行う相変化メモリを備える半導体装置において、工程数を削減してヒータ部の電流密度を高くする製造方法並びに構造を提供する。

【解決手段】ヒータ電極10を覆う層間絶縁膜13に、ヒータ電極10上面と同形状であり、全面を露出する開口部が形成されており、開口部に絶縁材料からなるサイドウォール15が形成されており、相変化材料層16は、サイドウォール10の形成された開口部内でヒータ電極10と接触しており、相変化材料層16における相変化領域18はサイドウォール10で囲まれた開口部内に形成される。

(もっと読む)

炭素/トンネル障壁/炭素・ダイオード

炭素/トンネル障壁/炭素・ダイオード及び炭素/トンネル障壁/炭素・ダイオードの形成方法を開示する。炭素/トンネル障壁/炭素はメモリアレイ内でステアリング素子として用いられてもよい。メモリアレイ内の各メモリセルは可逆的抵抗性スイッチング素子、及びステアリング素子として炭素/トンネル障壁/炭素・ダイオードを含んでいてもよい。トンネル障壁は半導体又は絶縁体を含んでいてもよい。従って、ダイオードは炭素/半導体/炭素・ダイオードであってもよい。ダイオード内の半導体は真性であってもよいし、ドープされていてもよい。ダイオードが平衡状態にある場合は、半導体が空乏化されることがある。例えば、空乏領域が半導体領域の一端から他端まで延びるように、半導体が低濃度にドープされてもよい。ダイオードは炭素/絶縁体/炭素・ダイオードであってもよい。 (もっと読む)

半導体記憶装置

【課題】正確な配線構造を得つつも、メモリセルに対し所望の電圧を供給することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ビット線BLとワード線WLとの各交差部に配置されたメモリセルMCを含むメモリセルアレイMAと、ワード線WLと同一の配線層に形成され、ビット線ドライバ25の上部の領域でビット線BLと交差するように形成されたダミーワード線DummyWLとを備える。ビット線ドライバ25は、選択ビット線BLに電圧VWRを印加する。ワード線ドライバ23は、選択ワード線WLに電圧VSSを印加するとともに、ダミーワード線DummyWLに、選択駆動されたビット線BLとダミーワード線DummyWLとの交差部に配置されるメモリセルMCにかかる電位差がダイオードDiのオン電圧Vonより小さくなるような電圧値の電圧VUX’を印加する。

(もっと読む)

1 - 20 / 136

[ Back to top ]