Fターム[5F092AA11]の内容

Fターム[5F092AA11]に分類される特許

1 - 20 / 299

プラズマ処理方法

磁気抵抗素子の製造方法

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

三次元磁界センサおよびその製造方法

【課題】構成が簡単で、製造コストを低減できる三次元磁界センサを実現する。

【解決手段】三次元磁界センサ1は、平面である素子配置面40aを有する基板40と、基板40の素子配置面40a側に配置されて基板40と一体化されたMR素子10,20,30を備えている。MR素子10は、磁化固定層11、非磁性層12および自由層13を有し、MR素子20は、磁化固定層21、非磁性層22および自由層23を有し、MR素子30は、磁化固定層31、非磁性層32および自由層33を有している。自由層13,23,33の磁化の方向は、外部磁界Hの方向に応じて変化する。磁化固定層11の磁化の方向は、素子配置面40aに平行なX方向に固定されている。磁化固定層21の磁化の方向は、素子配置面40aに平行であってX方向に直交するY方向に固定されている。磁化固定層31の磁化の方向は、素子配置面40aに垂直なZ方向に固定されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

被膜部材の製造方法

【課題】より高い特性を有する膜体を形成する。

【解決手段】被膜部材10の製造方法は、スパッタリングターゲット部材を用い、スパッタリング処理によって被処理部材11に膜体12を形成する形成工程、を含むものである。この形成工程では、1又は複数のスパッタリングターゲット部材を用い、Mg、Al、O及びNの元素を含む膜体12を被処理部材11の表面に形成する処理を行う。ここで、スパッタリングターゲット部材は、Mg、Al、O及びNの全てが含まれていれば、どのような形態でも構わず、スパッタリングターゲット部材を1種用いるものとしてもよいし、スパッタリングターゲット部材を複数種用いるものとしてもよい。被処理部材11に形成された膜体12には、Mg、Al、O及びNが含まれている。

(もっと読む)

磁気抵抗素子構造の製造方法

【課題】本発明は、磁気抵抗材料と集積回路とを巧みに統合することのできる、磁気抵抗素子構造の製造方法を提供する。

【解決手段】基板を提供する工程と、上記基板の上に金属ダマシン構造を形成する工程と、該金属ダマシン構造に電気的に接続するように該金属ダマシン構造の上にパターン化磁気抵抗ユニットを形成する工程とを含む、磁気抵抗素子構造の製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

角度検出センサおよびその製造方法

【課題】1つの基板に設けた複数の磁気抵抗素子部のピン磁性層を異なる方向に着磁させる。

【解決手段】基板10を用意し、基板10の一面13の上方に複数の磁気抵抗素子部22を形成する。次に、基板10において一面13から他面14までを貫通する貫通孔15を形成する。続いて、基板10の一面13側と他面14側とのいずれか一方から他方に貫通孔15を介して電流が流れる直線状の電流供給ライン40を形成する。ここで、電流供給ライン40としてワイヤ41を用いる。この後、ワイヤ41に電流を流すことによってワイヤ41の周囲にワイヤ41を中心とした同心円状の磁界を発生させると共に、基板10全体を加熱して磁場中アニールを行う。これにより、複数の磁気抵抗素子部22を構成するピン磁性層22aの磁化の向きがそれぞれ同心円状の磁界の接線方向に向くように着磁を行う。

(もっと読む)

磁気デバイスの製造方法

【課題】ダイシングストリートにGaAsが露出している場合、結果ダイシング時に素子のチッピング、電極や磁性体の剥離、溶解したGaAsによる電極接合部の汚染が発生し、さらにGaAs基板裏面もエッチングされるためGaAsの溶解による電極接合部の汚染の課題がある。

【解決手段】本発明は、ホール素子が設けられたGaAs基板と、GaAs基板上に設けられた磁気増幅機能を有する磁性体とを備える磁気デバイスにおいて、上記ホール素子上に絶縁層と、上記絶縁層上にTi系金属層と、上記Ti系金属層の上にCu系金属層とを有し、ダイシングストリート上を少なくとも無機絶縁材料乃至有機絶縁材料もしくはその両方でカバーさせGaAsを露出させず、またさらにGaAs基板裏面にも有機絶縁膜でカバーすることにより本課題を解決した。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

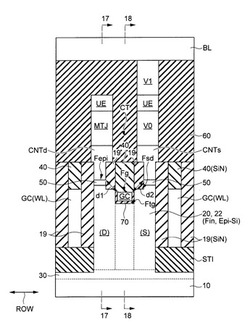

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。フェンス層の頂点は、側壁膜の頂点よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセル部及び周辺回路部を微細化する。

【解決手段】半導体基板20に設けられたメモリセル部11及び周辺回路部12を有する半導体記憶装置の製造方法であって、メモリセル部11及び周辺回路部12にそれぞれ層間絶縁層37及び47を形成する工程と、層間絶縁層37及び47上にそれぞれ、心材50を形成する工程と、心材50をスリミングする工程と、メモリセル部11及び周辺回路部12の心材50の側面にそれぞれ、側壁38及び48を形成する工程と、側壁38及び48をマスクとして、層間絶縁層37及び47を加工する工程と、加工された層間絶縁層37及び47内にそれぞれビット線BL及び配線層44を形成する工程とを含む。

(もっと読む)

磁気センサ

【課題】被実装部材上に回路チップと隣接して搭載される磁気センサにおいて、回路チップとパッドとを電気的に接続するワイヤ同士の接触を抑制することができる磁気センサを提供する。

【解決手段】複数のパッド31〜36を一辺10aと垂直方向において互いに完全にオフセットした状態で配置する。これによれば、被実装部材上に磁気センサの一辺10aを回路チップと隣接して搭載し、パッド31〜36と回路チップとをワイヤで接続した際に、ワイヤ同士が接触してしまうことを抑制することができる。

(もっと読む)

電子部品の実装構造

【課題】実装時における位置ズレが生じる従来の電子部品の実装構造に対して、半田ブリッジの発生を防止しつつ、実装の際に角度ずれが小さいことが要求される電子部品の取り付け角度の精度を高められる電子部品の実装構造を目的とする。

【解決手段】電子部品の実装構造において、電子部品が略直方体形状の基体の側面から複数のリード端子を延出しており、複数のリード端子が基体の四隅の内少なくとも2個所に設けられたアライメント用リード端子とアライメント用リード端子を除く電気的に基体内の電子回路に接続される電極リード端子とからなり、アライメント用リード端子が電極リード端子より長く延出されており、複数の接続ランドがアライメント用リード端子と半田付けされるアライメント用接続ランドと電極リード端子と半田付けされる電極用接続ランドとからなり、アライメント用接続ランドの長さが電極用接続ランドの長さよりも長いことを特徴としている。

(もっと読む)

改良されたトンネル障壁を有する磁気トンネル接合

【課題】磁気ランダムアクセスメモリ(MRAM)セル用に適し且つ第1強磁性層とトンネル障壁層と第2強磁性層とから成る磁気トンネル接合を製作する方法を提供する。

【解決手段】第1強磁性層を形成すること、トンネル障壁層22を形成すること及び第2強磁性層を形成することから成る。当該トンネル障壁層22を形成することは、金属製のMg層を蒸着すること及び当該金属のMgをMgO層22aに変えるために当該蒸着された金属製のMg層を酸化することから成る。当該トンネル障壁層が、少なくとも2つのMgO層22aから成るように、当該トンネル障壁層を形成するステップが、少なくとも2回実施される。

(もっと読む)

機能性薄膜素子及びその製造方法

【課題】薄膜積層型の機能性薄膜素子において、電極間の電流リークを防止する。

【解決手段】非導電性基板11上に金属機能薄膜を成膜し、この金属機能薄膜から所定の機能パターン12を形成した後に、その保護のために機能パターン12の上に非導電性薄膜である保護膜13を形成する。更に、電極膜を成膜してエッチングにより電極14a、14bを形成し、非導電性基板11の切断に際し保護膜13に設けた切断部13a、13bを共に切断し、保護膜13の周囲に生じた電極膜の残渣Sによる電極14a、14b間の電流リークを防止する。

(もっと読む)

磁気メモリ構造およびトンネル磁気抵抗効果型再生ヘッドならびにそれらの製造方法

【課題】十分に高い抵抗変化率および絶縁破壊電圧を確保しつつ、安定した製造に適した磁気トンネル接合素子を備えた磁気メモリ構造を提供する。

【解決手段】この磁気メモリ構造は、基体上に、第1シード層と導電層とを順に有する下部電極と、導線としての上部電極と、下部電極と上部電極との間に配置され、かつ、下部電極の側から順に、下部電極と接すると共に窒化タンタルを含む第2シード層と、反強磁性ピンニング層と、ピンド層と、トンネルバリア層と、磁化自由層と、上部電極と接するキャップ層とを有する磁気トンネル接合素子とを備える。窒化タンタルは、窒素プラズマをタンタルのターゲットに衝突させる反応性スパッタリング処理によって形成されたものである。

(もっと読む)

コバルト薄膜およびその形成方法ならびにナノ接合素子およびその製造方法ならびに配線およびその形成方法

【課題】厚さが35nm以下でも十分に高い保磁力および角型比を有する磁性のコバルト薄膜を得ることができるコバルト薄膜の形成方法およびこの方法により形成したコバルト薄膜を用いたナノ接合素子を提供する。

【解決手段】ポリエチレンナフタレート基板11上に真空蒸着法などによりコバルト薄膜12を35nm以下の厚さに成膜する。こうしてポリエチレンナフタレート基板11上にコバルト薄膜12を成膜した積層体を二つ用い、これらの二つの積層体をそれらのコバルト薄膜12のエッジ同士が、必要に応じて有機分子を挟んで、互いに対向するように交差させて接合することによりナノ接合素子を構成する。このナノ接合素子により不揮発性メモリや磁気抵抗効果素子を構成する。ポリエチレンナフタレート基板11の代わりに、少なくとも一主面がSiO2 からなる基板、例えば石英基板を用いてもよい。

(もっと読む)

半導体装置の製造方法

【課題】FinFETの特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板の上層部分に凹部を形成する工程と、前記凹部内に犠牲材を配置する工程と、前記半導体基板及び前記犠牲材を選択的に除去することにより、一方向に延び、周期的に配列された複数本のフィンを形成する工程と、前記フィン間の空間の下部に素子分離絶縁膜を形成する工程と、前記犠牲材を除去する工程と、前記フィンの露出面上にゲート絶縁膜を形成する工程と、前記素子分離絶縁膜上に、前記フィンを跨ぐように、前記一方向に対して交差した方向に延びるゲート電極を形成する工程と、を備える。

(もっと読む)

1 - 20 / 299

[ Back to top ]