Fターム[5F092AA12]の内容

Fターム[5F092AA12]に分類される特許

1 - 20 / 181

半導体装置、および、その製造方法

【課題】電流により発生する磁場を化合物半導体回路で集約して検出することができる小型で、高感度かつ高精度な電流センサを実現すること。

【解決手段】半導体回路(LSI回路)と化合物半導体回路(ホール素子を有する化合物半導体素子)とが形成された基板に、さらに、化合物半導体素子の直上に、該直下の化合物半導回路に対して磁束密度を増加させるための所定の形状からなる電気配線(コ字型または馬蹄型の形状を呈した金属配線)を形成し、この電気配線に被検出電流を流すようにした。

(もっと読む)

高周波磁界発生素子、磁気ヘッド、磁気ヘッドアセンブリ及び磁気記録装置

【課題】記録密度を向上できる高周波磁界発生素子、磁気ヘッド、磁気ヘッドアセンブリ及び磁気記録装置を提供する。

【解決手段】実施形態に係る高周波磁界発生素子は、第1固定層と、第1自由層と、第2自由層と、を備える。第1固定層は、磁化の方向が固定であって磁化の方向に第1方向と平行な成分が含まれる。第1自由層は、第1固定層と積層される。第1自由層は、磁化の方向が可変であって磁化の方向に第1方向と直交する成分が含まれる。第2自由層は、第1固定層と積層される。第2自由層は、磁化の方向が可変であって磁化の方向に第1方向と直交する成分が含まれる。第1固定層は、第1自由層と第2自由層との間に設けられる。第1自由層の磁化及び第2自由層の磁化は、第1自由層、第2自由層及び第1固定層に流れる電流により発振する。第1自由層の発振における磁化の回転方向は、第2自由層の発振における磁化の回転方向に対して逆である。

(もっと読む)

縮小されたビットセル寸法を有するスピン注入トルク磁気抵抗ランダムアクセスメモリ

【課題】スピン注入トルク磁気抵抗ランダム・アクセス・メモリ(STT−MRAM)のメモリセル寸法を縮小する。

【解決手段】ワード・ラインWLに対して実質的に平行にかつビット・ラインBLに対して実質的に垂直にソース・ラインSLを配列することによって、縮小されたビット・セル寸法が達成される。さらに、1つの実施の形態では、書込み動作時に、無効な書込み動作を防止するために、選択されないビット・セルのビット・ラインにハイ論理/電圧レベルが印加される。

(もっと読む)

シザーズ構造を有する磁気抵抗センサの磁気バイアス構造

【課題】 シザーズ構造を有する磁気抵抗センサの磁気バイアス構造を提供する。

【解決手段】 磁気バイアス付与の堅牢性を向上させる新規のハードバイアス構造を有するシザーズ型磁気センサ。当該センサは、電気絶縁障壁層または導電スペーサ層等の非磁性層により分離された第1の磁気層および第2の磁気層を含むセンサスタックを含む。第1の磁気層および第2の磁気層は、逆平行に結合されるが、磁気バイアス構造により、エアベアリング面に対して平行でも垂直でもない方向に傾けられた磁化方向を有する。磁気バイアス構造は、センサスタックの後縁から延在し、センサスタックの第1の側面および第2の側面に整列した第1の側面および第2の側面を有するネック部を含む。バイアス構造はまた、ネック部から後方に延在する先細または楔形部を含む。

(もっと読む)

磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路

【課題】 本発明の実施形態によれば、単方向電流で書き込みが可能であり、微細化が可能な磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路を提供することができる。

【解決手段】 磁気メモリ素子は、磁化が可変の第1の強磁性層と、第1のバンド及び第2のバンドを有する第2の強磁性層と、前記第1の強磁性層と前記第2の強磁性層との間に設けられた非磁性層と、を備える。

(もっと読む)

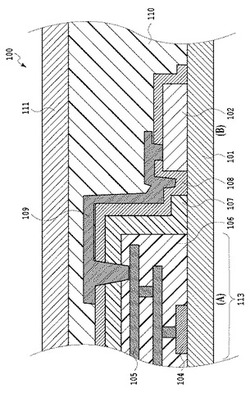

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

半導体装置及び磁気ランダムアクセスメモリ

【課題】磁壁移動型MRAMのメモリセルの面積を低減する。

【解決手段】メモリセル200−1が、固定層11と磁気記録層21とリファレンス層41とトンネルバリア膜31とMOSトランジスタ51とを備えており、メモリセル200−2が、固定層13と磁気記録層22とリファレンス層42とトンネルバリア膜32とMOSトランジスタ52とを備えている。固定層11、13は、第1方向に固定された磁化を有している。第1方向と反対の第2方向に固定された磁化を有する固定層12が磁気記録層21、22に接合されている。固定層12と共通ビット線CBLとが、それらの間の電気的接続が分離不能であるように接続される。

(もっと読む)

記憶装置及びその製造方法

【課題】磁気トンネル接合素子を用いた構造において、製造工程の簡素化を達成することができる記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、第1信号線と、第2信号線と、トランジスタと、記憶領域と、導通領域と、を備える。トランジスタは、第1信号線と、第2信号線と、のあいだを流れる第1方向の電流及びこれと反対の第2方向の電流の導通を制御する。記憶領域は、第1信号線と、トランジスタの一方端と、のあいだに接続され、第1の平行閾値以上の電流が第1方向に流れると磁化の向きが平行になり、第1の反平行閾値以上の電流が第2方向に流れると磁化の向きが反平行になる第1磁気トンネル接合素子を有する。導通領域は、第2信号線と、トランジスタの他方端と、のあいだに接続される。

(もっと読む)

記憶装置及びその製造方法

【課題】多値化にあたり素子構造及び製造工程の簡素化を達成する。

【解決手段】記憶装置は、第1信号線、第2信号線、トランジスタ、第1記憶領域、第2記憶領域、を備える。トランジスタは、第1、第2信号線間を流れる第1方向及びこれと反対の第2方向の電流の導通を制御する。第1記憶領域は、第1信号線とトランジスタの一方端とのあいだに接続される。第1記憶領域は、第1の平行閾値以上の電流が第1方向に流れると磁化の向きが平行になり、第1の反平行閾値以上の電流が第2方向に流れると反平行になる第1磁気トンネル接合素子を有する。第2記憶領域は、第2信号線とトランジスタの他方端とのあいだに接続される。第2記憶領域は、第1の平行閾値よりも大きな第2の平行閾値以上の電流が第2方向に流れると平行になり、第1の反平行閾値よりも大きな第2の反平行閾値以上の電流が第1方向に流れると反平行になる第2磁気トンネル接合素子を有する。

(もっと読む)

筐体

【課題】小型化が可能で、部品の搭載、及び部品間の電気的な接続を容易に行うことができる筐体を提供する。

【解決手段】筐体1は、電子部品が搭載される搭載領域27の周囲の高さが搭載領域27の高さ以下であり、配置されたリードフレーム4a及びリードフレーム4bの表面が露出する基部2a、及びリードフレーム4a及びリードフレーム4bの表面の一部が覆われる被覆部2b、を有する第1の筐体2と、第1の筐体2の形状に応じて形成され、第1の筐体2と溶着される溶着部36を有する第2の筐体3と、を備える。

(もっと読む)

情報格納装置

【課題】より容易な方法で集積度を向上させた情報格納装置を提供する。

【解決手段】本発明の情報格納装置は、基板と、基板上のゲートライン構造体を含むトランジスターと、少なくとも一部が基板内に埋め込まれてトランジスターの活性領域を定義する導電性分離パターン(conductive isolation patterns)と、を有し、導電性分離パターンは、互いに電気的に連結される。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】磁壁移動型MRAMのメモリセルの面積を小さくする。

【解決手段】磁気ランダムアクセスメモリが、メモリセルC1〜C3が形成されたメモリセルライン1と、書き込みビット線12−1〜12−4とを具備する。メモリセルライン1は、磁気記録層4と、磁化固定層3−1〜3−4と、リファレンス層6−1〜6−3と、スペーサ層5−1〜5−3と、nMOSトランジスタ2−1〜2−4とを備えている。スペーサ層5−iとリファレンス層6−iとは、磁化固定層3−iと磁化固定層3−(i+1)の間に位置している。磁化固定層3−1、3−3と、磁化固定層3−2、3−4は、互いに逆の方向に固定された磁化を有している。リファレンス層6−1〜6−3も、固定された磁化を有している。nMOSトランジスタ2−iは、書き込みビット線12−iと磁化固定層3−iの間に設けられている。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

磁気検出装置とその製造方法

【課題】本発明は、小型化に優れると共に高精度な電気抵抗の調整が可能である磁気検出装置とその製造方法を提供することを目的とする。

【解決手段】第一の短絡層41と第二の短絡層42とを、それぞれ第一の磁気抵抗効果素子層11と第一の抵抗素子層21とにのみ導通させ且つ一体に積層させて短絡することで、第一の磁気抵抗効果素子層11と第一の抵抗素子層21との電気抵抗を調整する。

(もっと読む)

半導体装置及び磁気ランダムアクセスメモリ

【課題】高速な読み出し動作に適しながらメモリセルの面積を低減することができる磁壁移動型の磁気ランダムアクセスメモリを提供する。

【解決手段】メモリセル10が、磁気記録層2と、固定層11、12と、磁気記録層2に対向するように設けられたリファレンス層41、42、43と、トンネルバリア膜31、32、33とを備えている。固定層11は上方向に固定された磁化を有し、固定層12は、下方向に固定された磁化を有している。リファレンス層41、42、43は、上方向に固定された磁化を有している。リファレンス層41、42、43及びトンネルバリア膜31、32、33は、固定層11、12の間の位置に設けられている。

(もっと読む)

磁気記録再生装置

【課題】 高い信号出力を有するスピン蓄積型磁気再生ヘッドおよび高密度の磁気記録再生装置を提供する。

【解決手段】 第1の電極層の一端上に、第1の絶縁層を介して積層された第1の強磁性体層と、第1の電極層の他端上に、第1の絶縁層よりも大きな接合面積を持つ第2の絶縁層を介して積層された第2の強磁性体層と、第1の強磁性体層に接続されている検出電極と、第2の強磁性体層に接続されている第2の電極層とを備え、第1の電極層の幅lbが、第1の絶縁層から第2の絶縁層方向に向かうにつれ大きくなり、かつ第1の絶縁層と第2の絶縁層の間で一定の幅を持つ部分laを備えている。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

磁気センサおよびその製造方法

【課題】コンパクトな構成でありながら磁場の検出性能に優れ、かつ容易に製造可能な磁気センサを提供する。

【解決手段】磁化固着層63と介在層62と磁化自由層61とを順にそれぞれ含むと共に、信号磁場によって互いに反対向きの抵抗変化を示す第1および第2のMR素子を備える。ここで、第1のMR素子における磁化固着層63は、介在層62の側から順にピンド層631と、結合層632と、ピンド層631と反強磁性結合するピンド層633とを含むシンセティック構造を有する。このシンセティック構造は、ピンド層633の総磁気モーメントがピンド層631の総磁気モーメントよりも大きなものである。一方、第2のMR素子における磁化固着層63は、単一もしくは複数の強磁性材料層からなる。

(もっと読む)

磁気抵抗素子及び磁気記憶装置

【課題】高い熱揺らぎ耐性を確保しつつ、スイッチング電流を低減するも、記憶保持特性を向上させ、更なる高速動作化及び高集積化を可能する信頼性の高い磁気抵抗素子及び磁気記憶装置を提供する。

【解決手段】反強磁性層51及び積層フェリー固定層50と、トンネルバリア層2と、非磁性層4を間に挟持した第1の磁性層3と第2の磁性層5とを有する積層磁化自由層11とを有してMTJ10が構成されており、MTJ10は、その周縁において、当該MTJ10の面内磁化容易軸の方向と垂直となる方向に一対の溝10a,10bが形成されている。

(もっと読む)

記憶素子、記憶装置

【課題】スピントルク型磁気メモリにおいて、異方性エネルギーを大きくし、微細化しても十分な熱揺らぎ耐性を有するようにする。

【解決手段】記憶素子は、膜面に対して垂直な磁化を有し、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる、膜面に対して垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とにより、MTJ構造を持つ。これに加え、記憶層に隣接する、Cr、Ru、W、Si、Mnの少なくとも一つからなる保磁力強化層と、保磁力強化層に隣接する酸化物によるスピンバリア層を設ける。

(もっと読む)

1 - 20 / 181

[ Back to top ]