Fターム[5F092AC08]の内容

ホール/MR素子 (37,442) | 素子の種類 (3,422) | 磁気抵抗効果素子(MR素子) (2,873) | 巨大磁気抵抗効果素子(GMR) (891) | スピンバルブ型 (783)

Fターム[5F092AC08]に分類される特許

1 - 20 / 783

磁気記録ヘッドおよびこれを備えた磁気記録装置

磁気抵抗効果素子、および磁気ランダムアクセスメモリ

所定の温度係数を有する抵抗器

記憶素子、記憶装置

【課題】書き込みエラーを生じることなく、短い時間で書き込み動作を行うことができる記憶素子及び記憶装置を提供する。

【解決手段】情報に対応して磁化の向きが変化される記憶層と、磁化の向きが固定された磁化固定層と、上記記憶層と上記磁化固定層との間に配された非磁性体による中間層とを含む層構造を有する記憶素子を構成する。そして上記磁化固定層が、少なくとも2つの強磁性層が結合層を介して積層され、上記2つの強磁性層が上記結合層を介して磁気的に結合し、上記2つの強磁性層の磁化の向きが膜面に垂直な方向から傾斜している。このような構成により、上記記憶層及び上記磁化固定層のそれぞれの磁化の向きがほぼ平行又は反平行とされてしまうことによる磁化反転時間の発散を効果的に抑えることができ、書き込みエラーを低減し、より短い時間で書き込みができる。

(もっと読む)

電力検知センサ

【課題】電力検知を精度良く行う。

【解決手段】磁気抵抗素子11を備えた電力検知センサ10であって、測定対象となる負荷Aに印加される電圧を、磁気抵抗素子11の抵抗成分に基づいて検知し、負荷Aに流れる電流を、磁気抵抗素子11の近傍に配置される電気配線waより発生する磁界に基づく磁気抵抗素子の出力変化、および磁気抵抗素子11の磁気抵抗変化に基づいて検知し、電力検知を行う。

(もっと読む)

電流検知装置、電流検知素子および電流検知方法

【課題】より広い電流レンジの測定を可能とする。

【解決手段】電流を検知するための素子として、磁界の強度に応じて抵抗値が変化する磁気抵抗効果を利用した磁気抵抗素子を用いる。磁気抵抗素子の近傍に配置した配線に測定対象の電流が流れた際に発生する磁界に応じた当該磁気抵抗素子の抵抗に基づき、当該測定対象電流の電流値を測定する。また、磁気抵抗素子を、IV特性の直線領域において純抵抗として用いて、当該磁気抵抗素子に測定対象電流を直接流して電流値の測定を行う。これらの、磁気抵抗素子の磁気抵抗効果を利用した電流測定と、磁気抵抗素子を純抵抗として用いた電流測定とを、測定対象電流の電流値に応じて切り替える。

(もっと読む)

三次元磁界センサおよびその製造方法

【課題】構成が簡単で、製造コストを低減できる三次元磁界センサを実現する。

【解決手段】三次元磁界センサ1は、平面である素子配置面40aを有する基板40と、基板40の素子配置面40a側に配置されて基板40と一体化されたMR素子10,20,30を備えている。MR素子10は、磁化固定層11、非磁性層12および自由層13を有し、MR素子20は、磁化固定層21、非磁性層22および自由層23を有し、MR素子30は、磁化固定層31、非磁性層32および自由層33を有している。自由層13,23,33の磁化の方向は、外部磁界Hの方向に応じて変化する。磁化固定層11の磁化の方向は、素子配置面40aに平行なX方向に固定されている。磁化固定層21の磁化の方向は、素子配置面40aに平行であってX方向に直交するY方向に固定されている。磁化固定層31の磁化の方向は、素子配置面40aに垂直なZ方向に固定されている。

(もっと読む)

電流センサ

【課題】電流値を精度良く検知する。

【解決手段】磁気抵抗素子11を備えた電流センサ10であって、該磁気抵抗素子11の、磁気抵抗素子11自体に流すセンス電流に応じた出力変化(センス電流部12による出力変化)と、磁気抵抗素子の近傍に配置される電気配線(電気配線wd2等の影響による出力変化)への電流に応じた出力変化と、の2つの出力変化に基づいて測定対象である負荷Aへの電流を測定する。

(もっと読む)

磁気メモリの製造装置

【課題】より小さい磁場で磁性層の磁化方向を所定の方向に設定する。

【解決手段】磁気メモリ21の磁場印加装置30は、磁気メモリ21の磁性層に磁場を印加し、磁性層の磁化方向を初期化する磁石32A及び32Bと、磁性層に磁場が印加されている間に、磁気メモリ21の温度を上昇させる温度上昇機構33と、制御回路34とを含む。磁石32A及び32Bはそれぞれ、設定する磁化方向に応じて、磁場を発生し、磁気メモリ21の上から下へ向かう磁場、又は下から上へ向かう磁場が印加される。

(もっと読む)

単一の磁気抵抗センサを使用して磁場の平面方向の磁場コンポーネントを決定するのための装置および方法

【課題】平面に適用された磁場を測定する方法を提供する。

【解決手段】第1の交流ドライブ電流を第1のストラップに適用し、第1のストラップの少なくとも一部が、磁気抵抗センサの上に横たわり、第1のストラップが、第1の方向Xに延びる大きさを有することを特徴とし、第2の交流ドライブ電流を第2のストラップに同時に適用し、第2のストラップの少なくとも一部が第1のストラップの少なくとも一部の上に横たわり、第2のストラップが第2の方向Yに延びる大きさを有し、第2の方向が、第1の方向と並行ではなく、第2の交流ドライブ電流が、第1の交流ドライブ電流と位相が異なり、磁気抵抗センサが、磁気抵抗センサの平面で回転する周期的回転磁気ドライブ磁場に影響を受けることを特徴とする。

(もっと読む)

磁気センサ

【課題】ピン層の磁化方向とフリー層の磁化方向との成す角度に対して検出精度が異なることを簡素な構成で抑制することができると共に、応答速度を向上させることができる磁気センサを提供する。

【解決手段】磁化方向が所定方向に固定されたピン層11および外部磁界に応じて磁化方向が変化するフリー層13を有し、ピン層11の磁化方向とフリー層13の磁化方向との成す角度に応じて抵抗値が変化する第1、第2磁気抵抗素子R1、R2を有する検出部10を備える。そして、第1、第2磁気抵抗素子R1、R2をピン層11の磁化方向が互いに直交する状態で直列接続し、検出部10から第1、第2磁気抵抗素子R1、R2の中点電圧を検出信号として出力する。

(もっと読む)

シザーズ構造を有する磁気抵抗センサの磁気バイアス構造

【課題】 シザーズ構造を有する磁気抵抗センサの磁気バイアス構造を提供する。

【解決手段】 磁気バイアス付与の堅牢性を向上させる新規のハードバイアス構造を有するシザーズ型磁気センサ。当該センサは、電気絶縁障壁層または導電スペーサ層等の非磁性層により分離された第1の磁気層および第2の磁気層を含むセンサスタックを含む。第1の磁気層および第2の磁気層は、逆平行に結合されるが、磁気バイアス構造により、エアベアリング面に対して平行でも垂直でもない方向に傾けられた磁化方向を有する。磁気バイアス構造は、センサスタックの後縁から延在し、センサスタックの第1の側面および第2の側面に整列した第1の側面および第2の側面を有するネック部を含む。バイアス構造はまた、ネック部から後方に延在する先細または楔形部を含む。

(もっと読む)

磁気メモリ及びその製造方法

【課題】低コストで広帯域の読出方式の、磁壁で区切られた磁区毎に情報が記録された磁

性配線を有する磁気メモリを提供する。

【解決手段】磁区、及び前記磁区を仕切る磁壁を有する第1磁性細線と、前記第1磁性細

線の両端部に配置される電流導入用電極と、前記第1磁性配線に隣接して設けられる書き

込み部と、前記第1磁性配線に交差するように設けられる第2磁性細線と、前記第2磁性

配線の一端部に設けられるスピン波発生部と、前記第2磁性配線の他端部に設けられるス

ピン波検出部とを備える。

(もっと読む)

磁気メモリ素子及び磁気メモリ装置

【課題】電流で書き込み動作を行うことができる大容量の磁気メモリ及び磁気メモリ装置を提供する。

【解決手段】磁化が固定された第1の磁性層10と、磁化が可変の第2の磁性層30と、第1の磁性層10と第2の磁性層30との間に設けられた第1の中間層20と、第1の磁性層10と第2の磁性層30とを結ぶ第1の方向に直交する第2の方向に延在し、第2の磁性層30に隣接し、スピン波を伝搬する第1の磁性細線40と、第1の磁性細線40の一端に設けられた第1のスピン波入力部と、第1の磁性細線40の他端に設けられた第1のスピン波検出部と、を備える。

(もっと読む)

磁気メモリ素子

【課題】実施形態による、磁壁制御が容易な磁気メモリ素子を提供する。

【解決手段】磁気メモリ素子100は、第1方向に延在し、磁壁により隔てられた複数の磁区を有する磁性細線20と、前記磁性細線20に対して前記第1の方向又は前記第1の方向と逆方向に通電可能な一対の第1の電極30と、前記第1の方向に直交する第2の方向において、前記磁性細線20上に設けられた第1の絶縁層40と、前記第2の方向であって前記第1の絶縁層40上に離間して設けられた複数の第2の電極50と、複数の前記第2の電極50と電気的に接続された第3の電極60と、を備える。

(もっと読む)

歪検知装置及びその製造方法

【課題】微小領域で歪を高感度に検知することができる歪検知装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体回路部と、半導体回路部の上に設けられた検知部と、を含む歪検知装置が提供される。半導体回路部は、半導体基板上に設けられたトランジスタを有する。検知部は、トランジスタの上方に設けられた空洞部と、空洞部と並置された非空洞部と、を有する。検知部は、可動梁、歪検知素子部、第1、第2埋め込み配線を含む。可動梁は、固定部分及び可動部分を有し、第1、第2配線層を含む。固定部分は非空洞部に固定される。可動部分は、固定部分から空洞部に延びトランジスタと離間する。歪検知素子部は、可動部分に固定され、第1、第2配線層と電気的に接続され、第1磁性層を含む。第1、第2埋め込み配線は、非空洞部に設けられ、第1、第2配線層と半導体回路部とを電気的に接続する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

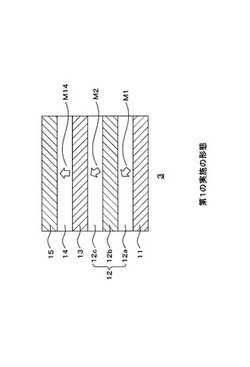

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

不揮発性記憶装置

【課題】安定した動作が可能な不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、磁気記憶素子と制御部とを備えた不揮発性記憶装置が提供される。磁気記憶素子は積層体を含む。積層体は第1積層部と第2積層部とを含む。第1積層部は、磁化が固定された第1強磁性層と、磁化の方向が可変の第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、を含む。第2積層部は、積層方向に沿って第1積層部と積層される。第2積層部は、通電される電流によって磁化が回転して発振が生じる第3強磁性層と、磁化が固定された第4強磁性層と、第3強磁性層と第4強磁性層との間に設けられた第2非磁性層と、を含む。制御部は、第2強磁性層の磁化の向きに応じた第3強磁性層の発振の周波数の変化を検出することで、第2強磁性層の磁化の向きを読み出す読み出し部を含む。

(もっと読む)

磁気記憶素子及び不揮発性記憶装置

【課題】安定した動作が可能な磁気記憶素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、第1、第2積層部を含む磁気記憶素子が提供される。第1積層部は、第1強磁性層/第1非磁性層/第2強磁性層を含む。第1強磁性層の磁化は面直に固定され、第2強磁性層の磁化方向は面直に可変である。第2積層部は、第3強磁性層/第2非磁性層/第4強磁性層を含む。第3強磁性層の磁化方向は面内方向に可変であり、第4強磁性層の磁化は面直に固定されている。第3強磁性層の位置での第1、第2、第4強磁性層からの漏れ磁界Hs、第3強磁性層の磁気異方性Ku、ダンピング定数α、磁化Ms及び反磁界係数Nzは、Ku≦αMs(8πNzMs−Hs)を満たす。電流によりスピン偏極した電子と、第3強磁性層で発生する回転磁界と、を第2強磁性層に作用させ、第2強磁性層の磁化方向を決定できる。

(もっと読む)

1 - 20 / 783

[ Back to top ]