Fターム[5F101BA00]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664)

Fターム[5F101BA00]の下位に属するFターム

Fターム[5F101BA00]に分類される特許

1 - 18 / 18

半導体装置

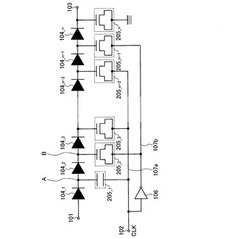

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置及びその製造方法

【課題】放射線耐性能力をさらに向上することができる半導体装置を提供する。

【解決手段】半導体基板1の上方に形成された第1絶縁膜12と、第1絶縁膜12の上方に形成され、下部電極17と上部電極19に挟まれる強誘電体膜18を有するキャパシタQと、キャパシタの上に形成される第2絶縁膜26と、を有し、第1絶縁膜12と下部電極17の間に、Pb又はBiが添加された結晶を持つ絶縁材料膜から形成される第3絶縁膜16、38と、

を有する。

(もっと読む)

3次元垂直チャンネル構造を有する不揮発性メモリ装置のプログラム方法

【課題】本発明は、ビットラインとストリング選択ラインとの交差領域に各々形成され、各々が基板上に垂直に多層構造で形成されたメモリセルを有するストリングを含む不揮発性メモリ装置のプログラム方法を提供する。

【解決手段】本発明のプログラム方法によると、シャドープログラム方式によってYZ平面の各層に属したメモリセルがマルチビットデータにプログラムされ、YZ平面のN番目の層(ここで、Nは1、またはそれより大きい定数)のメモリセルがプログラムされる場合、YZ平面の他層のメモリセルがプログラムされる前にN番目の層に対応するXZ平面の残りのメモリセルがプログラムされる。

(もっと読む)

半導体装置及び該半導体装置のレイアウト方法

【課題】半導体装置及び該半導体装置のレイアウト方法を提供する。

【解決手段】複数のビットラインパターンと、複数のビットラインパターンにそれぞれ連結されて形成される複数のパッドパターンと、パッドパターンに形成される少なくとも一つのコンタクトと、を備え、パッドパターンのピッチは、ビットラインパターンのピッチより長い半導体装置とする。

(もっと読む)

半導体素子の製造方法および半導体素子

【課題】 半導体素子の微細パターン製造方法を提供する。

【解決手段】フィーチャー層310の第1領域Aには第1マスク構造物を形成し、第2領域Bには第2マスク構造物を形成する。各々デュアルマスク層とエッチングマスク層とを含むように第1マスク構造物及び第2マスク構造物を形成する。第1マスク構造物及び第2マスク構造物のエッチングマスクパターンを等方性エッチングし、第1マスク構造物からエッチングマスクパターンを除去する。第1マスク構造物及び第2マスク構造物の両側壁にスペーサ350A、350Bを形成する。第2マスク構造物上にあるエッチングマスクパターンをマスクとして第1領域Aで間にボイドが形成されるように側壁スペーサ350Aを含む第1マスクパターンと、第2領域Bで間に第2マスク構造物が介在するように側壁スペーサ350B、350Cを含む第2マスクパターンを形成する。

(もっと読む)

酸化ゲルマニウムの製造方法およびそれを用いた半導体デバイスの製造方法

【課題】熱的および化学的に安定な酸化ゲルマニウムの製造方法を提供する。

【解決手段】p型Geからなる基板1は、純水および0.1%HFによって洗浄され、その後、超純水によってリンスされる(工程(a)参照)。その後、基板1は、33%の過酸化水素水3に、60秒間、浸漬される(工程(b)参照)。これによって、酸化ゲルマニウム膜4が基板1の一主面に形成される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置を製造する際、側壁加工プロセスで形成される不要な配線を介したショートの発生を防ぎ、マイクロローディング効果やディッシング現象の発生を防ぐ。

【解決手段】基板上に被加工絶縁性膜を形成し、前記基板に設けられる素子を接続する第1の配線が配置される第1のエリアに前記第1の配線を形成するためにパターニングされた第1の犠牲膜を形成し、ダミー配線が配置される第2のエリアに前記ダミー配線を形成するためにパターニングされた第2の犠牲膜を形成し、前記第1の犠牲膜の側壁に形成される第3の犠牲膜と前記第2の犠牲膜の側壁に形成される第4の犠牲膜とを、分離した膜として形成し、前記第3の犠牲膜と前記第4の犠牲膜とをマスクとして前記被加工絶縁性膜をエッチングして凹部を形成し、導電性材料を前記凹部に埋め込むことを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

不揮発性メモリ装置及びその動作方法

【課題】不揮発性メモリ装置及びその動作方法を提供する。

【解決手段】積層された複数の半導体層と、複数の半導体層上にそれぞれ形成され、NAND構造で配置された複数のメモリセル及び一つ以上のストリング選択トランジスタをそれぞれ含む複数のNANDストリングと、複数のメモリセルの一側の複数のNANDストリングに共通接続された共通ビットラインと、複数のメモリセルの他側の複数のNANDストリングに共通接続された共通ソースラインと、複数のNANDストリングのそれぞれの複数のメモリセルに結合された複数のワードラインと、共通ビットラインに印加された信号が複数のNANDストリングに選択的に印加されるように、複数のNANDストリングのそれぞれの一つ以上のストリング選択トランジスタにそれぞれ結合された複数のストリング選択ラインと、を備える不揮発性メモリ装置である。

(もっと読む)

半導体装置の製造方法

【課題】素子分離絶縁膜の表面の平坦度を向上させることができる半導体装置の製造方法を提供する。

【解決手段】シリコン酸化膜11及びシリコン窒化膜12をハードマスクとして用いながら、半導体基板51のエッチングを行うことにより、溝13及び溝14を形成する。溝13及び14を埋め込むようにシリコン酸化膜を高密度プラズマCVD法により形成する。溝13上に開口部を備えたレジストパターンをシリコン酸化膜上に形成する。レジストパターンをマスクとして用いながら、窒素イオンをシリコン酸化膜の表面に注入する。レジストパターンし、窒素雰囲気中でアニールを行うことにより、シリコン酸化膜の窒素イオンが導入された部分にシリコン酸窒化膜を形成する。700℃〜900℃程度のアンモニア雰囲気中でアニールを行うことにより、シリコン酸化膜のうちで、シリコン酸化膜11の表面より上方に位置する部分をシリコン窒化膜18に変化させる。

(もっと読む)

不揮発性メモリ装置のソフトプログラム方法

【課題】消去されたセルのしきい値電圧分布を改善させるためにソフトプログラム段階を行う不揮発性メモリ装置のソフトプログラム方法を提供する。

【解決手段】不揮発性メモリ装置のソフトプログラム方法は、消去動作が実施されたメモリセルのしきい値電圧を一定レベルに上昇させるソフトプログラム段階と、各セルストリング別にしきい値電圧以上にプログラムされたセルがあるかを判断する検証段階と、上記検証結果、全体のセルストリングがしきい値電圧以上にプログラムされたセルを一つ以上含むまで上記ソフトプログラムを反復する段階を含む。

(もっと読む)

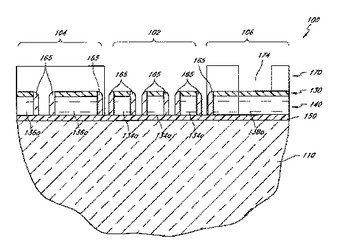

効率的なピッチマルチプリケーションプロセス

集積回路(100)の、ピッチマルチプリケーションされたフィーチャと、ピッチマルチプリケーションされていないフィーチャ、例えば、それぞれ集積回路(100)の、アレイ領域(102)、インターフェース領域(104)、および周辺領域(106)内のフィーチャが、マスクを通して基板(110)を処理することによって形成される。マスクは、フォトレジスト層をパターニングすることによって形成され、これは同時に、それぞれ集積回路(100)のアレイ領域(102)、インターフェース領域(104)、および周辺領域(106)内のフィーチャに対応するマスク要素を画定する。パターンは非晶質炭素層(140)に転写される。側壁スペーサー(165)が、パターニングされた非晶質炭素層(140)の側壁に形成される。保護材料の層(170)が堆積され、その後パターニングされ、アレイ領域(102)内、およびインターフェース領域(104)もしくは周辺領域(106)の選択部分内のマスク要素を露出する。アレイ領域内の非晶質炭素、もしくは他の露出された部分は除去され、その結果、アレイ領域(102)内にピッチマルチプリケーションされた自立スペーサー(165)を含むパターンを残す。保護材料(170)は除去され、アレイ領域(102)内のピッチマルチプリケーションされたスペーサーと、インターフェース領域(104)および周辺領域(106)内のピッチマルチプリケーションされていないマスク要素のパターンを残す。パターンはハードマスク層(150)に転写され、それを通して下にある基板(110)がエッチングされる。  (もっと読む)

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】コンタクトホールのサイズの安定した減少を実現でき、素子の信頼性を向上させるフラッシュメモリ素子の製造方法を提供する。

【解決手段】半導体基板101上に層間絶縁膜105とハードマスク膜パターン106aを形成し、それらの表面を覆うようにしてスペーサ膜109を形成する。第1のエッチング工程で層間絶縁膜105にコンタクトホール(図4中の符号200)を形成し、スペーサ膜109も第1のエッチング工程にて除去し、ハードマスク膜パターン106aを除去するための第2のエッチング工程を実施する。それにより、コンタクトホールのサイズを減少させる必要がある場合、あるいは隣り合うコンタクトホールどうしの間隔スペースを減少させる必要がある工程にあって、リソグラフィ工程の限界を克服しつつ、コンタクトホールのサイズを安定して減少させ、ブリッジの発生を抑えて素子の信頼性を高める。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】四角形のドレインコンタクトホールを形成することにより、コンタクトとコンタクトとの間に発生するブリッジの発生を抑制できるフラッシュメモリ素子の製造方法を提供する。

【解決手段】半導体基板にエッチング防止膜102、第1及び第2層間絶縁膜104,106、第1、第2及び第3ハードマスク膜108,110,112を順次形成する。第3ハードマスク膜をエッチングして第2ハードマスク膜の一部領域を露出し、この露出領域よりさらに狭く露出するフォトレジストパターンを形成し、これをマスクとして第2、第1ハードマスク膜をエッチングした後、残留する第3及び第2ハードマスク膜をマスクとして第2、第1層間絶縁膜をエッチングして四角形のホールを形成する。残留する第2及び第1ハードマスク膜をマスクとしてエッチング防止膜をエッチングし、基板を露出させてドレインコンタクトホールを形成する。

(もっと読む)

フラッシュメモリ素子およびその製造方法

【課題】半導体素子の信頼性を向上させ、かつ集積度を向上させるフラッシュメモリ素子およびその製造方法を提供する。

【解決手段】メモリセル領域Aとペリ領域Cとの境界部分にゲートライン12が通るか否かによって、ゲートライン12が通る場合には、その境界部分を素子分離膜11aで構成し、ゲートライン12が通らない場合には、ダミーアクティブ(dummy active)で構成することにより素子の信頼性を改善し、ウェルピックアップ(well pick up)領域を上記ダミーアクティブ内に構成することで集積度を向上させる。

(もっと読む)

半導体素子の素子分離膜形成方法

【課題】素子分離膜形成工程で発生するプラズマ損傷Wを防止する半導体素子の素子分離膜形成方法を提供。

【解決手段】半導体素子の素子分離膜形成方法は、半導体基板上のパッド膜および半導体基板10の所定の深さをパターニングしてトレンチを形成する段階と、前記トレンチの側壁に側壁酸化膜18を形成する段階と、全面に第1トレンチ埋め込み用酸化膜を形成し、前記パッド膜が露出するまで平坦化工程を行い、非活性領域が定義される第1素子分離膜20を形成する段階と、前記パッド膜を除去し、活性領域を定義する前記半導体基板10を露出させる段階と、前記半導体基板10上に前記第1素子分離膜20の高さより高くシリコン層を形成する段階と、全面に第2トレンチ埋め込み用酸化膜を形成し、前記シリコン層が露出するまで平坦化工程を行って第2素子分離膜23を形成することにより、積層された素子分離膜を形成する段階とを含む。

(もっと読む)

メモリ領域とロジック領域を混載する半導体装置の製造方法

【課題】 メモリ領域とロジック領域でのSTIの突き出し量のバラツキを低減するのと共に、ゲート写真製版のフォーカスマージンを向上し得る半導体装置の製造方法を得ることを目的とする。

【解決手段】 素子分離としてのSTI形成後の半導体基板において、メモリ領域のメモリセル部に対するチャネルドープ工程をゲート酸化前に行い、所定の不純物注入完了後にレジスト付きの状態にてフッ酸含有の溶液によりSTI段差を調整するためウエットエッチングを行い、メモリ領域とロジック領域のSTI突き出し量の差が同程度になるようにした。

(もっと読む)

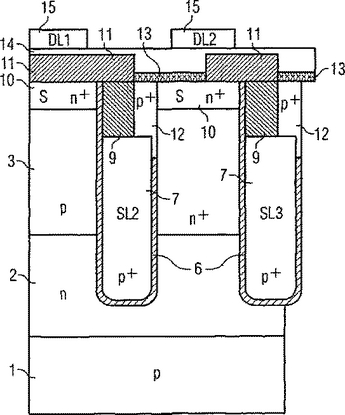

ビット線構造およびその製造方法

本発明は、表面ビット線(DLx)および埋め込みビット線(SLx)を備えたビット線構造に関するものである。これに関して、埋め込みビット線(SLx)は、トレンチ絶縁層(6)を備えたトレンチに形成されており、トレンチの上部に設けられた被覆接続層(12)と自動調心電極層(13)とを介して形成された接触部とともに、ドープ領域(10)に接続されている。  (もっと読む)

(もっと読む)

パッド下に素子を備える手法によるウェハの有効利用

半導体構造(20)のパッドエリア(21)下に能動素子(25)を組み込むことにより、シリコンエリアのより効率的な利用を可能とする。パッドエリア(21)は、上方に第1の金属層(23)を備えた基板(22)を含む。第2の金属層(26)は第1の金属層(23)の下とする。能動素子(25)は基板内であって、第2の金属層(26)の下に備えられる。誘導体層(24)は第1の金属層(26)と第2の金属層(23)とを分離する。誘導体層(24)内のビア(27)は第1の金属層(23)と第2の金属層(26)とを電気的に接続する。ビア(27)は能動素子(25)と接続する。隣接金属層(424、425、426)を第1の金属層(23)と第2の金属層(26)の間に配置してもよい。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]