Fターム[5F101BA12]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG形状構造 (858)

Fターム[5F101BA12]の下位に属するFターム

埋め込みFG、溝 (45)

CG側壁 (37)

FGの突起 (84)

複数FG(単一メモリセル内) (90)

FG接続 (271)

PN接合(FG内の) (5)

Fターム[5F101BA12]に分類される特許

1 - 20 / 326

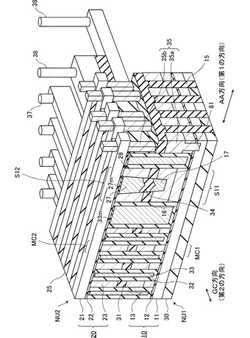

不揮発性半導体記憶装置及びその製造方法

【課題】制御性の高い不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第1の絶縁層の上に形成された第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1の絶縁層を介して上下に位置する第1及び第2の選択ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第2の方向に延び、第1及び第2の半導体層並びに第1及び第2のゲート絶縁層と共に補助トランジスタを形成する補助ゲートとを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造の容易な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセルアレイ層と、第1のメモリセルアレイ層の上に形成された第1の絶縁層と、第2のメモリセルを具備する第2のNANDセルユニットを有する第2のメモリセルアレイ層と、第1の絶縁層を介して上下に位置する第1及び第2の浮遊ゲートの第1の方向の両側面にゲート間絶縁層を介して形成され、第1の方向と直交する第2の方向に延びる制御ゲートと、第1のNANDセルユニットの両端に位置し、第1の浮遊ゲートと同層に形成され、第1の半導体層と接続される下部コンタクトと、第2のNANDセルユニットの両端に位置し、第2の半導体層と下部コンタクトとを接続する上部コンタクトとを備える。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、半導体層として機能する酸化物半導体膜と、酸化物半導体膜上のシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有し、少なくともゲート電極と重畳する酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%以下の濃度で分布する領域を有する構造とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離絶縁膜の形成時に、浮遊ゲート電極膜の基板に対面する部分の幅寸法が細くなってしまうことを防止する。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、浮遊ゲート電極膜、電極間絶縁膜および制御ゲート電極膜が積層されたゲート電極とを備えた。そして、前記浮遊ゲート電極膜を、窒素を含む下層シリコン層と窒素を実質的に含まない上層シリコン層とを有する多結晶シリコン層で構成し、前記下層シリコン層のゲート幅方向の寸法を、前記上層シリコン層のゲート幅方向の寸法よりも大きく構成した。

(もっと読む)

不揮発性半導体記憶装置

【課題】カップリング比の増大と書き込み/消去時のリーク電流の低減とを実現する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、半導体層11と、半導体層11上の第1の絶縁層13と、第1の絶縁層13上の電荷蓄積層14と、電荷蓄積層14上の第2の絶縁層15と、第2の絶縁層15上の制御ゲート電極16とを備える。第2の絶縁層15は、電荷蓄積層14側から制御ゲート電極16側に向かって、第1のランタンアルミネート層LAO、ランタンアルミシリケート層LASO及び第2のランタンアルミネート層LAOを備える。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】短チャネル効果が抑制され、微細化を実現しつつ、安定した電気的特性を付与する半導体装置を提供する。また、上記半導体装置を作製する。

【解決手段】酸化物絶縁層に設けたトレンチに、トレンチに沿って成膜される酸化物半導体膜と、酸化物半導体膜と接するソース電極及びドレイン電極と、酸化物半導体膜上のゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有する半導体装置(トランジスタ)を設ける。該トレンチは下端コーナ部に曲面を有し、側部が酸化物絶縁層上面に対して略垂直な側面を有する。また、トレンチの上端の幅がトレンチの側面の幅の1倍以上1.5倍以下である。

(もっと読む)

半導体メモリ装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線の一端にバックゲートを有するトランジスタ(バックゲートトランジスタ)を直列に挿入し、そのバックゲートの電位は常に十分な負の値となるようにする。また、ビット線の最低電位はワード線の最低電位よりも高くなるようにする。電源が切れた際には、ビット線はバックゲートトランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。

(もっと読む)

半導体装置

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

半導体装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースおよび読み出しトランジスタのソースをビット線に、読み出しトランジスタのドレインを読み出しワード線に接続する。ここで、書き込みトランジスタと読み出しトランジスタの導電型を異なるものとする。集積度を高めるために、バイアス線を他行の読み出しワード線で代用したり、記憶セルを直列に接続し、NAND構造とし、読み出しワード線と書き込みワード線を共用してもよい。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶

縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに

、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半

導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された

酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳す

る領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

記憶回路、信号処理回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】酸化物半導体を用いて形成されたトランジスタと、該トランジスタのソース電極またはドレイン電極の一方と接続された容量素子を用いて、不揮発性の記憶回路を構成する。記憶回路に予めハイレベル電位を書き込んでおき、退避させるデータがハイレベル電位の場合は、そのままの状態を維持し、退避させるデータがローレベル電位の場合は、ローレベル電位を記憶回路に書き込むことで、書き込み速度を向上させた信号処理回路を実現できる。

(もっと読む)

半導体装置

【課題】半導体装置を小型化する。また、メモリセルを有する半導体装置の駆動回路の面積を縮小する。

【解決手段】少なくとも第1の半導体素子を有する素子形成層と、素子形成層上に設けられた第1の配線と、第1の配線上に設けられた層間膜と、層間膜を介して第1の配線と重畳する第2の配線と、を有し、第1の配線と、層間膜と、第2の配線と、は、第2の半導体素子を構成し、第1の配線と、第2の配線と、は、同電位が供給される配線である半導体装置である。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】記憶回路におけるデータの保持期間を長くする。また、消費電力を低減する。また、回路面積を小さくする。また、1回のデータの書き込みに対する該データの読み出し可能回数を増やす。

【解決手段】記憶回路を具備し、記憶回路は、ソース及びドレインの一方にデータ信号が入力される第1の電界効果トランジスタと、ゲートが第1の電界効果トランジスタのソース及びドレインの他方に電気的に接続される第2の電界効果トランジスタと、ソース及びドレインの一方が第2の電界効果トランジスタのソース又はドレインに電気的に接続される第3の電界効果トランジスタと、を備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料を用いたトランジスタと、第1の半導体材料とは異なる第2の半導体材料を用いたトランジスタと、容量素子とを有する複数のメモリセルを有し、書き込み期間にソース線に電源電位を供給する機能を有する電位切り替え回路を備えた半導体装置とする。これにより、半導体装置の消費電力を十分に抑えることができる。

(もっと読む)

ゲインセル型半導体メモリ装置およびその駆動方法

【課題】ゲインセルとして知られている2つのトランジスタと1つのキャパシタよりなるメモリセルを改良する。

【解決手段】キャパシタの一方の電極をビット線に接続し、他方の電極を書き込みトランジスタのドレインに接続する。また、書き込みトランジスタのソースは、ソース線に接続される。この結果、例えば、キャパシタとしてスタック型キャパシタを採用する場合には、キャパシタの電極の一方をビット線の一部とすることができる。ソース線の電位と書き込みビット線の電位を設定することで、特定の書き込みトランジスタのみをオンとし、1つのメモリセルだけを書き換えることもできる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】選択ゲート電極が浮遊ゲート電極の横に位置している不揮発型記憶素子において、浮遊ゲート電極と半導体基板の間の容量に対する、制御ゲート電極と浮遊ゲート電極の間の容量の比を大きくする。

【解決手段】平面視において、制御ゲート電極130のうち選択ゲート電極170側の端部は、浮遊ゲート電極120の外側に位置した拡張部133となっている。拡張部133の下端は、浮遊ゲート電極120の上面よりも半導体基板100の近くに位置している。また拡張部133と浮遊ゲート電極120の間にも第1絶縁膜132が形成されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または

、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶

縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と

、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁

層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)

粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層

表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】トランジスタの作製工程において、酸化物半導体層、ソース電極層、ドレイン電極層、ゲート絶縁膜、ゲート電極層、酸化アルミニウム膜を順に作成した後、酸化物半導体層および酸化アルミニウム膜に対して熱処理を行うことで、水素原子を含む不純物が除去され、かつ、化学量論比を超える酸素を含む領域を有する酸化物半導体層を形成する。また、酸化アルミニウム膜を形成することにより、該トランジスタを有する半導体装置や電子機器の作製工程での熱処理でも大気から水や水素が酸化物半導体層に侵入し、拡散することを防止することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

1 - 20 / 326

[ Back to top ]