Fターム[5F101BA36]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG周囲絶縁膜 (3,604) | 薄膜化又は絶縁膜材料の特徴部位 (1,645) | CGとFG間 (1,254)

Fターム[5F101BA36]に分類される特許

1 - 20 / 1,254

半導体装置及びその製造方法

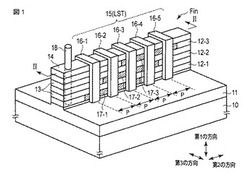

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供すること。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

(もっと読む)

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】パンチスルーを抑制しつつ、セレクトゲート電極からのフリンジ電界を低減する。

【解決手段】空隙AG1は、制御ゲート電極8およびセレクトゲート電極12下に潜るようにしてトレンチ2に沿って連続して形成され、セレクトゲートトランジスタのドレイン領域間に達している。そして、セレクトゲートトランジスタのドレイン領域間において、空隙AG1が埋め戻し絶縁膜RBにて埋め戻されている。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、半導体層として機能する酸化物半導体膜と、酸化物半導体膜上のシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有し、少なくともゲート電極と重畳する酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%以下の濃度で分布する領域を有する構造とする。

(もっと読む)

半導体装置、メモリカード、データ処理システムおよび半導体装置の製造方法

【課題】歩留まりや信頼性の低下を招くことなく、隣接セルのフローティング・ゲート間の結合容量を小さくすることができ、隣接セルの書き込み情報の影響を小さくした状態でフローティング・ゲートの電位を制御することが可能なNAND型フラッシュメモリを提供する。

【解決手段】一導電型の半導体材料層表面のチャネル領域上方に第2の絶縁膜12を介して形成されたゲート電極部と、ゲート電極部の上方に前記ゲート電極部と一体形成されたキャパシタ電極部と含むフローティング・ゲート13と、キャパシタ電極部の側面を囲むように第1の絶縁膜12を介して形成されたコントロールゲート10となる第1の電極と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】デバイス特性の向上を図る。

【解決手段】本実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法においては、半導体層10上に、トンネル絶縁膜11を形成する。トンネル絶縁膜上に、浮遊ゲート電極となる第1導電膜12を形成する。第1導電膜、トンネル絶縁膜、および半導体層を加工することにより、溝15を形成する。溝内の下部側に、第1犠牲膜17を埋め込む。溝内の第1犠牲膜上に、その上面がトンネル絶縁膜の上面よりも高く、第1導電膜の上面よりも低くなるように、第1犠牲膜よりも高密度な第2犠牲膜18を形成する。第1導電膜上および第2犠牲膜上に、絶縁膜19を形成する。絶縁膜上に制御ゲート電極となる第2導電膜WLを形成する。第2導電膜を加工することにより、第2犠牲膜を露出する。第1犠牲膜および第2犠牲膜を除去する。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

不揮発性メモリ装置の製造方法

【課題】不揮発性メモリ装置の製造方法を提供する。

【解決手段】基板10上に第1絶縁膜11及び第1導電膜12を形成するステップと、第1領域Cの第1導電膜12、第1絶縁膜11及び基板10をエッチングして、第1素子分離トレンチを形成するステップと、第1素子分離トレンチに埋め立てられる第1素子分離膜を形成するステップと、第2絶縁膜16及び導電性のキャップ膜17を形成するステップと、第2領域Pのキャップ膜17及び第2絶縁膜16をエッチングするステップと、第2導電膜19を形成するステップと、第1領域Cの第2導電膜19、キャップ膜17、第2絶縁膜16、第1導電膜12及び第1絶縁膜11を選択的にエッチングして、第1ゲートパターンを形成しながら、第2領域Pの第2導電膜19、第1導電膜12、第1絶縁膜11及び基板10を選択的にエッチングして、第2領域Pに第2素子分離トレンチT2、T3を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

酸化膜の形成方法

【課題】シリコン表面のプラズマ酸化により、界面準位密度が低くリーク電流の少ない高品質な酸化膜をシリコン表面上に形成する。

【解決手段】

酸化膜の形成方法は、KrとO2の混合ガス中にプラズマを形成することにより原子状酸素O*を発生させ、前記原子状酸素O*によりシリコン表面をプラズマ酸化するプラズマ酸化工程を含み、前記プラズマ酸化工程は、800〜1200mTorrの圧力範囲において実行される。

(もっと読む)

半導体装置の製造方法

【課題】

実施形態は、ゲート配線の抵抗が増大することを防止可能な半導体装置の製造方法を提供する。

【解決手段】

本実施形態の半導体装置の製造方法は、第1領域及び第2領域の半導体素子を形成するために、半導体基板、前記半導体基板上の第1絶縁膜、前記第1絶縁膜上の電荷蓄積層を積層し、所望のトレンチを形成する工程と、前記トレンチに素子分離膜を形成する工程と、前記素子分離膜及び前記電荷蓄積層上にストッパー膜30を形成する工程と、前記第2領域を第2絶縁膜で被膜し、前記第1領域の前記ストッパー膜30と前記素子分離膜をエッチバックする工程と、前記エッチバックされた素子分離膜、前記電荷蓄積層、第2領域の前記ストッパー膜30上に第3絶縁膜を介して配線を形成する工程とを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】注入した導電性不純物により形成される結晶欠陥の密度を低減し、歩留まり率が向上するような半導体装置の製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板を加熱することにより、半導体基板の基板温度を200から500℃の間の所望の温度に維持すると同時に、半導体基板に導電性不純物をイオン注入法もしくはプラズマドーピング法を用いてドーピングし、ドーピングした導電性不純物を活性化させるための活性化処理を行う。

(もっと読む)

1 - 20 / 1,254

[ Back to top ]