Fターム[5F101BA41]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039)

Fターム[5F101BA41]の下位に属するFターム

Fターム[5F101BA41]に分類される特許

1 - 20 / 64

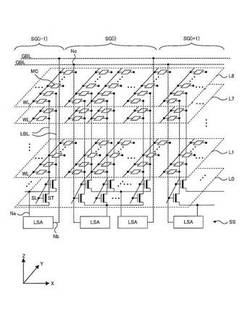

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】積層構造物の傾きまたは崩壊を防止するのに適する半導体装置及びその製造方法を提供する。

【解決手段】パイプゲート内に埋め込まれたパイプチャンネル及びパイプチャンネルと繋がれた一対のドレインサイドチャンネル、及びソースサイドチャンネルを含むチャンネルを含むメモリブロックと、隣合うメモリブロックの間に位置された第1スリットと、一対のソースサイドチャンネルとドレインサイドチャンネルの間に位置された第2スリットと、を含む。

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

3次元不揮発性メモリ素子及びその製造方法

【課題】エンハンスドモード(Enhanced Mode)で駆動される3次元不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】第1パイプゲート、前記第1パイプゲート上に形成された第2パイプゲートおよび前記第1パイプゲートと前記第2パイプゲートとの間に介在され、第1層間絶縁膜を含むパイプゲートと、前記パイプゲート上に交互に積層された複数のワードラインおよび複数の第2層間絶縁膜と、前記パイプゲート内に埋め込まれたパイプチャンネルと、前記パイプチャンネルに連結されながら前記複数のワードラインおよび前記複数の第2層間絶縁膜を貫通する複数のメモリセルチャンネルと、を含むことを特徴とする3次元不揮発性メモリ素子。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 ダイオードとトランジスタとを直列接続した半導体メモリにおいて、ダイオードからトランジスタにキャリアが入ることで、トランジスタの特性が劣化する課題がある。

【解決手段】 半導体記憶装置において、ダイオード(PD)中のキャリアを生成するダイオード半導体層(40p)と、トランジスタのチャネル層(8p)との間に、当該キャリアを対消滅させる構造(61pと62p等)を有する。

(もっと読む)

半導体集積回路

【課題】 不揮発記憶保持用途の電界効果トランジスタと、論理演算用途の電界効果トランジスタの製造工程を別々に設けることなく前記2用途の電界効果トランジスタを同一半導体基板上に同一構造に作製できるようにする。

【解決手段】 ゲート絶縁構造体12に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタで半導体集積回路のメモリ回路とロジック回路の両方を構成し、ゲート絶縁構造体に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタのゲート-基板領域間に印加する電圧の大きさと印加タイミングを制御することによって、論理演算状態と記憶書込み状態と不揮発記憶保持状態を電気的に切り替える。

(もっと読む)

不揮発性半導体記憶装置

【課題】より安定した動作を実現する一括加工型3次元積層型の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、メモリ部MUと、メモリ部に併設された非メモリ部PUと、を備えた不揮発性半導体記憶装置が提供される。メモリ部は、積層された複数の電極膜61と、複数の電極膜どうしの間に設けられた電極間絶縁膜62と、を含む積層構造体MLと、積層構造体と積層された選択ゲート電極SGと、積層構造体及び選択ゲート電極を貫通する半導体ピラーSPと、電極膜と半導体ピラーとの間に設けられた記憶層48と、を含む。非メモリ部は、複数の電極膜の少なくとも1つと同層の部分を含むダミー導電膜65と、選択ゲート電極と同層のダミー選択ゲート電極SGdと、ダミー導電膜に接続されたコンタクト電極と、ダミー選択ゲート電極に接続されたコンタクト電極と、を含む。

(もっと読む)

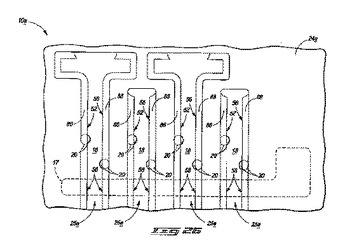

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

3次元半導体装置の配線構造体

【課題】集積度及び信頼性を共に向上させた3次元半導体装置を提供する。

【解決手段】3次元半導体装置の配線構造が提供される。3次元半導体装置は3次元基板上に2次元的に配列された積層構造体、第1配線を含み、積層構造体の上部に配置される第1配線層及び第2配線を含み、第1配線層の上部に配置される第2配線層を含み、積層構造体各々は順次に積層された複数の下部ワードラインを含む下部構造体及び順次に積層された複数の上部ワードラインを含み、下部構造体の上部に配置される上部構造体を含み、第1配線各々は下部ワードラインの内の何れか1つに連結し、第2配線各々は上部ワードラインの内の何れか1つに連結する。

(もっと読む)

半導体装置の製造方法

【課題】パターン不良を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】被加工膜上に、ラインアンドスペース部と前記ラインアンドスペース部の外側に形成された第一のパターンとを有する第二のパターンを形成し、側壁パターンを前記第二のパターンの側壁に形成し、前記第一のパターンの側壁のうち、前記ラインアンドスペース部と反対側の側壁に形成された側壁パターンを除去し、前記第一のパターンの側壁のうち、前記ラインアンドスペース部と対向する側の側壁に形成された側壁パターンに基づき、回路パターンを形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高速なアクセスが可能で、かつ、高集積化が可能なスプリットゲート型不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板101の主表面の溝に第1、第2のスプリット型不揮発性メモリセルを形成した不揮発性半導体記憶装置100であって、溝内部の対向する第1、第2の側壁102a,102bの表面にそれぞれ第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とが形成され、第1、第2のスプリット型不揮発性メモリセルの選択ゲート121とコントロールゲート122とには、それぞれ異なる電圧を印加することが可能である。

(もっと読む)

3次元半導体メモリ装置及びその製造方法

【課題】3次元半導体メモリ装置及びその製造方法を提供する。

【解決手段】本装置は、積層された導電パターン、導電パターンを貫通する活性パターン及び導電パターンと活性パターンとの間に介在される情報貯蔵膜を含む少なくとも1つのメモリ構造体を含み、活性パターンは積層された下部及び上部貫通ホールを各々満たす下部及び上部半導体パターンを含むことができる。1つのメモリ構造体を構成する情報貯蔵膜は同一の工程段階を利用して実質的に同時に形成され、1つのメモリ構造体を構成する下部及び上部貫通ホールは互いに異なる工程段階を利用して順に形成され得る。

(もっと読む)

半導体メモリー装置のチャンネルをプリチャージする方法

【課題】プログラムディスターバンスが効果的に遮断されて高いデータ信頼性を有する3次元半導体メモリー装置のチャンネルをプリチャージする方法を提供する。

【解決手段】本発明による半導体メモリー装置のプログラム方法は、複数のビットラインの中でプログラムビットラインに連結される少なくとも1つのインヒビットストリングのチャンネルと、インヒビットビットラインに連結されるインヒビットストリングの中で少なくとも何れか1つのチャンネルとを共通ソースラインに供給されるプリチャージ電圧に充電する段階と、ワードライン電圧を複数のセルストリングに供給してプリチャージされたチャンネルをブースティングさせる段階と、を有する。

(もっと読む)

集積回路の製造において複数の導電線を形成する方法、導電線アレイを形成する方法、および集積回路

集積回路の製造において導電線対を形成する方法は、基板上に受けられるダマシン材料にトレンチを形成することを含み、導電性材料34a/35aが、そのダマシン材料を覆ってそしてトレンチ内へ蒸着されてそのトレンチを過充填する。その導電性材料は、少なくともダマシン材料へと戻すように除去されて、そのトレンチ内に残っている導電性材料の少なくともいくらかが残される。エッチングがトレンチ内で導電性材料を通って縦方向に処理されて、トレンチ内に少なくとも第1および第2の導電線の長さの大部分に沿って横断面図において互いにミラー像となる第1および第2の導電線が形成される。他の装いが考えられる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】メモリセルにMONOS構造が用いられる場合においても、メモリセル領域にバーズビークが形成されるのを防止しつつ、選択トランジスタのゲート絶縁膜の電界を緩和する。

【解決手段】メモリセルアレイ1にマトリクス状に配置されたメモリセルMCのチャージトラップ膜として、シリコン窒化膜を用いた上で、メモリセルMCとともにNANDセルMSに含まれる選択トランジスタSG1、SG2のゲート絶縁膜として、シリコン酸窒化膜を用いる。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

垂直NANDチャンネルとこれを含む不揮発性メモリー装置、及び垂直NANDメモリー装置

【課題】高集積化され、動作速度が速い垂直NANDチャンネルとこれを含む不揮発性メモリー装置、及び垂直NANDメモリー装置を提供する。

【解決手段】本発明の不揮発性メモリー装置は、単一の上部選択ゲートライン又は単一の下部選択ゲートラインに電気的に結合された複数の直に隣接するオフセット垂直NANDチャンネルを有する。

(もっと読む)

1 - 20 / 64

[ Back to top ]