Fターム[5F101BA61]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | その他記憶作用 (122)

Fターム[5F101BA61]の下位に属するFターム

強誘電体 (98)

非晶質 (1)

電子ガス、ヘテロ接合 (1)

半絶縁性材料 (2)

超格子

磁性体 (5)

Fターム[5F101BA61]に分類される特許

1 - 15 / 15

不揮発性記憶装置

【課題】プロセス耐性が高く、高い性能を維持する不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、第1導電部と、第2導電部と、記憶層と、を含む不揮発性記憶装置が提供される。前記記憶層は、前記第1導電部と前記第2導電部との間に設けられる。前記記憶層は、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能である。前記記憶層は、カルコパイライト構造を有する。

(もっと読む)

情報記録再生装置

【課題】高記録密度及び低消費電力の情報記録再生装置を提案する。

【解決手段】実施形態に係わる情報記録再生装置は、記録層12と、記録層12に電圧を印加して記録層12に相変化を発生させて情報を記録する記録回路とを備える。記録層12は、少なくとも1種類の陽イオン元素と少なくとも1種類の陰イオン元素を有する化合物から構成され、陽イオン元素の少なくとも1種類は、電子が不完全に満たされたd軌道を有する遷移元素であり、隣接する陽イオン元素間の平均最短距離は、0.32nm以下である。記録層12は、(i) AxMyX4 (0≦x≦2.2、1.8≦y≦3)、(ii) AxMyX3 (0≦x≦1.1、0.9≦y≦3)及び(iii) AxMyX4 (0≦x≦1.1、0.9≦y≦3)のうちから選択される材料を備える。

(もっと読む)

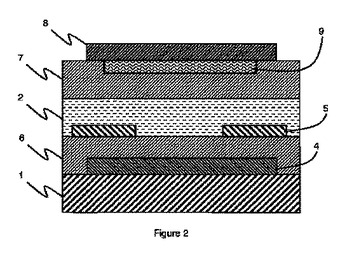

有機デュアルゲートメモリおよびその製造方法

有機メモリデバイスは、第1のゲート電極(4)と、第1のゲート誘電体(6)と、有機半導体材料(2)と、第2のゲート誘電体(7)と、第2のゲート電極(8)とを備えるデュアルゲートトランジスタである。ソース・ドレイン電極(5)が、有機半導体材料(2)中に配置されるとともに、電極間表面を規定する。捕捉領域(9)が、有機半導体材料(2)とゲート電極(4,8)のうちの一方との間に配置されるとともに、ゲート電極(4,8)のうちの一方または有機半導体材料(2)と電気的に接触する。捕捉領域(9)は少なくとも電極間表面と対向する。  (もっと読む)

(もっと読む)

情報記録再生装置

【課題】高記録密度かつ低消費電力を実現した情報記録再生装置を提供する。

【解決手段】情報記録再生装置は、電圧パルスの印加によって所定の抵抗値を持つ第1の状態とこの第1の状態よりも高い抵抗値を持つ第2の状態との間を可逆的に遷移する記録層からなるメモリセルを備える。前記記録層は、組成式AxMyX4(0.1≦x≦1.2、2<y≦2.9)で表される第1化合物層を含む。前記Aは、Mn(マンガン)、Fe(鉄)、Co(コバルト)、Ni(ニッケル)、及びCu(銅)のグループから選択される少なくとも1種類の元素である。前記Mは、Al(アルミニウム)、Ga(ガリウム)、Ti(チタン)、Ge(ゲルマニウム)、及びSn(スズ)のグループから選択される少なくとも1種類の元素であり、かつ、前記Aとは異なる元素である。前記Xは、O(酸素)であることを特徴とする。

(もっと読む)

ナノ線メモリ

【課題】単純な構造のナノ点を有するメモリを利用してマルチレベルを保存することができるメモリ素子を提供する。

【解決手段】ソース210及びソース210と対応するドレイン220と、ソース210とドレイン220との間を連結するように形成されているナノチャンネル230とを含み、ナノチャンネル230は、ソース210及びドレイン220の電圧によってソース210とドレイン220との間を電気的に連結するナノ線と、ナノ線上に吸着されて形成され、電荷を補集する複数のポテンシャルを有するナノ点とを含む。

(もっと読む)

薄膜トランジスタを利用して不揮発性メモリとする方法およびその装置

【課題】薄膜トランジスタ(TFT)のベースを利用して電荷を保存し、不揮発性メモリとする方法を提供する。

【解決手段】薄膜トランジスタ10を利用し、そのうち薄膜トランジスタ10は中間がベース21、両端がそれぞれドレイン電極22、ソース電極23である半導体層20を備え、絶縁表面31を備えた基板30上に設置され、ゲート電極絶縁層41が前記半導体層20上に設置され、ゲート電極40がゲート電極絶縁層41上に設置され、電子がゲート電極40の電場作用下で、熱電子界放射により電子正孔対を形成し、電子正孔対がゲート電極40の垂直電場により分離され、複数のキャリア(nチャネルでいうと正孔)が薄膜トランジスタ10のベース21に注入され、薄膜トランジスタ10の閾値電圧の変化を引き起こし、書き込み動作が完了する。

(もっと読む)

半導体記憶素子

【課題】従来構造のフラッシュメモリと比べてはるかに微細化可能な、フラーレンによるダイポールを利用した半導体記憶素子を提供する。

【解決手段】半導体領域を含む第1の電極11と、第1の電極11上に形成され、膜厚方向に設けられた孔を有する絶縁膜12と、孔の開口部を覆って閉鎖された空間13を形成する金属を含む第2の電極15と、閉鎖空間13内に配置され、電圧の印加により第1または第2の電極11,15のいずれかの側に移動することにより第1の電極11と第2の電極15との間にダイポールを発生させて、フラットバンド電圧をシフトさせるフラーレン14を具備する。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】微細な構造でも安定して製造可能な不揮発性記憶装置の製造方法を提供する。

【解決手段】第1の方向に延在する第1の配線と、前記第1の方向と非平行な第2の方向に延在する第2の配線と、前記第1の配線と前記第2の配線との間に挟持され、前記第1の配線と前記第2の配線とを介して供給される電流により、第1の状態と第2の状態との間を可逆的に遷移可能な記録層と、を有する不揮発性記憶装置の製造方法であって、前記第1の配線の層を形成する工程と、前記第1の配線の層の主面上に前記記録層の層を形成する工程と、前記記録層の層と前記第1の配線の層を選択的にエッチングして、前記第1の方向に延在する複数の積層体を形成する工程と、前記複数の積層体の間隙の表面に、気相成長法を用いて第1の絶縁層を形成する工程と、前記第1の絶縁層の上に、塗布法を用いて第2の絶縁層を形成する工程と、を備えたことを特徴とする不揮発性記憶装置の製造方法を提供する。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート絶縁層の信頼性とデータ保持特性を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置100は、半導体基板Baに対して垂直方向に延びるメモリ柱状半導体層38と、メモリ柱状半導体層38の側壁側に電荷蓄積層36を介して形成された第1〜第4ワード線導電層32a〜32dと、第1〜第4ワード線導電層32a〜32dの上下に形成された第1〜第5ワード線間絶縁層31a〜31eとを備える。第1〜第4ワード線導電層32a〜32dのメモリ柱状半導体層38側の側壁は、上方から下方へと移動するに従いメモリ柱状半導体層38の中心軸から離れる方向へ傾斜するように形成されている。第1〜第5ワード線間絶縁層31a〜31eのメモリ柱状半導体層38側の側壁は、上方から下方へと移動するに従いメモリ柱状半導体層38の中心軸に近づく方向へ傾斜するように形成されている。

(もっと読む)

シリコンドット形成方法及びシリコンドット形成装置

【課題】低温で基板上に直接粒径の揃ったシリコンドットを均一な密度分布で形成する方法及び装置を提供する。

【解決手段】シリコンスパッタターゲット30と基体Sを配置したチャンバ1内に水素ガスを導入し、該ガスに高周波電力を印加してチャンバ1内に、プラズマ発光において波長288nmにおけるシリコン原子の発光強度Si(288nm) と波長484nmにおける水素原子の発光強度Hβとの比〔Si(288nm) /Hβ〕が10.0以下であるプラズマを発生させ、該プラズマでターゲット30をケミカルスパッタリングして500℃以下の低温で基体上に直接、粒径が20nm以下のシリコンドットを形成する。

(もっと読む)

情報記録再生装置

【課題】高記録密度及び低消費電力の不揮発の情報記録再生装置を提供する。

【解決手段】本発明の例に関わる情報記録再生装置は、記録層と、前記記録層に電圧を印加して前記記録層に相変化を発生させて情報を記録する手段とを具備し、前記記録層は、少なくとも、化学式1:AxMyX4 (0.1≦x≦2.2、1.5≦y≦2)で表されるスピネル構造を有する第1化合物を含むように構成されることを特徴とする。但し、Aは、Zn, Cd, Hgのグループから選択される少なくとも1種類の元素であり、Mは、Cr, Mo, W, Mn, Reのグループから選択される少なくとも1種類の遷移元素であり、Xは、Oである。

(もっと読む)

情報記録再生装置

【課題】低消費電力で、かつ、熱安定性が高い不揮発性の情報記録再生装置を提案する。

【解決手段】本発明に係る情報記録再生装置は、記録層12と、記録層12に電圧を印加して記録層12に状態変化を発生させて情報を記録する手段とを備える。記録層12は、ホランダイト構造を有する材料により構成される。

(もっと読む)

直列連結構造の抵抗ノードを有するメモリ素子

【課題】直列連結構造の抵抗ノードを有するメモリ素子を提供する。

【解決手段】第1端子N1と第2端子N1との間に印加される電圧によって可変抵抗特性を有する複数の抵抗ノード110と、一の抵抗ノード110の第1端子N1と他の抵抗ノード110の第2端子N2との間を直列に連結し、抵抗ノード110より低い抵抗を有する複数の金属プラグ120と、第1端子S、第2端子D、及び第1端子Sと第3端子Gを有する複数の制御素子140と、一の制御素子140の第1端子Sと他の制御素子140の第2端子Dとを直列的に連結するビットラインBLと、ビットラインBLと金属プラグ120との間に介在されて、ビットラインBLと金属プラグ120との間の電流フローを開閉することができる複数のスイッチ素子130と、制御素子140の第3端子Gと連結された複数のワードラインWLと、を備えることを特徴とする。

(もっと読む)

電界効果トランジスタ及びその動作方法

【課題】 ゲート容量可変の電界効果トランジスタを用いた不揮発性メモリの消費電力と読み出しエラーとを低減する。

【解決手段】 シリコン基板101上にソース領域104とドレイン領域105を形成すると共にソース領域104とドレイン領域105とに挟まれた領域上に順次、絶縁膜102a、PCMO膜102b、ゲート電極103を積層して、電界効果トランジスタ1とする。PCMO膜102bに印加する書き込み電圧の電圧値を変えることによってデータを書き込み、PCMO膜102bに読み出し電圧を印加し、ドレイン電流を検出することによってデータを読み出す。

(もっと読む)

半導体装置、及びその作製方法

【課題】不揮発性メモリにおいて、印加電圧が高いという問題があった。これは、絶縁膜を介して、フローティングゲートにキャリアをトンネル効果により注入する必要があるからである。またこのようなキャリアの注入を行うことにより、絶縁膜の劣化が懸念される。そこで印加電圧を低くし、絶縁膜の劣化を防止したメモリを提供することを課題とする。

【解決手段】メモリのフローティングゲートとして機能するものとして、電荷移動錯体を有する無機化合物、及び有機化合物が混在された層を用いることを特徴とする。具体的には、絶縁層間に挟まれた、電荷移動錯体を有する無機化合物、及び有機化合物が混在された層をフローティングゲートとして用いたトランジスタ構造を有する素子である。

(もっと読む)

1 - 15 / 15

[ Back to top ]