Fターム[5F101BA62]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | その他記憶作用 (122) | 強誘電体 (98)

Fターム[5F101BA62]に分類される特許

1 - 20 / 98

ニッケル酸ランタン膜形成用組成物及びその製造方法、ニッケル酸ランタン膜の製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、並びに液体噴射装置の製造方法

液体噴射ヘッド及び液体噴射装置並びに圧電素子

液体噴射ヘッド、液体噴射装置及び圧電素子

液体噴射ヘッド、及び液体噴射装置

【課題】環境負荷が小さく且つ新規な手法により比較的小さな電界で大きな圧電歪を得ることができる液体噴射ヘッド、及び液体噴射装置を提供する。

【解決手段】少なくともビスマス、バリウム、鉄、及びチタンを含むペロブスカイト型構造の複合酸化物からなる圧電体層70と、圧電体層70に電界を印加する電極60,80と、を具備する圧電素子300を備えた液体噴射ヘッドIであって、圧電体層70は、引張り応力により菱面晶から単斜晶へ変化しており、駆動時において、電界を印加することにより圧電体層70が単斜晶から菱面晶へ変化する。

(もっと読む)

液体噴射ヘッド及び液体噴射装置並びに圧電素子

【課題】環境負荷が小さく、歪量が大きい液体噴射ヘッド、液体噴射装置及び圧電素子を提供する。

【解決手段】圧電体層70と圧電体層70に設けられた電極60,80とを具備する圧電素子300を備え、圧電体層70は、ビスマス、鉄、バリウム及びチタンを含みペロブスカイト構造を有する複合酸化物からなり、圧電体層70に駆動電圧Vaを印加したときの変位量をZmax、その後印加電圧を0Vにしたときの変位量をZ0としたとき、(Zmax−Z0)/Vaが70pm/V以上且つ比誘電率が700以下である。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

機能性デバイスの製造方法及び機能性デバイスの製造装置

【課題】機能性デバイスの高性能化、又はそのような機能性デバイスの製造プロセスの簡素化と省エネルギー化を提供する。

【解決手段】機能性デバイスの製造方法は、型押し工程と、機能性固体材料層形成工程を含む。型押し工程では、機能性固体材料前駆体溶液を出発材とする機能性固体材料前駆体層に対して型押し構造を形成する型を押圧している間の少なくとも一部の時間においてその機能性固体材料前駆体層に対して熱を供給する熱源の第1温度がその機能性固体材料前駆体層の第2温度よりも高くなるように、その機能性固体材料前駆体層に対して型押し加工を施す。また、機能性固体材料層形成工程では、型押し工程の後、酸素含有雰囲気中において、機能性固体材料前駆体層を前述の第1温度よりも高い第3温度で熱処理することにより、機能性固体材料前駆体層から機能性固体材料層を形成する。

(もっと読む)

圧電体前駆体溶液、圧電セラミックスの製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、及び、液体噴射装置の製造方法

【課題】少なくともBi、Ba、Fe及びTiを含む圧電体層を有する圧電素子、液体噴射ヘッド及び液体噴射装置の性能を向上させることにある。

【解決手段】少なくともビスマス、バリウム、鉄及びチタンを含むペロブスカイト型酸化物を形成するための圧電体前駆体溶液は、少なくとも、ビスマス塩、バリウム塩、鉄塩、並びに、チタンの部分アルコキシド(チタンにアルコキシ基及び該アルコキシ基以外の官能基が結合したチタン化合物)を含む。圧電セラミックスの製造方法は、前記圧電体前駆体溶液を塗布する工程と、該塗布した前駆体溶液を結晶化させてペロブスカイト型酸化物を含む圧電セラミックスを形成する工程と、を備える。圧電素子の製造方法は、前記圧電セラミックスに電極を形成する工程を備える。液体噴射ヘッドの製造方法は、前記圧電素子の製造方法により圧電素子を形成する工程を備える。

(もっと読む)

圧電セラミックスの製造方法、圧電素子の製造方法、液体噴射ヘッドの製造方法、及び、液体噴射装置の製造方法

【課題】少なくともBi、Ba、Fe及びTiを含む圧電体層を有する圧電素子、液体噴射ヘッド及び液体噴射装置の性能を向上させる製造方法を提供する。

【解決手段】少なくともBi、Ba、Fe及びTiを含む前駆体溶液であって、水溶液とした場合にpHが7以上である前駆体溶液31を下電極20上に塗布し、塗布した前駆体溶液31を結晶化させてペロブスカイト型酸化物を含む圧電セラミックスを形成する。圧電素子の製造方法は、圧電セラミックス30に電極を形成する工程を備える。液体噴射ヘッドの製造方法は、圧電素子の製造方法により圧電素子を形成する工程を備える。

(もっと読む)

半導体装置

【課題】頻繁なリフレッシュ動作が不要で、正常な読み出しを行うことのできる2トランジスタ型のDRAMを備えた半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、ゲートが第1配線に接続され、第1ソース/ドレインの一方が第2配線に接続された第1トランジスタと、ゲート絶縁膜、ゲート電極、および前記ゲート絶縁膜と前記ゲート電極との間に設けられしきい値を変調するしきい値変調膜を有するゲート構造と、第2ソース/ドレインとを備え、前記ゲート電極が前記第1トランジスタの前記第1ソース/ドレインの他方に接続され、前記第2ソース/ドレインの一方が第3配線に接続され、前記第2ソース/ドレインの他方が第4配線に接続された第2トランジスタと、を備えている。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法

【課題】液体プロセスに採用し易い配向性の制御が可能な半導体装置や強誘電体素子の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ソース電極およびドレイン電極と、前記ソース電極及び前記ドレイン電極との間に配置され、チャネル部を有する有機半導体膜と、ゲート電極と、前記チャネル部と前記ゲート電極との間に配置されたゲート絶縁膜と、を有する半導体装置の製造方法であって、前記チャネル部を第1の温度に加熱する工程と、前記第1の温度の前記有機半導体膜に、前記第1の温度よりも低い第2の温度の絶縁性ポリマーを含む液滴材料を配置し一定の方向に延ばす塗工工程により前記ゲート絶縁膜を形成する工程と、を有することを特徴とする。

(もっと読む)

半導体集積回路

【課題】 不揮発記憶保持用途の電界効果トランジスタと、論理演算用途の電界効果トランジスタの製造工程を別々に設けることなく前記2用途の電界効果トランジスタを同一半導体基板上に同一構造に作製できるようにする。

【解決手段】 ゲート絶縁構造体12に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタで半導体集積回路のメモリ回路とロジック回路の両方を構成し、ゲート絶縁構造体に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタのゲート-基板領域間に印加する電圧の大きさと印加タイミングを制御することによって、論理演算状態と記憶書込み状態と不揮発記憶保持状態を電気的に切り替える。

(もっと読む)

半導体不揮発性記憶素子及びその製造方法

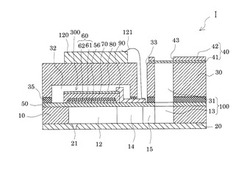

【課題】MFMIS構造の半導体不揮発性記憶装置において、メモリセル面積を大きくすることなく、効率的に強誘電体キャパシタに分配電圧を加えることができる半導体不揮発性記憶装置及びその製造方法を提供する。

【解決手段】強誘電体不揮発性記憶素子において、チャンネル領域上に第1絶縁体層(3)、第1導電体層(4)、強誘電体層(5)、及び第2導電体層(6)が順次積層された構造を持ち、ソース領域とドレイン領域上にそれぞれ積層された第3導電体(9)と第4導電体(10)を持ち、第3導電体(9)及び第4導電体(10)が、第1導電体層(4)と第2絶縁体薄膜(11)を介して対向する構造を持つ。

(もっと読む)

不揮発性半導体メモリ

【課題】新たなコンセプトに基づく不揮発性半導体メモリを提供する。

【解決手段】本開示の不揮発性半導体メモリは、半導体基板11上の半導体層12と、半導体層12を貫通する複数のコントロールゲートCG11〜CG17と、第1方向の2つの端部における半導体層12内にそれぞれ配置される2つの第1導電型拡散層14と、半導体層12上で第1方向に延びる複数のセレクトゲート線SG1〜SG5と、複数のセレクトゲート線SG1〜SG5上で第2方向に延びる複数のワード線WL1〜WL7とを備える。複数のセレクトゲート線SG1〜SG5の各々は、第1方向に並ぶ複数のコントロールゲートCG11〜CG17と複数のワード線WL1〜WL7との間に接続される複数のセレクトトランジスタに共有されるセレクトゲートとして機能する。半導体層12及び複数のコントロールゲートCG11〜CG17は、メモリセルアレイを構成する。

(もっと読む)

強誘電体材料層の製造方法、薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】強誘電体材料層の電気特性(例えば、高残留分極特性、低リーク電流特性など。)をより一層向上させることが可能な強誘電体材料層の製造方法を提供する。

【解決手段】熱処理することにより強誘電体材料となるゾルゲル溶液を準備する第1工程と、基材上に前記ゾルゲル溶液を塗布することにより、前記強誘電体材料の前駆体組成物層を形成する第2工程と、前記前駆体組成物層を120℃〜250℃の範囲内にある第1温度で乾燥させる第3工程と、前記前駆体組成物層を前記第1温度よりも高く、かつ、150℃〜300℃の範囲内にある第2温度に加熱した状態で前記前駆体組成物層に対して型押し加工を施す第4工程と、前記前駆体組成物層を前記第2温度よりも高い第3温度で熱処理することにより、前記前駆体組成物層から強誘電体材料層を形成する第5工程とをこの順序で含む強誘電体材料層の製造方法。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

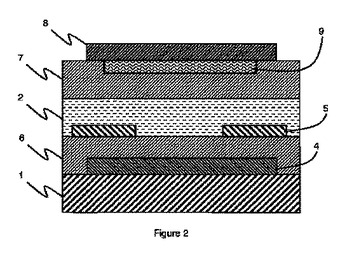

有機デュアルゲートメモリおよびその製造方法

有機メモリデバイスは、第1のゲート電極(4)と、第1のゲート誘電体(6)と、有機半導体材料(2)と、第2のゲート誘電体(7)と、第2のゲート電極(8)とを備えるデュアルゲートトランジスタである。ソース・ドレイン電極(5)が、有機半導体材料(2)中に配置されるとともに、電極間表面を規定する。捕捉領域(9)が、有機半導体材料(2)とゲート電極(4,8)のうちの一方との間に配置されるとともに、ゲート電極(4,8)のうちの一方または有機半導体材料(2)と電気的に接触する。捕捉領域(9)は少なくとも電極間表面と対向する。  (もっと読む)

(もっと読む)

1 - 20 / 98

[ Back to top ]