Fターム[5F101BC00]の内容

不揮発性半導体メモリ (42,765) | 電荷注入 (1,823)

Fターム[5F101BC00]の下位に属するFターム

トンネル注入 (746)

アバランシェ注入 (75)

高不純物濃度部形成(電荷注入部の) (25)

注入領域形成 (10)

チャンネル注入 (848)

光書込み (4)

電子ビーム書込み

その他 (112)

Fターム[5F101BC00]に分類される特許

1 - 3 / 3

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物を低減する。また、酸化物半導体膜の被形成面近傍の結晶性を向上させる。また、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

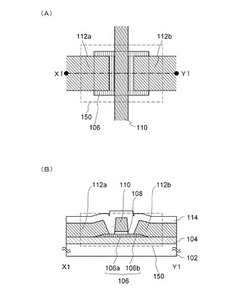

【解決手段】シリコンを含む下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも酸化物半導体膜と重畳する領域に設けられたゲート電極と、酸化物半導体膜に電気的に接続されたソース電極、及びドレイン電極と、を有し、酸化物半導体膜は、下地絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度で分布する領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】MONOS型不揮発性メモリセルの書込特性を改善する。

【解決手段】第1方向に伸び、且つ、半導体基板1を複数の素子領域に分離する素子分離絶縁膜STIと、第1方向と交差する第2方向に伸びる複数のワード線と、素子領域上に接続された複数のメモリセルを含むメモリセルストリングと、メモリセルストリングの一端に選択ゲートトランジスタを介して接続されたビット線コンタクトと、メモリセルストリングの他端に選択ゲートトランジスタを介して接続されたソース線コンタクトとを備え、メモリセル4は、半導体基板1上に形成されたトンネル絶縁膜41と、トンネル絶縁膜41上に形成され、且つ、絶縁膜を含む電荷蓄積層42と、電荷蓄積層42上に形成され、且つ、ワード線に接続されるゲート電極44とを有し、書込時に、選択ワード線に隣接する第1及び第2隣接ワード線のうち、第1隣接ワード線に、パス電圧より大きい補助電圧が印加される。

(もっと読む)

ゲートによるジャンクションリーク電流を使用してフラッシュメモリをプログラミングする技術

メモリ素子をプログラムする方法と、ゲートによる接合リーク電流を利用してプログラムされたメモリ素子を提供する。本素子は、基板上のフローティングゲートと、基板内の活性領域と、フローティングゲートに隣接する第2ゲートを少なくとも含むことができる。本方法は、第1ゲートにバイアスをか印加することによってフローティングゲートの下の基板内に反転領域を生成する工程と、第2ゲートの付近に臨界電界を生成する工程を含むことができる。臨界電界を生成する工程は、活性領域に第1ポジティブバイアスを印加する工程と、第2ゲートに第1ポジティブバイアスより小さいバイアスを印加する工程を含むことができる。本素子は、活性領域に印加されるゼロボルトより大きい第1バイアスと、第2ゲートに印加される第1バイアスより大きい第2バイアスをさらに含む。第1バイアスと第3バイアスは、フローティングゲートと選択ゲートの間において基板内にリーク電流を生成するために選択される。  (もっと読む)

(もっと読む)

1 - 3 / 3

[ Back to top ]