Fターム[5F101BC01]の内容

不揮発性半導体メモリ (42,765) | 電荷注入 (1,823) | トンネル注入 (746)

Fターム[5F101BC01]の下位に属するFターム

ファウラーノルトハイム・トンネル注入 (566)

突起、電界集中 (26)

Fターム[5F101BC01]に分類される特許

1 - 20 / 154

メモリ装置

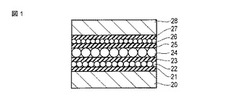

【課題】配線電極間の双方向の電流値、書き込み及び消去の電圧値、および記憶保持時間が制御容易なメモリ装置を提供する。

【解決手段】微結晶である第1の導電性微粒子を含む微結晶層22と、微結晶層22を挟むトンネル絶縁膜21、23とを有する第1の二重トンネル接合構造と、微結晶である第2の導電性微粒子を含む微結晶層26と、微結晶層26を挟むトンネル絶縁膜25、27とを有する第2の二重トンネル接合構造と、第1の二重トンネル接合構造と第2の二重トンネル接合構造との間に配置され、情報電荷を蓄積する電荷蓄積層と、第1の二重トンネル接合構造、電荷蓄積層、及び第2の二重トンネル接合構造を挟む第1、第2の導電層とを備える。第1の導電性微粒子の平均粒径は、第2の導電性微粒子の平均粒径と異なっている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法とデータ書き換え方法

【課題】データ保持時間を、マスクROMと同様の無限大とすることができる、長期にわたりデータを保持できる信頼性の高いEEPROMを提供する。

【解決手段】不揮発性半導体記憶装置は、所定のセンスレベルに対して熱平衡状態しきい値電圧が正方向である第1の不揮発性半導体記憶素子100に正のデータを記憶し、熱平衡状態しきい値電圧が負方向である第2の不揮発性半導体記憶素子200に負のデータを記憶することでデータ保持時間を無限大にする。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

アプリケーション回路及び半導体デバイスの動作方法

【課題】バッテリレス電子タイマに適用される半導体デバイス、及びその動作方法とアプリケーション回路を提供する。

【解決手段】半導体デバイス600は、第1導電型半導体基板と、ゲート誘電層と、フローティングゲート606と、第2導電型ウェル608と、第1導電型ウェル610と、第2導電型ソース拡散層612と、第2導電型ドレイン拡散層614と、第2導電型制御ゲート拡散層616と、を含む。制御ゲート拡散層616、ソース拡散層612及びドレイン614の間の漏れ電流が二重のウェル領域上に印加されるバイアスを調節することにより減少される。

(もっと読む)

半導体記憶装置

【課題】高性能な乱数を生成することができ、予測困難性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルMCが配置されるメモリセルアレイ11と、乱数(Random number)を発生させる乱数発生回路16と、メモリセルアレイ11および乱数発生回路16を制御するコントローラ19とを少なくとも具備する。乱数発生回路16は、生成した制御パラメータ(Read voltage parameter)によりメモリセルMCを読み出した結果にもとづく乱数パラメータ(PRESET)を生成する乱数制御回路162と、乱数パラメータ(PRESET)をシード値として用いて乱数(Random number)を発生させる擬似乱数生成回路161とを備える。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】従来のMONOS型の不揮発性半導体記憶装置の製造方法では、トップ絶縁膜のエッチング加工にウェットエッチングを用いるため、サイドエッチングが侵攻してしまうという問題があった。これにより電荷蓄積層とゲート電極との間の絶縁性が損なわれ、電気的リークが発生し、消去特性などの電気特性が低下していた。

【解決手段】本発明の不揮発性半導体記憶装置の製造方法は、2つの犠牲膜を用いることにより、トップ絶縁膜と側壁保護膜とを同時に形成するエリアを作り出し、酸化処理によってそれらを形成する。このような製造方法とすることで、メモリゲート絶縁膜のサイドエッチングが発生することはない。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】従来のMONOS型の不揮発性半導体記憶装置の製造方法では、トップ絶縁膜のエッチング加工にウェットエッチングを用いるため、サイドエッチングが侵攻してしまうという問題があった。これにより電荷蓄積層とゲート電極との間の絶縁性が損なわれ、電気的リークが発生し、消去特性などの電気特性が低下していた。

【解決手段】メモリゲート絶縁膜の形成前に保護絶縁膜を形成し、この保護絶縁膜によりメモリゲート絶縁膜のサイドエッチングを防止する製造方法とすることで、電荷蓄積層とゲート電極との間の絶縁性が向上する。そして、この保護絶縁膜を不揮発性半導体記憶装置の製造後も側壁保護膜として残してもよい。そうすると不揮発性半導体記憶装置の完成後に、他の半導体素子を形成するためのウェットエッチング工程があったとしても、メモリゲート絶縁膜がサイドエッチングされることはない。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域とフローティングゲート電極との間には、膜厚の異なる複数のトンネル絶縁膜を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域のエッジ近傍のトンネル絶縁膜上には、トンネル絶縁膜とは異なる材質の絶縁膜からなる電界緩和層を配置した。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】下部電極、上部電極およびそれらの間の絶縁膜により構成される容量素子の下部電極および上部電極間の耐圧を向上させる。

【解決手段】上部電極TEならびに上部電極TEのそれぞれの側壁の側壁酸化膜9およびサイドウォール10と下部電極BEとの間にONO膜IFを連続的に形成し、また、上部電極TEの側壁に、側壁酸化膜9を介して真性半導体膜からなるサイドウォール10を形成することにより、下部電極BEおよび上部電極TE間にリーク電流が発生することを防ぐ。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】書き込み特性の向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板10上に、トンネル絶縁膜11を形成し、前記トンネル絶縁膜上に、導電体で構成される電荷蓄積層12を形成し、前記電荷蓄積層、前記トンネル絶縁膜、および前記基板を加工して、前記基板内に、前記電荷蓄積層および前記トンネル絶縁膜を分離する素子分離溝22を形成し、前記素子分離溝内に、上面が前記電荷蓄積層の下面より高く上面より低くなるように素子分離絶縁膜13を埋め込み、前記電荷蓄積層の表面に形成された自然酸化膜30を除去し、前記素子分離絶縁膜および前記電荷蓄積層の表面に、絶縁膜14を形成し、前記自然酸化膜の除去から前記絶縁膜の形成までが、その内部の酸素濃度がコントロールされた製造装置内で行われる。

(もっと読む)

不揮発性半導体記憶装置およびその制御方法

【課題】高速で高信頼動作できるようにした不揮発性半導体記憶装置およびその制御方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセル、および、前記第1のメモリセルに対し第1方向に隣接して配置された第2のメモリセルを備えたセル群と、書込回路とを備え、第1および第2のメモリセルの一方をデータ記憶保持に、他方を一方の閾値調整に用い、書込回路が、セル群の前記第1のメモリセルにデータを書込むときには、セル群の第2のメモリセルに電圧を印加し、セル群の第1のメモリセルの閾値電圧を所望の第1閾値電圧より高く調整する。

(もっと読む)

半導体装置及びその製造方法

【課題】デバイス特性及びプロセスのばらつきを低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10と、下部ゲート層BGと、積層体と、ダミー電極層DWLと、絶縁膜30と、チャネルボディ20,45とを備えた。下部ゲート層BGは、基板10上に設けられた。積層体は、下部ゲート層BG上にそれぞれ交互に積層された複数の絶縁層と複数の電極層WLとを有する。ダミー電極層DWLは、下部ゲート層BGと積層体との間に設けられ、電極層WLと同じ材料からなり、各々の電極層WLよりも厚い。絶縁膜30は、積層体及びダミー電極層を貫通して形成されたホールMHの側壁に設けられた電荷蓄積膜を含む。チャネルボディ20,45は、ホールMH内における絶縁膜30の内側に設けられた。

(もっと読む)

不揮発性半導体記憶装置

【課題】生産性及び動作安定性の向上を可能とする不揮発性半導体記憶装置を提供する。

【解決手段】交互に積層された複数の電極膜14及び絶縁膜を含み、X軸方向に延在する第1、第2積層構造体Sa1、Sa2と、これらに積層された第1、第2選択ゲート電極SGa1、SGa2と、これらのそれぞれを貫通し、下端が接続された第1、第2半導体ピラーSPa1、SPa2と、電極膜14と記憶層と、X軸方向と交差する第1、第2配線LL1、LL2と、交互に積層された複数の電極膜14及び絶縁膜を含む積層構造体Sbと、それに積層された選択ゲート電極SGbと、これらを貫通し下端が接続された第1及び第2選択部半導体ピラーSPb1,SPb2と、第4方向に延在する第3、第4配線LL3,LL4と、第4配線LL4は第2配線LL2に接続され、第3配線LL3の上に設けられ第3配線L3に接続された第5配線LL5と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去特性の変動が小さく、特性の安定した不揮発性半導体記憶装置を実現する。

【解決手段】不揮発性半導体記憶装置50は、第1導電型の半導体基板1上にゲート電極6bを有し第2導電型のMISFET5と、半導体基板1上の第2導電型第1ウェル3に設けられ、第1容量電極6cを有する第1MISキャパシタ15と、半導体基板1上の第2導電型第2ウェル4に設けられ、第2容量電極6aを有する第2MISキャパシタ21とを備える。ゲート電極6b、第1容量電極6c、第2容量電極6aが電気的に接続されてフローティングゲート6を構成する。第2MISキャパシタ21にて、第2ウェル4と、第2ウェル4上の部分の第2容量電極6aとがキャパシタ領域を構成する。第2容量電極6aは、キャパシタ領域が複数の分割キャパシタ領域に分割され、各分割キャパシタ領域の面積が変動してもその総面積は略一定となる平面形状及び配置を有する。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の駆動方法

【課題】隣接セル間の干渉の影響を抑制し、データリテンション特性の向上を図ること。

【解決手段】本発明は、メモリ部と、制御部と、を備え、制御部は、複数の記憶領域MEの全てに消去の情報を設定し、メモリセルトランジスタTrの全てについて消去の閾値に設定した後、記憶領域MEにn(nは2以上の整数)値の情報を書き込み、記憶領域MEに設けられたメモリセルトランジスタTrをn値の情報に応じた閾値に設定した状態で、情報の書き込み済みの記憶領域MEに隣接する少なくとも1つの書き込み前の記憶領域MEの情報が、メモリセルトランジスタTrの閾値として、消去の閾値よりも、n値の情報に応じた閾値に近い値になるよう制御する。

(もっと読む)

1 - 20 / 154

[ Back to top ]