Fターム[5F101BD01]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677)

Fターム[5F101BD01]の下位に属するFターム

MOSトランジスタ (3,641)

MOSトランジスタ以外のセンサ (25)

Fターム[5F101BD01]に分類される特許

1 - 11 / 11

半導体装置の製造方法

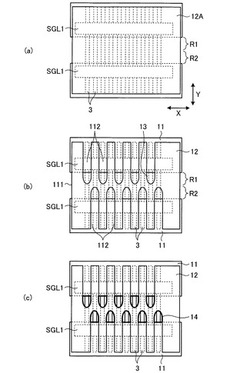

【課題】ホールパターンの寸法のばらつきを抑え、ホールパターンの未開口の発生を抑制する半導体装置の製造方法を提供する。

【解決手段】一つの実施形態によれば、半導体装置の製造方法は、第1と第2のレジストパターン形成工程を含む。第1のレジストパターン形成工程では、コンタクトホール形成領域に、開口パターン111を有する第1のレジストパターン11を形成する。第2のレジストパターン形成工程では、コンタクトホール形成領域の第1の領域R1に開口パターン112を有し、第2の領域R2に第3の開口パターン112を有する第2のレジストパターン12を形成する。第2と第3の開口パターン112は、1本おきの活性領域3上に配列した形状を有するが、互いに異なる活性領域3上に形成される。そして、先に行う第1または第2のレジストパターン形成工程では、後のリソグラフィ処理で耐性を有するレジストの不溶化処理が行われる。

(もっと読む)

記憶装置

【課題】ロジック回路を増やすことなく、第三者がメモリセルにアクセスできずかつ必要な場合にはいつでもアクセス可能なメモリセルを有する記憶装置を提供する。

【解決手段】本実施形態は、第1のメモリセルと、第2のメモリセルと、を有し、第2のメモリセルに設けられた第2のトランジスタの第2のチャネルが酸化物半導体膜からなる記憶装置であって、第2のメモリセルからのデータの読み出しは第2のトランジスタに紫外線を照射している時に行われる記憶装置によって解決する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】不揮発性半導体記憶装置を構成するメモリセルの縮小化および高密度化を実現することにより、製品となる不揮発性半導体記憶装置のさらなる小型化を達成できる技術を提供する。

【解決手段】メモリセルMC1とメモリセルMC2の間に自己整合的にソース配線SLを形成する。具体的には、メモリゲート電極MG1の側壁に形成されているサイドウォールSWと、メモリゲート電極MG2の側壁に形成されているサイドウォールSWの両方に自己整合的に接触するようにソース配線SLを形成する。さらに、メモリゲート電極MG1、MG2、MGだけでなく、コントロールゲート電極CG1、CG2、CGもサイドウォール形状にする。

(もっと読む)

メモリデバイス

【課題】書込、読み出し、消去時間を改善した、トンネル障壁構造を有するメモリデバイスを提供する。

【解決手段】メモリデバイスは、制御電極9からトンネル障壁構造2を通り抜けて電荷を書き込むメモリノード1を有する。この蓄積された電荷はソース/ドレイン経路4の伝導性に影響を与え、この経路の伝導性をモニターすることによりデータが読み出せる。電荷障壁構造は多重トンネル障壁構造により構成される。この障壁構造は、メモリノードを形成するシリコンの多結晶層1を被覆する、厚さ3nmのポリシリコン層16と厚さ1nmのSi3N4層15を交互に積層したものからなる。ショットキ障壁構造、および電気絶縁マトリクス内に分散された、メモリノードとして機能する伝導性のナノスケール伝導島30,36,44を含む他の障壁構造2も開示されている。

(もっと読む)

半導体記憶装置

【課題】不揮発性半導体メモリのソース拡散層とデジット拡散層との間の面積を小さくする

【解決手段】コントロールゲート(2)とフローティングゲート(5)とを有する複数のメモリセル(21)と、前記複数のメモリセル(21)の上層に配置され、デジット電位コンタクト(4)を介して前記メモリセル(21)にデジット電位を供給するデジット線群(3)と、前記デジット線群(3)に平行に構成された電源線(10)と、前記フローティングゲート(5)と同層に構成され、電源供給コンタクト(8)を介して前記電源線(10)から供給される電源電位を前記複数のメモリセル(21)の電源端(11)に提供する導電部(12)とを具備する半導体記憶装置を構成する。

(もっと読む)

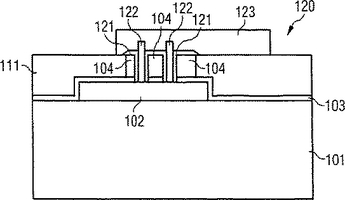

電子装置、電子装置の製造方法、電子回路及び電子機器

【課題】 特性を安定にでき、製造コストが安価で、高集積化を行い易く、また、効果的に消費電力の低減を行うことができる電子装置とその製造方法を提供すること。

【解決手段】 電子装置は、絶縁体101の中に、金属で形成された第1領域102及び第2領域103と、この第1領域102と第2領域103で挟まれた第3領域104を備える。この第3領域は、第1及び第2領域102,103を形成する金属元素と同じ金属元素で形成されて、直径が20nm以下の微粒子を有する。第1領域102及び第2領域103は、第3領域104よりも、金属濃度が高くて電気抵抗が小さい。第1領域102と第2領域103とに電圧が印加されて、第3領域104を単一の電荷がトンネルする。第1領域102と、第2領域103と、第3領域104とは、互いに同じ金属元素を含むので、互いの境界に形成される障壁を安定にできる。

(もっと読む)

スイッチング素子としてトランジスタ及びダイオードを含むハイブリッドタイプの不揮発性メモリ素子

【課題】スイッチング素子としてトランジスタ及びダイオードを含むハイブリッドタイプの不揮発性メモリ素子を提供する。

【解決手段】ソース、ドレイン及び制御ゲートを備えるトランジスタを備える。第1ストレージノードは、トランジスタにカップリングされ、電荷を保存できる。第1ワードラインは、トランジスタの制御ゲートに連結される。第1ビットラインは、トランジスタのドレインに連結される。ダイオードの一端は、トランジスタのソースに連結される。第2ストレージノードは、ダイオードの他端に連結され、抵抗変化を保存できる。第2ビットラインは、第2ストレージノードに連結される。そして第2ワードラインは、トランジスタのソースに連結される。

(もっと読む)

不揮発性半導体記憶装置

【課題】エンデュランスやディスターブ等の故障モードによって引き起こされる可能性のある重大な事故や損害を未然に防止するための手段が講じられた不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルトランジスタMCに記憶されたデータの読み出しに用いる第1のセンスアンプ10に加え、セル電流Icの状態を詳しく調べるために、第2,第3のセンスアンプ20,30を設ける。第2のセンスアンプ20は、セル電流Icと第1の基準電流Iref1よりも大きい第2の基準電流Iref2とを比較する。また、第3のセンスアンプ30では、第1の基準電流Iref1よりも小さい第3の基準電流Iref3とを比較する。そして、各出力信号に基づいて、第1のセンスアンプ10の出力信号の信頼度を判定する。その判定結果から、メモリセルトランジスタMCに故障モードが発生しているか否かを判定する。

(もっと読む)

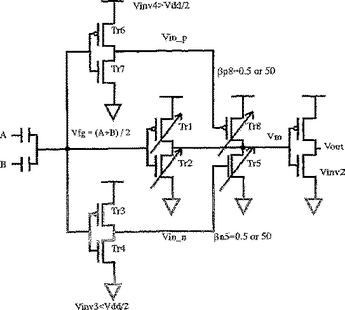

スピン依存伝達特性を有するトランジスタを用いた再構成可能な論理回路

不揮発に再構成可能な論理回路を構成する。スピンMOSFETを用いたCMOS構成による再構成可能な論理回路である。スピンMOSFETであるTr1、Tr2、Tr5、Tr8の磁化状態によりそれぞれのトランジスタの伝達特性を変化させることでAND/OR/XOR/NAND/NOR/XNOR/“1”/“0”の全2入力対称関数が再構成可能である。不揮発かつ少素子数で論理機能を構成できるため、チップ面積の縮小化が可能であり、高速・低消費電力動作が期待できる。  (もっと読む)

(もっと読む)

適応型負性微分抵抗デバイス

【課題】 単一のシリコンウェーハ中に形成した互いに異なる回路に多様な負性微分抵抗(NDR)特性を付与できるように製造工程中または出荷後のフィールドでの通常動作中に最大電流対最小電流比(PVR)値などの特性値を調整できるようにしたNDRデバイスを提供する。

【解決手段】 互いに異なるNDRモードを発現するように動作中に多様にNDR特性を変える過程を含むNDR素子の制御の方法を開示している。NDR素子(シリコン利用のNDR FETなど)に印加するバイアスの条件を変えることによって、最大電流対最小電流比(PVR)値(またはそれ以外の特性)をNDR素子利用回路の所望の動作変化の実現のために動的に変えることができる。例えば、メモリ用または論理回路用では、動作電力の削減のために最小電流値を休止期間中に小さくすることができる。すなわち、適応型NDR素子を慣用の半導体回路の中で有利に活用することができる。

(もっと読む)

不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法

本発明は、不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法に関するものである。不揮発性メモリーセルは、チャネル領域として設計されたナノ素子を有する垂直電界効果トランジスタと、ナノ素子を少なくとも部分的に取り囲む、電荷蓄積層として、および、ゲート絶縁層としての電気絶縁層とを備えている。この電気絶縁層は、電気的な電荷担体をその内部に選択的に注入でき、または、その内部から除去できるように設計されており、電気絶縁層に注入された電気的な電荷担体によって、ナノ素子の導電性に特徴的に影響を及ぼすように設計されている。  (もっと読む)

(もっと読む)

1 - 11 / 11

[ Back to top ]