Fターム[5F101BD03]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | SD領域 (1,220)

Fターム[5F101BD03]の下位に属するFターム

S・D平面形状 (20)

S・D断面形状 (141)

S・D深さ (34)

LDD等高耐圧構造(メモリセルの) (599)

不純物ドープ、不純物濃度分布(SDの) (71)

ソースドレイン共用又は入れ替え (269)

Fターム[5F101BD03]に分類される特許

1 - 20 / 86

半導体装置およびその作製方法

【課題】酸化物半導体膜の水素濃度および酸素欠損を低減する。また、酸化物半導体膜を用いたトランジスタを有する半導体装置の信頼性を向上させる。

【解決手段】下地絶縁膜と下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜に重畳して設けられたゲート電極と、を有し、下地絶縁膜は、電子スピン共鳴にてg値が2.01で信号を表し、酸化物半導体膜は、電子スピン共鳴にてg値が1.93で信号を表さない半導体装置である。

(もっと読む)

半導体記憶装置

【課題】チャネル領域にソース領域及びドレイン領域を形成せずに、信頼性が高い動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、第1の方向に延びる同一導電形のチャネル領域と、チャネル領域上に設けられた第1の絶縁膜と、第1の絶縁膜上に設けられた複数の浮遊ゲートと、浮遊ゲートの上に設けられた第2の絶縁膜と、第2の絶縁膜の上に設けられた制御ゲートとを備えている。複数の浮遊ゲートは第1の方向及びこれに交差する第2の方向に分断されている。制御ゲートは第1の方向に対して交差する第2の方向に延びている。浮遊ゲートのフリンジ電界によって、第1の方向で隣り合う浮遊ゲート間の下のチャネル領域の表面に反転層が形成される。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

半導体不揮発性メモリ装置

【課題】トンネル絶縁膜にエッジ部があることによるトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部から離間した位置に、電荷受け渡し用電極を配置し、電荷受け渡し用電極とフローティングゲート電極とが、電気的に接続されるようにした。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化された不揮発性半導体記憶装置で、隣接セル間の寄生容量によるセル間干渉とトランジスタ特性の劣化を従来に比して抑制する。

【解決手段】チャネル半導体上にゲート誘電体膜21、フローティングゲート電極22、トンネル誘電体膜23および制御ゲート電極24が順に積層され、フローティングゲート電極22と制御ゲート電極24は、トンネル誘電体膜23側に曲率を有する尖端部25,26を有する。また、トンネル誘電体膜23のキャパシタンスがゲート誘電体膜21のキャパシタンスと同等以下となるようにトンネル誘電体膜23とゲート誘電体膜21の厚さが調整される。さらに、制御ゲート電極24の尖端部26からフローティングゲート電極22に電子を注入する処理と、フローティングゲート電極22の尖端部26から制御ゲート電極24に電子を抜き取る処理とを、チャネル半導体と制御ゲート電極24との間に印加される電圧によって制御する。

(もっと読む)

不揮発性半導体記憶装置

【課題】NAND型フラッシュメモリにおいて、微細化にともなうソース領域およびドレイン領域の導通を回避できるようにする。

【解決手段】たとえば、p型ウェル12の少なくとも表面領域のボロン濃度が1E15cm-3以下となるように設定する。また、そのp型ウェル12の表面部に、ソース領域およびドレイン領域を有さず、トンネル酸化膜21を介して設けられた浮遊ゲートFGと、この浮遊ゲートFG上に絶縁膜22を介して設けられたワード線WLとなる制御ゲートCGとを有するゲート電極を備える、複数のフラッシュメモリセルMCnを設けてなる構成とされている。

(もっと読む)

半導体装置の製造方法

【課題】ウエハの設置状態にかかわらず、ドレイン領域およびソース領域をゲート電極に対して対称に形成することにより、単一セルにおける電流の対称性を確保する。

【解決手段】

半導体基板上にゲート酸化膜を形成する。ゲート酸化膜上にゲート電極を形成する。半導体基板の表面のゲート電極を挟む位置にドレイン領域およびソース領域を形成する。ドレイン領域およびソース領域を形成する工程は、半導体基板をイオン注入装置の搭載ステージ上に載置して、ゲート電極をマスクとして半導体基板の表面に不純物イオンを注入する第1のイオン注入工程と、搭載ステージの載置面内において、半導体基板を搭載ステージに対して180°回転させた向きに搭載ステージ上に再載置して、ゲート電極をマスクとして半導体基板の表面に不純物イオンを注入する第2のイオン注入工程と、を含む。

(もっと読む)

不揮発性半導体メモリ

【課題】メモリセルを可及的に小さくできるとともにセル単位で書き込み消去が可能な不揮発性半導体メモリを提供する。

【解決手段】NAND列であって、絶縁膜11上の半導体領域と、ソース/ドレイン領域14a、14bと、チャネル領域12と、電荷をトラップできる電荷トラップ膜20と、磁化の向きが固定された第1のハーフメタル強磁性金属からなるソース/ドレイン電極401とを有し、各電荷トラップ膜上に設けられ、第2のハーフメタル強磁性金属からなるゲート電極30a1、30a2であって、前記ゲート電極は、磁化の向きが前記ソース/ドレイン電極の磁化の向きに略平行な第1の領域と、磁化の向きが略反平行な第2領域から構成され、前記第1の領域が、前記ゲート電極に電流を印加することにより、前記電荷トラップ膜上から前記絶縁膜上へ、及び前記絶縁膜上から前記電荷トラップ膜上へと、可逆的に移動可能となっているゲート電極と、を備える。

(もっと読む)

強誘電体ゲート有機電界効果トランジスタ、それを用いたメモリ素子及び強誘電体ゲート有機電界効果トランジスタの製造方法

【課題】強誘電体膜及びゲート電極間のリーク電流値を低減させると共に耐絶縁性を向上させる。

【解決手段】Si基板1と、Si基板1上に少なくともHfSiON膜2、強誘電体膜3HfSiON膜4及びC60膜6が、この順で積層されたゲート構造を有しており、強誘電体膜3の、HfSiON膜4と接する側の表面におけるRa値とRms値との和の第1絶対値が、HfSiON膜4の膜厚以下であり、かつ、HfSiON膜4の、C60膜6と接している側の表面におけるRa値とRms値との和の第2絶対値が3.0nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性メモリを有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に順に形成したメモリゲート絶縁膜MI1およびメモリゲート電極MG1を覆うようにして、第1保護膜pt1を形成する。その後、メモリゲート電極MG1の側方下部の主面s1にイオン注入dp01を施してn型イオン注入領域n1を形成する。続いて、熱処理によってn型イオン注入領域n1を拡散および活性化させることで、n型メモリエクステンション領域を形成する。イオン注入dp01では、メモリゲート電極MG1およびその側壁に形成した第1保護膜pt1がイオン注入マスクとなり、メモリゲート電極MG1から、第1保護膜pt1の厚さ分だけ離れた位置に、n型イオン注入領域n1を形成する。

(もっと読む)

半導体記憶装置

【課題】高集積化することができるチャージトラップ型フラッシュ構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置70には、半導体基板1の第1主面(表面)にゲート絶縁膜2、電荷蓄積膜3、高誘電率絶縁膜4、ゲート電極膜5、及び絶縁膜6が積層形成される。高誘電率絶縁膜4は、底部が上部より広い台形形状を有する。ゲート電極膜5及び絶縁膜6は、高誘電率絶縁膜4の底部端よりも内側に形成される。メモリセルトランジスタMTRのゲート長とメモリセルトランジスタMTRのゲート間は60nm以下に形成される。メモリセルトランジスタMTRのゲート間にはソース或いはドレインが設けられず、メモリセルトランジスタMTRの書き込み動作及び読み出し動作時では、発生する反転層31がソース或いはドレインの代わりをする。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルの微細化を図ること。

【解決手段】本発明は、半導体基板10上に電荷蓄積層14、第1導電層20、及びパターン化した第1マスク層22を順次形成する工程と、第1マスク層間の中央部に開口部30を有するように、第1マスク層の側壁に第2マスク層28を形成する工程と、開口部に第2導電層32を形成する工程と、第2導電層の表面に第3マスク層34を形成する工程と、第2マスク層と第3マスク層とをマスクにエッチングを行い、第1溝部36を形成し、第1溝部間に第1導電層からなるゲート電極38を形成する工程と、半導体基板内に第1溝部で画定される拡散領域40を形成する工程と、第1溝部に第1絶縁膜42を形成し、第2マスク層と第1絶縁膜とをマスクにエッチングを行い、第2溝部44を形成し、第2溝部により電荷蓄積層を分離させる工程と、第2溝部に第2絶縁膜を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体記憶装置

【課題】大容量化、低電圧化を図ることが可能な半導体記憶装置を提供する。

【解決手段】半導体基板1の表面層のチャネル領域4の両側に、ソース2及びドレイン3が形成されている。半導体基板1のチャネル領域4上に、トンネル絶縁膜5が形成されている。トンネル絶縁膜5の上に、フローティングゲート電極6が、ソース2及びドレイン3のいずれにも重ならないように配置されている。フローティングゲート電極6を覆うように、チャネル領域4の上方にゲート絶縁膜7が形成されている。ゲート絶縁膜7の上に、ソース2及びドレイン3に接するかまたは部分的に重なるようにコントロールゲート電極8が配置されている。フローティングゲート電極6に電荷が注入された状態において、チャネル領域4とコントロールゲート電極8との間に外部から電圧を印加しない状態のときに、フローティングゲート電極6のフェルミ準位がチャネル領域の禁制帯の中に位置する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】ドレインディスターブ特性が満足でき、電子注入状態における電流の低下が抑制される半導体記憶装置の提供。

【解決手段】溝24を有するP型半導体基板2と、P型半導体基板2の溝24を有しない部分の表面に形成されたソース側N−拡散層44S、N+拡散層42S、ドレイン側N−拡散層44D、N+拡散層42Dと、溝24の側壁部、底部、N−拡散層44S、44D、N+拡散層42S、42Dの表面を覆うゲート酸化膜12と、溝24を埋め込むようゲート酸化膜12の表面に形成され、溝24が連続する方向に格子状に形成されたゲート電極14と、溝24の側壁部の表面のうち、少なくともゲート酸化膜12を介してN−拡散層44S、44Dと対向する領域に形成され、ゲート電極14との間に酸化膜12を介してスペーサ状に形成された窒化膜8と、ゲート電極14と直接接するように形成されたゲート裏打ち配線10と、を備える半導体記憶装置。

(もっと読む)

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】注入効率が高いソースサイドインジェクションによる電荷注入が可能で、標準的なCMOSプロセス工程内で基板上に実装可能な不揮発性半導体記憶装置を提供する。

【解決手段】第2不純物拡散領域7と第3不純物拡散領域8と第2ゲート電極14を有する選択トランジスタ2と、第1不純物拡散領域6と第3不純物拡散領域8と第1ゲート電極13を有するメモリトランジスタ3と、第4不純物拡散領域9に形成された第5不純物拡散領域10と第3ゲート電極17を有するMOSキャパシタ4を備え、第1ゲート電極13と第3ゲート電極17を電気的に接続してフローティングゲートFGとし、第4不純物拡散領域9と第5不純物拡散領域10を制御ゲートCGとし、第2ゲート電極14を選択ゲートとしてメモリセル1を構成し、第3不純物拡散領域8の不純物密度を第1及び第2不純物拡散領域6、7より低く5×1012ions/cm2以下に設定する。

(もっと読む)

半導体装置およびその製造方法

【課題】オフリーク電流が少なく、且つ良好なデータ書き込み特性を有するセルトランジ

スタを備えた半導体装置およびその製造方を提供する。

【解決手段】半導体基板11と、半導体基板11の主面に、第1ゲート絶縁膜12を介し

て形成された第1ゲート電極13と、第1ゲート電極13上に第2ゲート絶縁膜16を介

して形成され、ソース領域側に歪んだ形状を有する第2ゲート電極17と、第2ゲート電

極17上に形成され、ソース領域側がドレイン領域側より第2ゲート電極17側に厚いシ

リサイド膜18と、第1ゲート電極13と、第2ゲート電極17と、シリサイド膜18の

側壁に形成された酸化膜21と、第1ゲート電極13からオフセットしたソース不純物拡

散層19と、第1ゲート電極13にオーバラップしたドレイン不純物拡散層20と、を具

備する。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置

【課題】通常のC−MOSFET回路との整合性、混載可能性を保ちつつ安定した動作で、不揮発な再構成可能論理回路を構築することが可能なスピンMOSFETを備えた半導体装置を提供することを可能にする。

【解決手段】半導体基板と、半導体基板に離間して形成された第1ソース領域12および第1ドレイン領域14と、第1ソース領域と第1ドレイン領域との間に設けられる第1チャネル領域と、第1チャネル領域上に形成された第1ゲート絶縁膜と、ゲート絶縁膜上に形成された第1ゲート電極18と、第1ソース領域上に形成され第1方向に磁化容易軸を有する強磁性層を含む第1ソース電極Ms1と、第1ドレイン領域上に形成され第1方向に対して0度より大きく180度未満の角度をなす第2方向に磁化した強磁性層を含む第1ドレイン電極Md1と、第1ドレイン領域上に第1ドレイン電極と離間して形成され第2方向と略反平行な方向に磁化した強磁性層を含む第2ドレイン電極Md2と、を備えている。

(もっと読む)

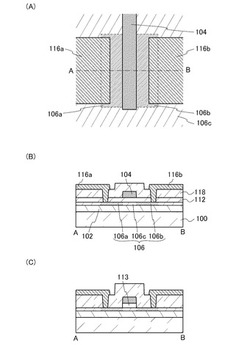

フラッシュメモリ及びその製造方法

【課題】30nm以下の微細化に適応できるフラッシュメモリ及びその製造方法を提供する。

【解決手段】基板101に接続された上部にスペーサ絶縁膜116を有するフィン構造のビットラインから形成されたメモリセル部の最小加工寸法をFとするとき、独立に書き込み/消去可能なビットライン2本が対になって4F周期に配置されてメモリセル部が形成され、一対のフィンの上部を覆うように記憶絶縁膜が形成されている。

(もっと読む)

1 - 20 / 86

[ Back to top ]